4.10 多功能寄存器(MPR)

4.10.1 使用MPR的DQ训练

DDR4 SDRAM包含了4个8bit的MPR寄存器用来存储DQ数据。这些一次性编程的寄存器可通过MRS命令来激活。在DQ总线连接性训练过程中可使用MPR所存储的数据位。在MPR使能模式下,DDR4 SDRAM仅支持如下命令:MRS, RD, RDA WR, WRA, DES, REF与RESET。

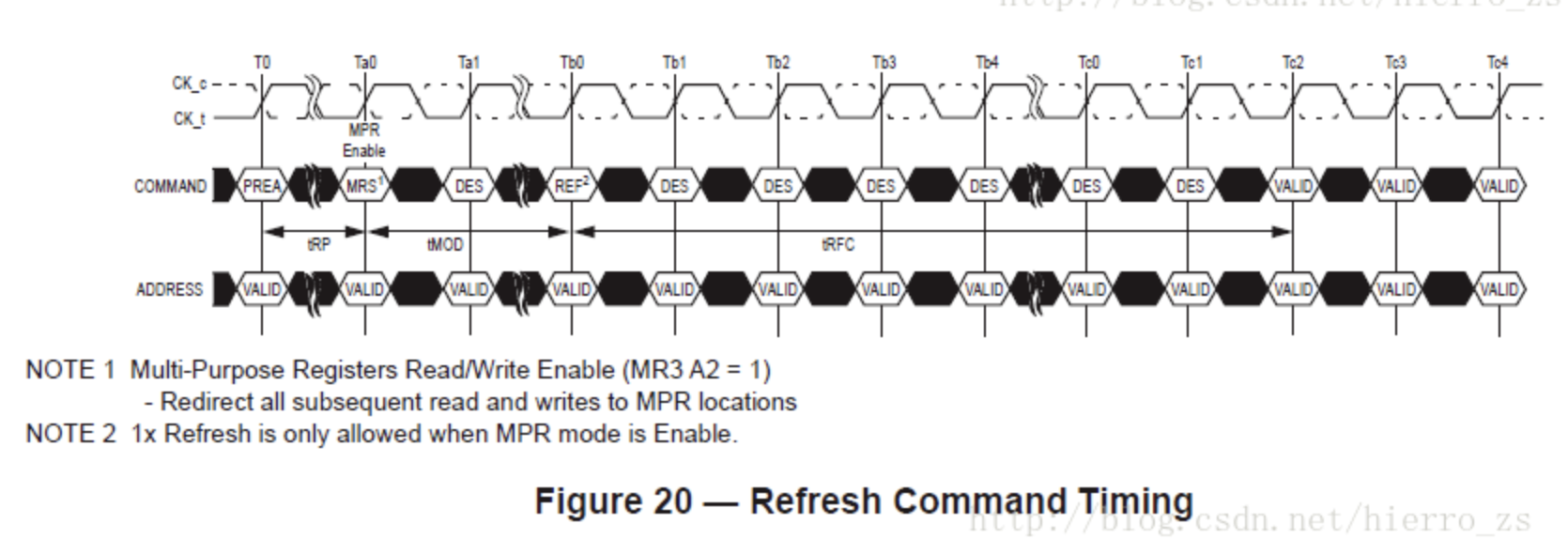

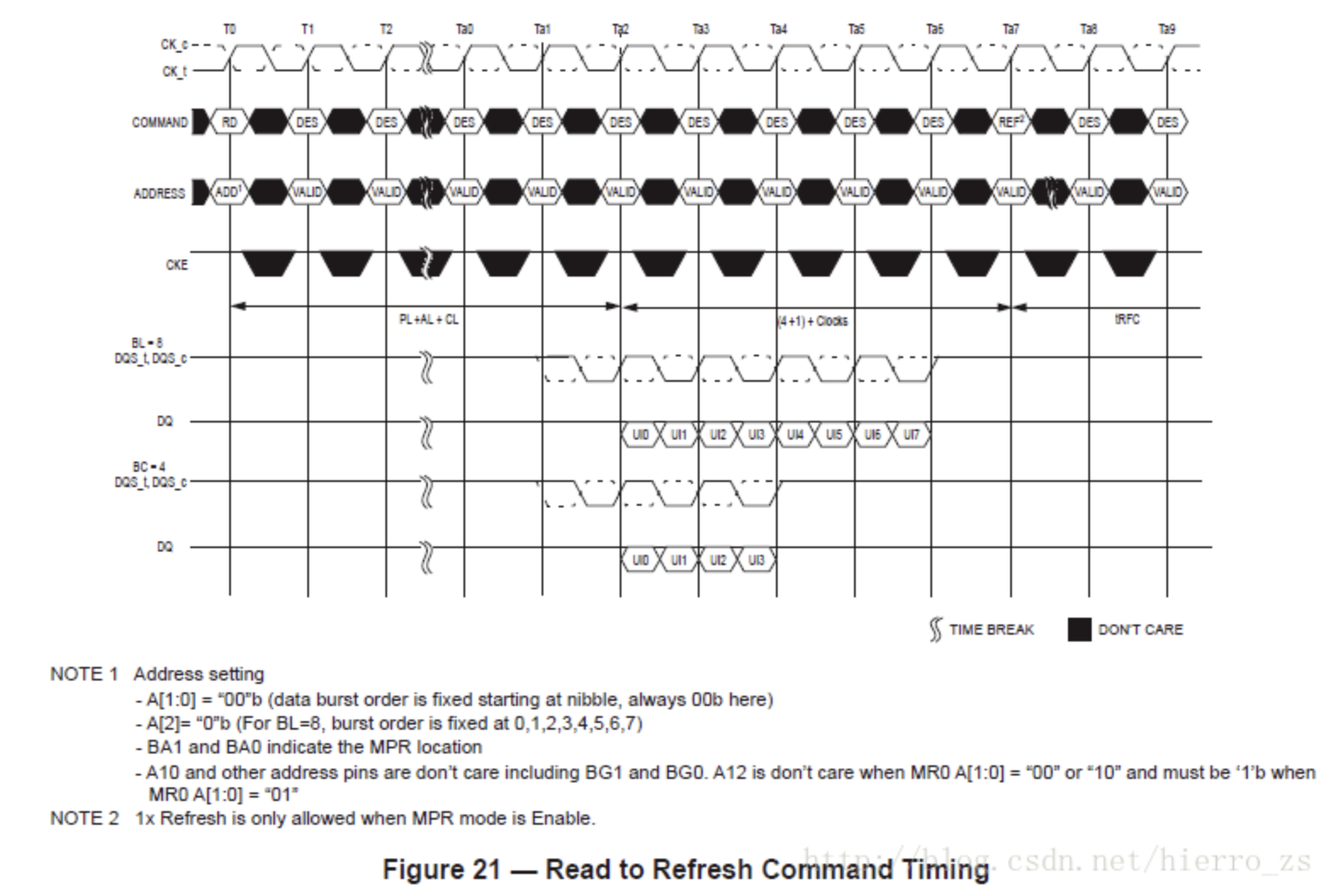

需要注意的是在MPR模式下,RDA和WRA命令的功能与READ和WRITE命令的功能是相同的,也就是说,在MPR模式下RDA和WRA的自动充电部分是被忽略的。在MPR模式下,RESET命令后的tRFC时间内仅允许1x Refrsh命令发送。在MPR操作中,所有的读写命令都必须在Refresh命令之前完成。

4.10.2 MPR的定义

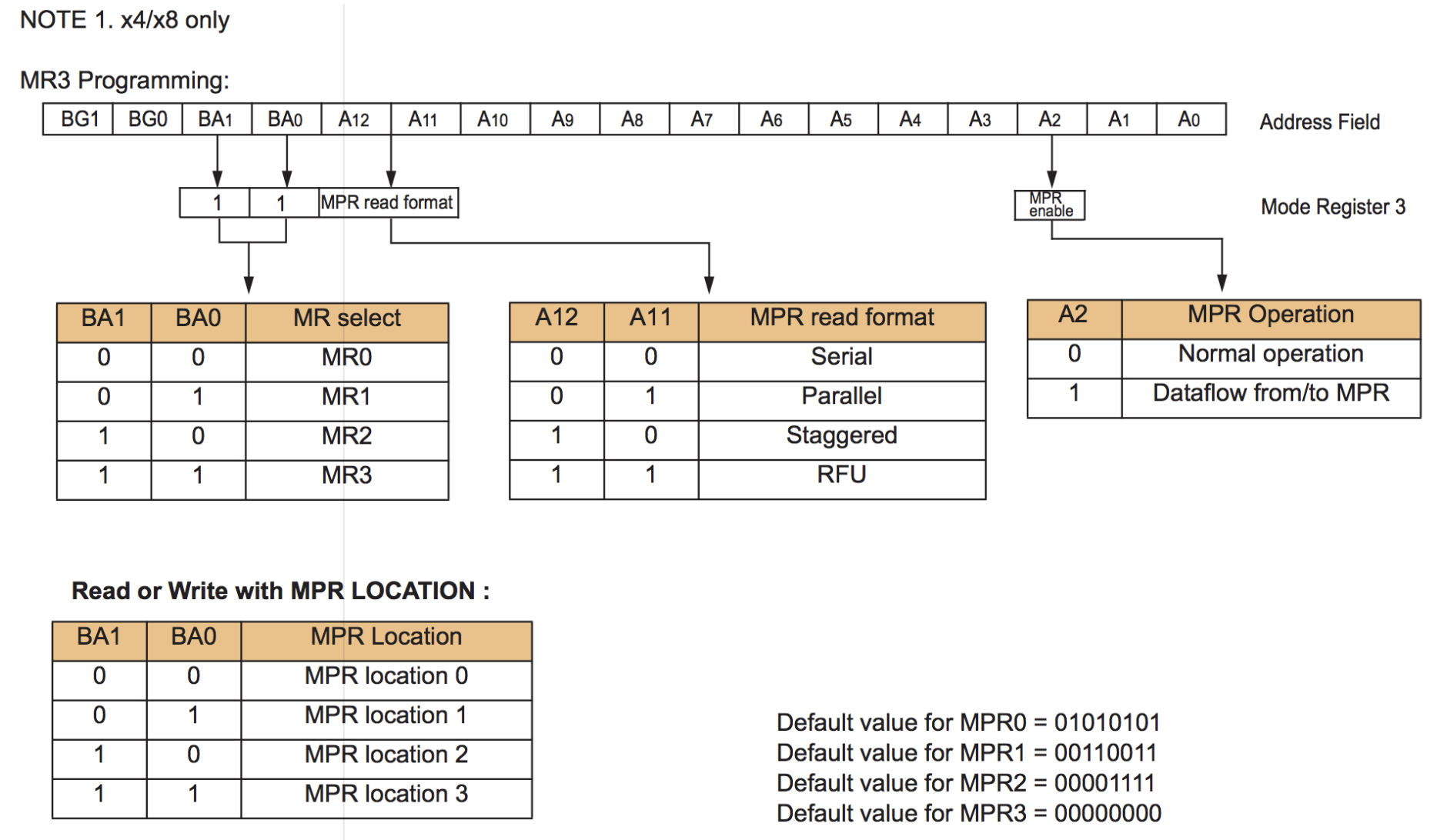

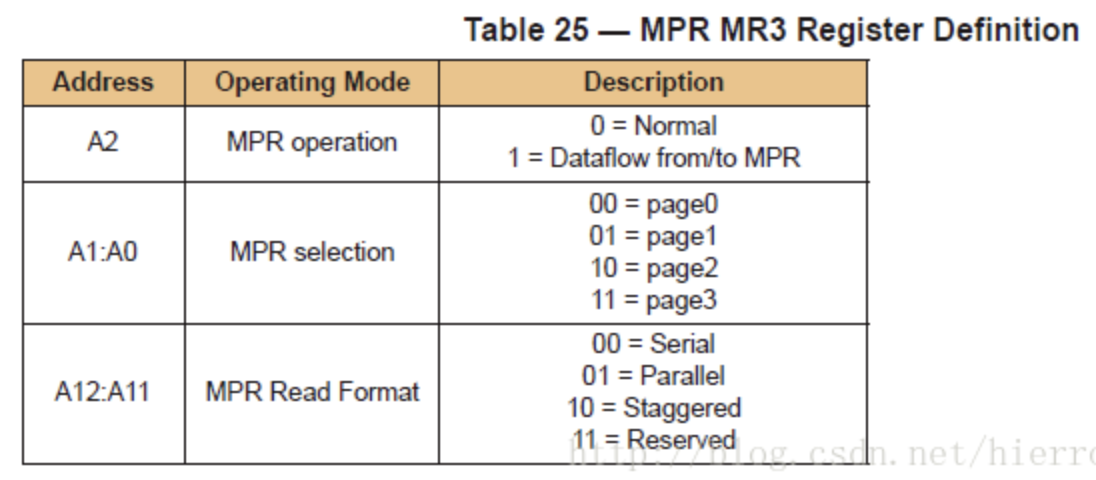

MR3寄存器控制了训练过程中的MPR寄存器的使用。MR3寄存器可通过将CS_n, RAS_n/A16,CAS_n/A15与WE_n/A14驱动至低电平, 将ACT_n, BA0与BA1驱动至高电平,以及 将BG11和BG0驱动至低电平。控制状态与地址引脚可参考下图。

4.10.3 MPR读

DDR4 SDRAM支持BC4与BL8模式读取MPR寄存器的操作,且不支持BC4 OTF模式来读取MPR寄存器。BC4读取MPR寄存器时,BA0与BA1表示了MPR的中选中页的地址,A10、BG0、BG1以及其他的地址总线都是不关心的。使用BC4读MPR寄存器时,列地址的A2:A0仅能取“000”或“001”这两个值中间的一个。

在MPR读操作中,DBI功能是不可用的。

DDR4 MPR模式是通过将A2写为1来使能的,读返回的时间来自于MPR寄存器内的特殊位置。MPR的位置是由Bank地址BA0与BA1来确定的。每一个MPR位置都是8-bits宽的。

步骤:

1.若MR1[A0=1],DLL使能情况下,在进行MPR读操作之前DLL必须已经完成LOCK。

- 执行Precharge ALL命令

- 等待tPR时间满足

- 执行MRS命令,将MR3寄存器A2写1,将所有读写DDR4 SDRAM的操作目的修改为MPR位置。

- 等待tMRD与tMOD时间满足

- 读操作:

- A[0:1]固定为“00”

- A[2]为“0”,在 BL8时,burst序列为固定0,1,2,3,4,5,6,7;在BC4时,burst序列固定为0,1,2,3,x,x,x,x

- A[2]为“1”,BL8不支持,BC4burst序列固定为4,5,6,7,x,x,x,x

- A[12]/BC为“0”或“1”时,不支持BC4 OTF。当MR0[A1:A0]为“01”,在MPR读操作过程中A[12]/BC必须为“1”

- BA0与BA1表示了MPR内的位置

- A10、BG0、BG1以及其他的地址总线都是不关心的

7.在RL=AL+CL之后,DRAM会将MPR的数据输出返回,返回数据的格式会在后面的图中进行描述,并受MR3寄存器中A0、A1、A11与A12的控制。控制器通过不断重复读取MPR寄存器的值来优化整条读通路,在读MPR时可通过读命令实现读取不同MPR地址的读取。在MPR读数据返回完之后需要满足tMPRR时间满足,

- 执行MRS命令,将MR3寄存器A2写0,将所有读写DDR4 SDRAM的操作目的修改为DRAM阵列。

- 等待tMRD与tMOD时间满足

- 继续执行正常的DRAM命令,类似于Activate等。

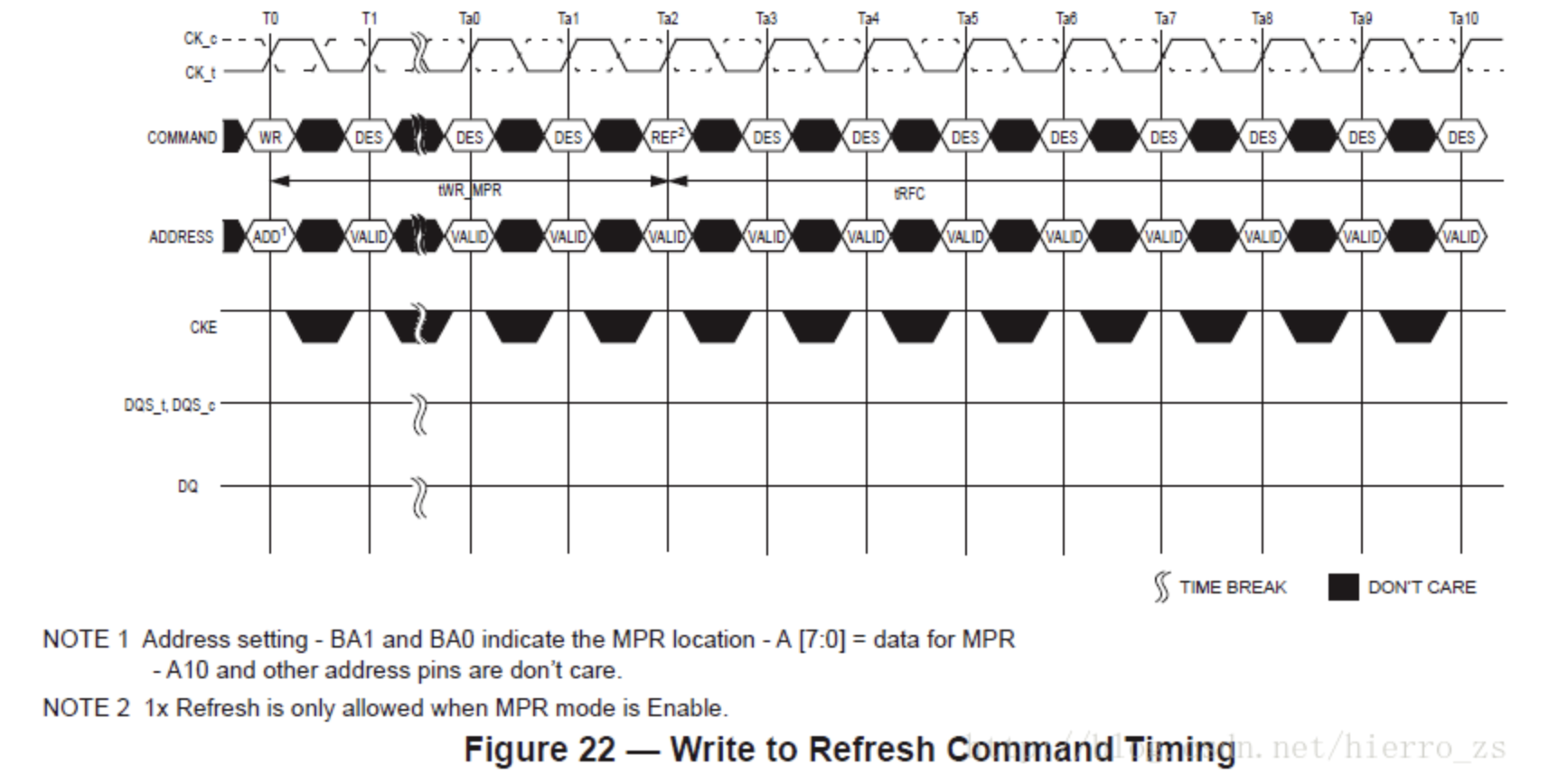

4.10.4 MPR写

DDR4允许8-bits写到MPR内的位置,使用A7:A0作为数据总线。如下表所示。

步骤:

1、若MR1[A0=1],DLL使能情况下,在进行MPR写操作之前DLL必须已经完成LOCK。

2、执行Precharge ALL命令

3、等待tPR时间满足

4、执行MRS命令,将MR3寄存器A2写1,将所有读写DDR4 SDRAM的操作目的修改为MPR位置。

5、等待tMRD与tMOD时间满足

6、写操作:

- BA0与BA1表示了MPR内的位置

- A7:A0作为写MPR寄存器的数据

7、等待tWR_MPR时间满足,此时DRAM已经满足一次MPR写操作

8、控制器通过不断重复写入与读取MPR寄存器的值来优化整个通路。在MPR读数据返回完之后需要满足tMPRR时间满足,

- 执行MRS命令,将MR3寄存器A2写0,将所有读写DDR4 SDRAM的操作目的修改为DRAM阵列。

- 等待tMRD与tMOD时间满足

- 继续执行正常的DRAM命令,类似于Activate等。

4.10.5 MPR写数据格式

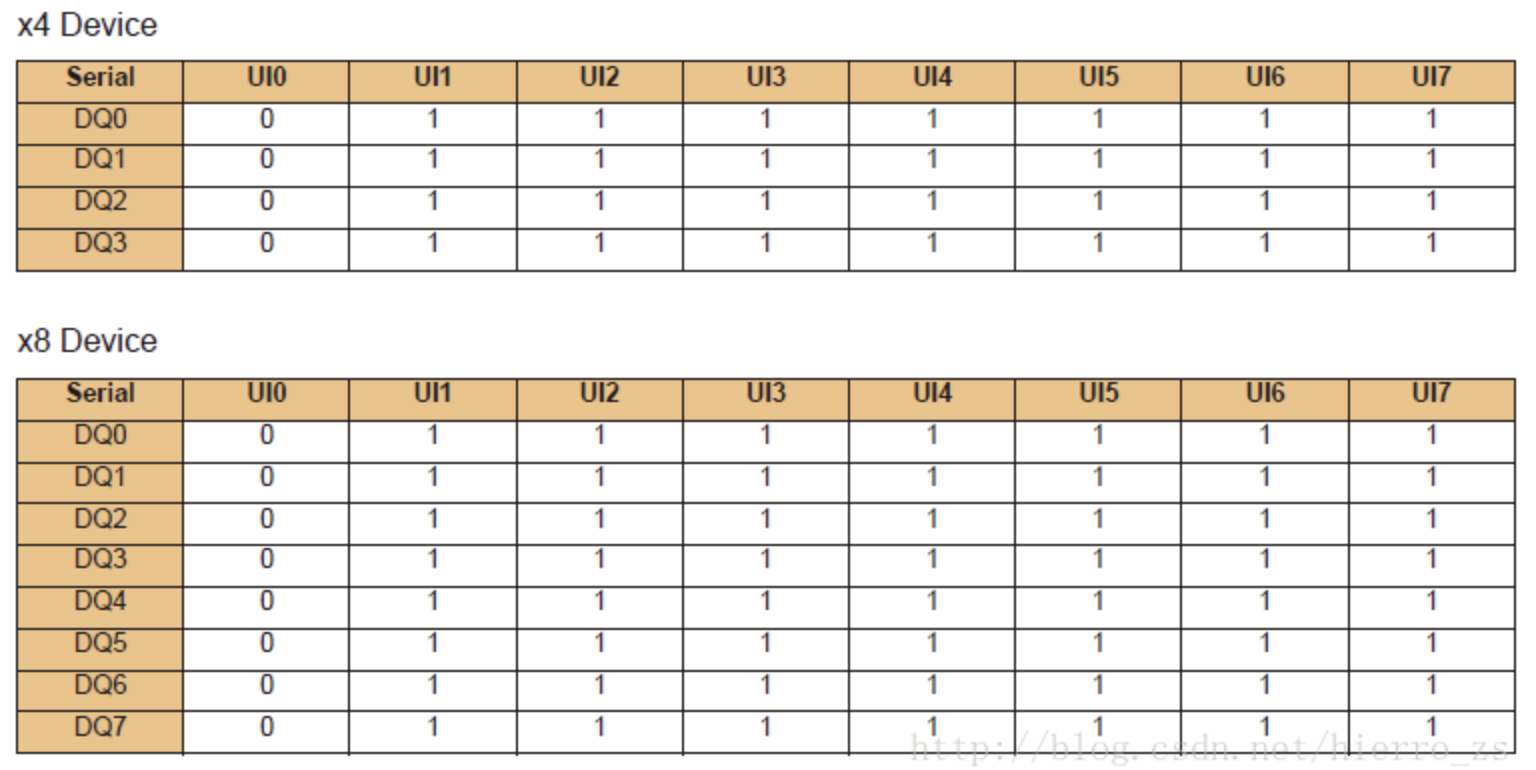

MR3[A12:A11]是位模式,用来选择MPR读操作返回数据的格式。在所有的返回数据格式中,DRAM都会驱动相应的选通信号匹配读数据。

如下表所示,串行返回模式表示所有的DQ位都是返回的相同的数据。在串行返回模式中,数据可来自于MPR寄存器的第0,1,2,3页中。在以下例子中,MPR[7:0]中预定义了数据“0111 1111”。

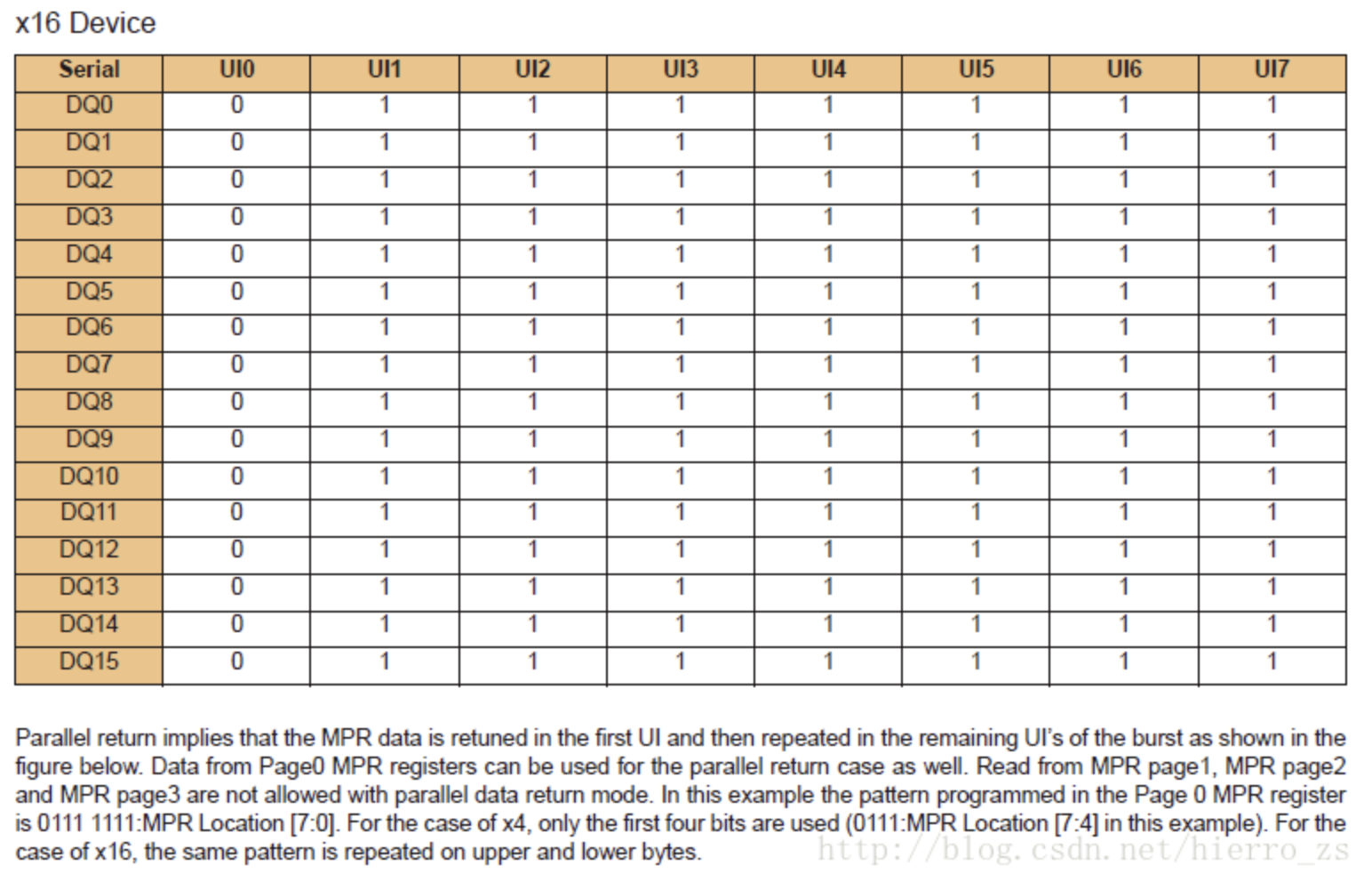

并行返回模式表示每一根DQ线上在一个burst中将返回MPR寄存器的第一个UI的数据,且每一个DQ都是相同的。可使用MPR寄存器的第0页,但不可使用第1,2,3页中的数据。在如下例子中,MPR寄存器的第0页[7:0]已预定义为“0111 1111”。在x4设备中,仅能返回[7:4]“0111”,在x16设备中,会将低8位的数据复制到高8位。

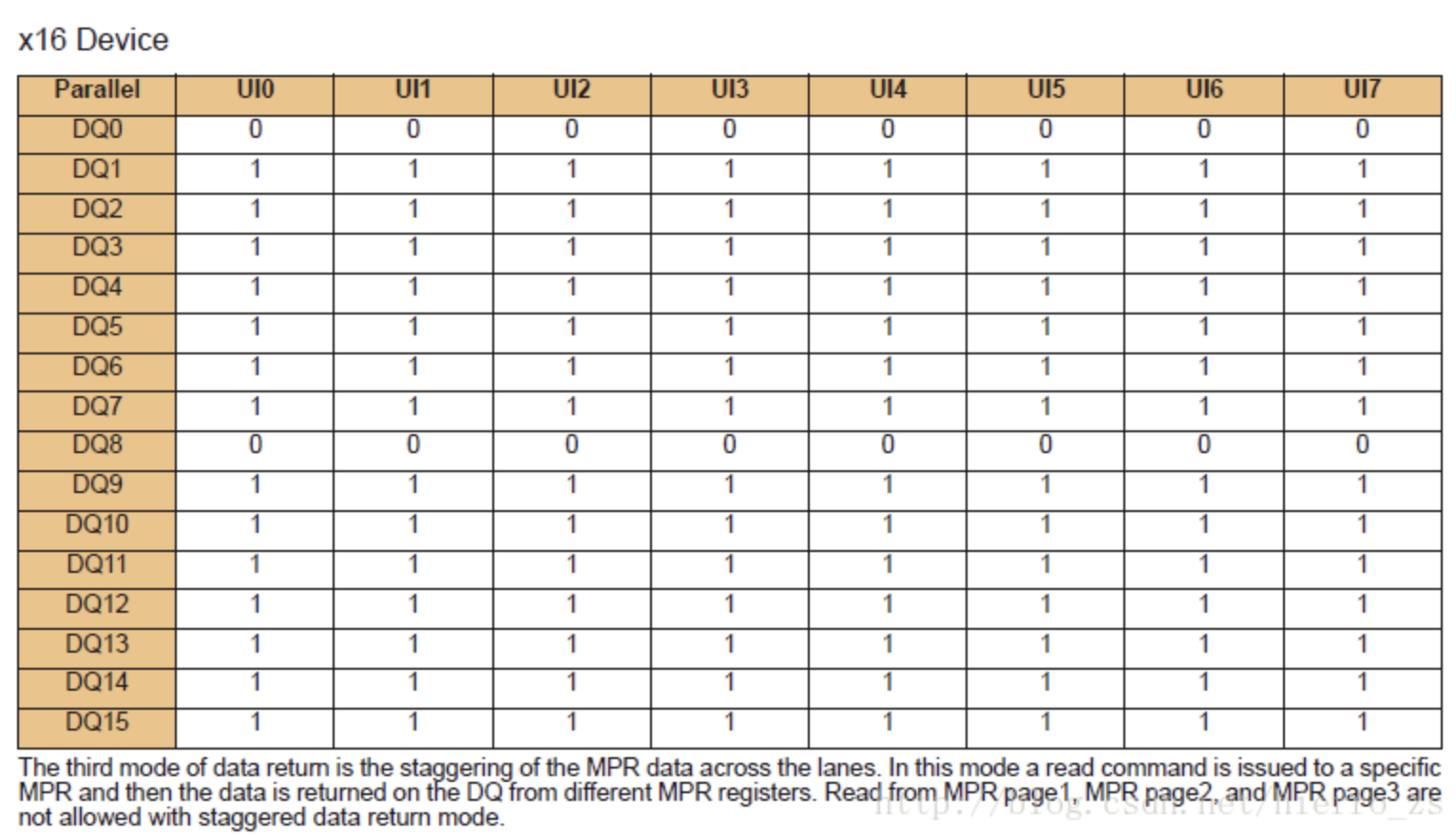

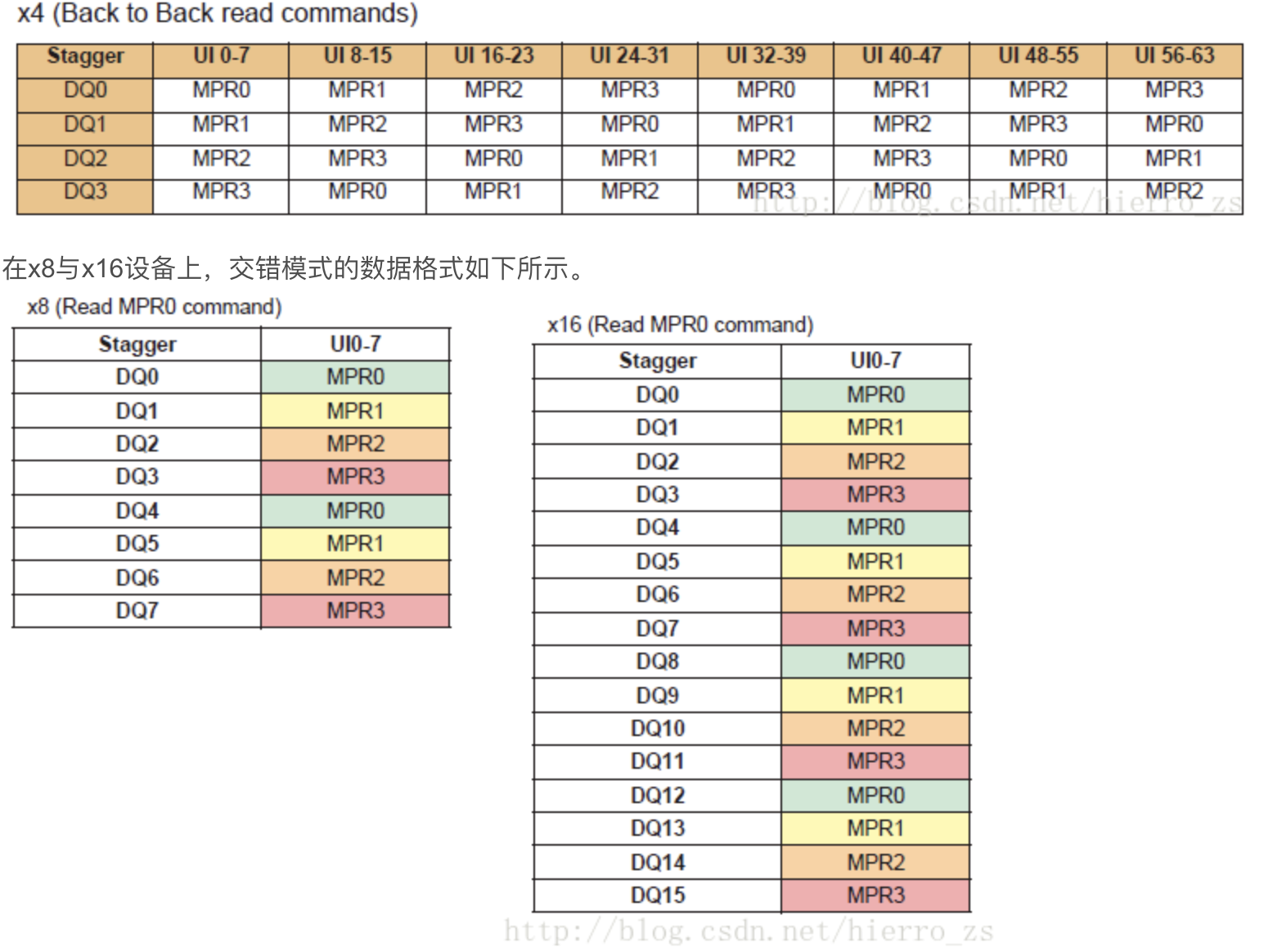

第三种模式为交错模式,在使用这种模式读取MPR时,MPR0-3的数值会轮流出现在DQ总线上。在此模式中MPR的第1,2,3页是不可用的。

在x4模式中,若读取MPR0地址,则MPR0出现在DQ0上,MPR1将出现在DQ1上,MPR2与MPR3分别出现在DQ2、DQ3上。若此时读取MPR1地址,则MPR1出现在DQ0上,MPR2出现在DQ1上,如下图所示。

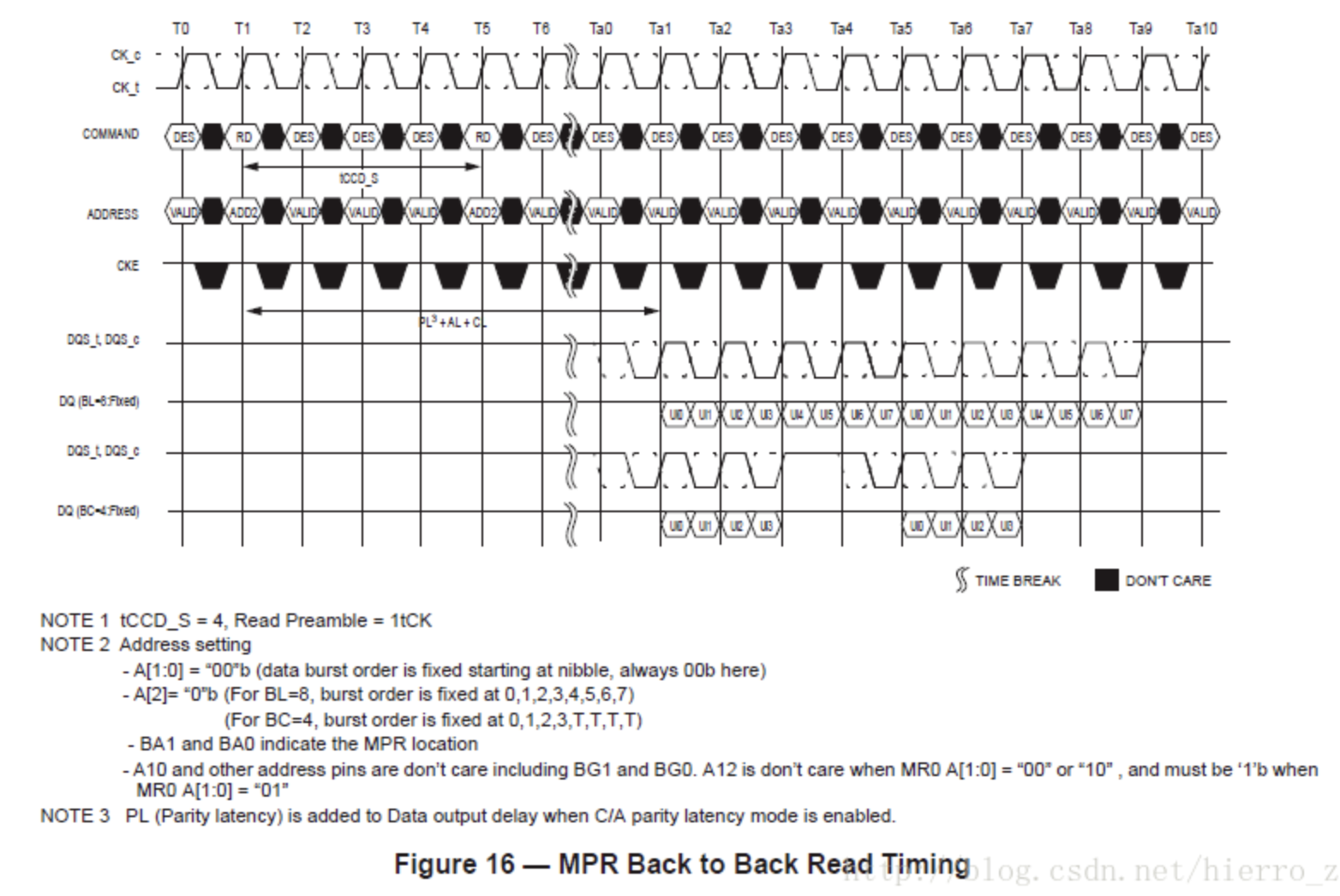

在DDR4 SDRAM上提供了一种背靠背的读取MPR寄存器的方法,此方式可以在任何频率下进行操作,且可产生一种无气泡或空闲时钟的数据流。在此方式下,控制器需连续的发送如下命令序列:RD

MPR0, RD MPR1, RD MPR2, RD MPR3, RD MPR0, RD MPR1, RD MPR2 and RD MPR3

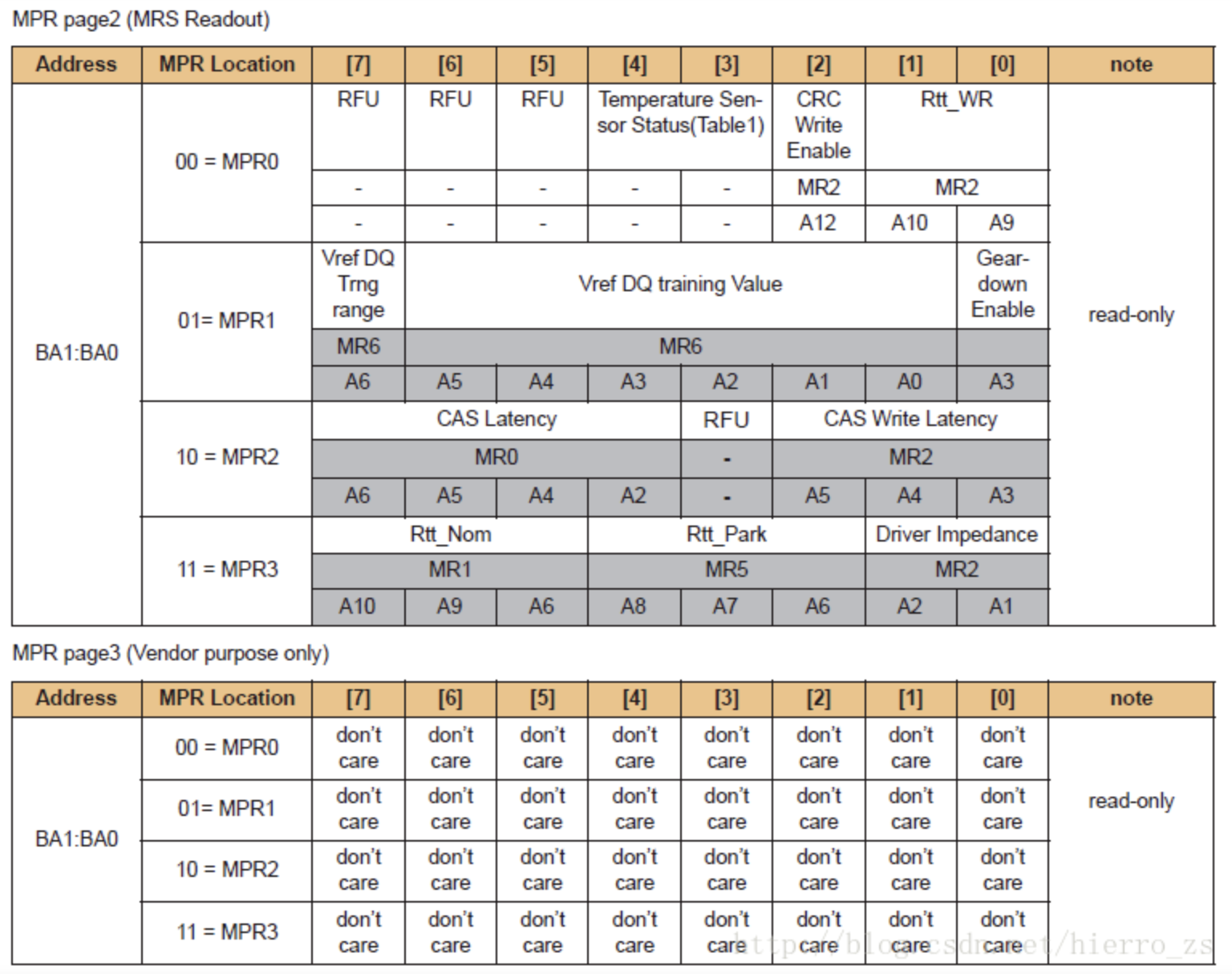

下表中列出了MPR模式中对页的操作方法。

在DDR4 SDRAM提供的MPR寄存器中,Page 0是可读可写的,而Page1,2,3是只读的。在所有的MPR0-3中,Page 0在三种模式下都是可以读取的,而其他三个页仅在串行模式下可以读取。

在上电之后,MPR寄存器内的值必须如下图所示,MPR第0页仅在控制器发出写MPR命令时可被改写。在没有MPR写命令时,DRAM必须永久保持MPR内的数据,并不得以任何原因修改其数值。

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.8-4.9)

- JESD79-4 第4章 SDRAM命令描述与操作(4.5-4.7)

- JESD79-4 第4章 SDRAM命令描述与操作(4.1-4.4)

- JESD79-4 第3章 功能描述

- JESD79-4 第2章 DDR4 SDRAM 的引脚封装与寻址

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。