4.11 数据掩码(DM),数据总线翻转(DBI),以及TDQS

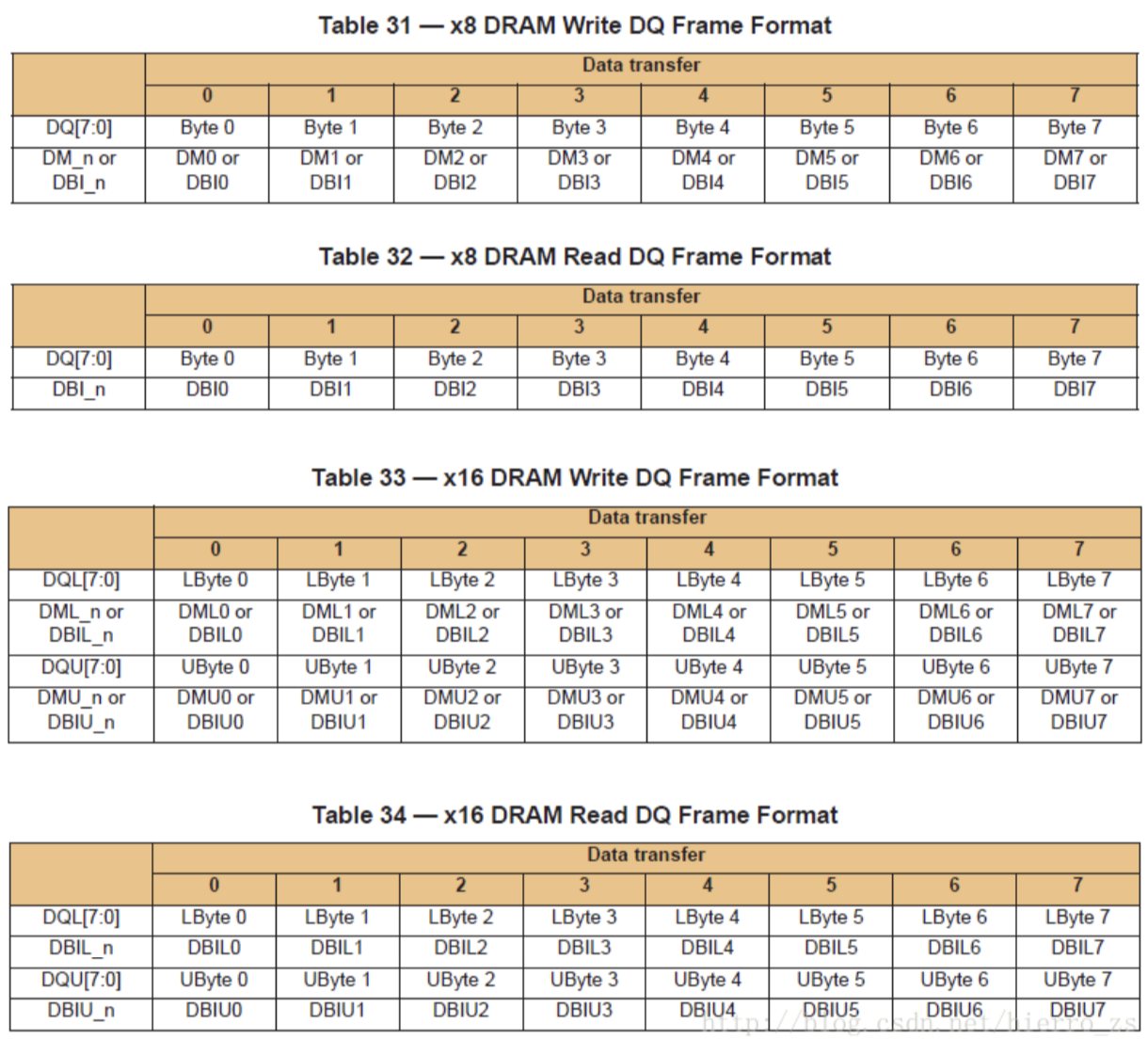

DDR4 SDRAM中的x8、x16设备支持DM、DBI功能。x4设备不支持DM、DBI功能。x8设备支持TDQS功能,x4、x16不支持TDQS功能。

DM、DBI以及TDQS功能都需要专门的一个引脚来实现,例如

DM_n/DBI_n/TDQS_t,这些引脚都是双向的DRAM引脚。DM_n/DBI_n信号在DDR4中的参考终结电阻下,都是低电平有效的。TDQS功能不会再实际引脚上驱动任何电压。

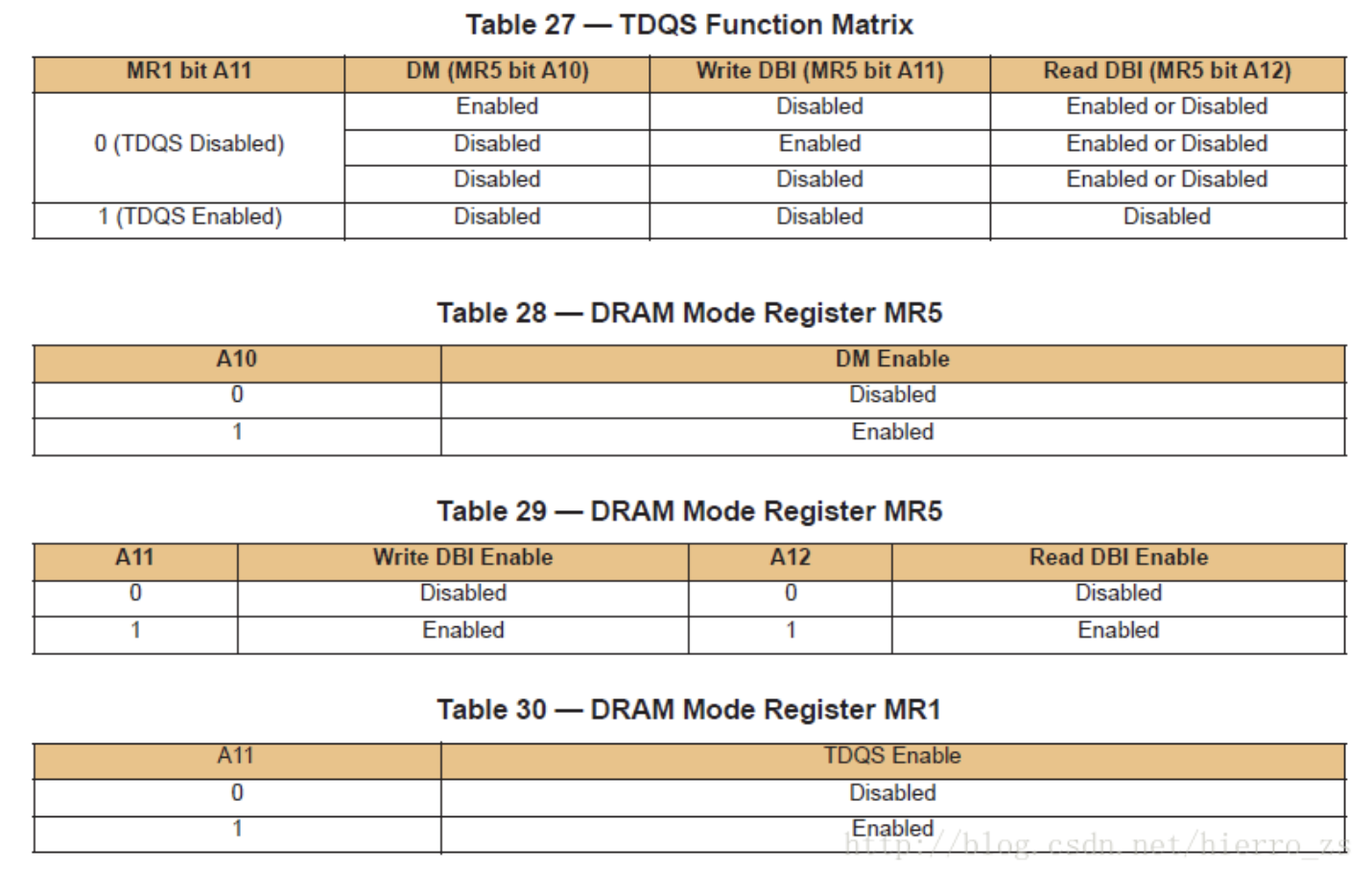

DM、DBI、TDQS的功能都是在SDRAM的模式寄存器MR中定义的,由MR1的A11以及MR5的A12:A10确定的。

写操作时,DBI与DM功能都是可以使用的,但是这两个功能无法同时开启。当DM与DBI功能都关闭时,DRAM将关闭此引脚的接收器,并且不需要任何逻辑状态。

读操作时,仅DBI功能可用。当DBI功能关闭时,DRAM将关闭此引脚的接收器,并且不需要任何逻辑状态。

TDQS功能,当此功能开启时,DM与DBI功能都不能使用了。当此功能关闭时,DM与DBI功能的可用方式可参考下面表格所示。当TDQS功能开启时,

TDQS_c/TDQS_t引脚的终端电阻设置与DQS_t/DQS_c引脚的设置相同。

在写操作中的DM功能:在指定的bytelane中,若DM_n为低电平,则DRAM将屏蔽此bytelane的相应的写数据;若DM_n为高电平,则DRAM不会屏蔽这个bytelane的所有写数据。

写操作中的DBI功能,当DBI_n为低电平时,DRAM将把相应的写数据做位翻转,若DBI_n为高电平,DRAM将不会对数据进行翻转操作。

读操作中的DBI功能,当DRAM的返回数据中的“0”个数超过4的时候,DRAM会将读数据进行翻转,且将DBI_n引脚驱动为低电平。否则DRAM不会翻转数据,且将DBI_n驱动为高电平。

4.12 ZQ校准命令

4.12.1 ZQ校准描述

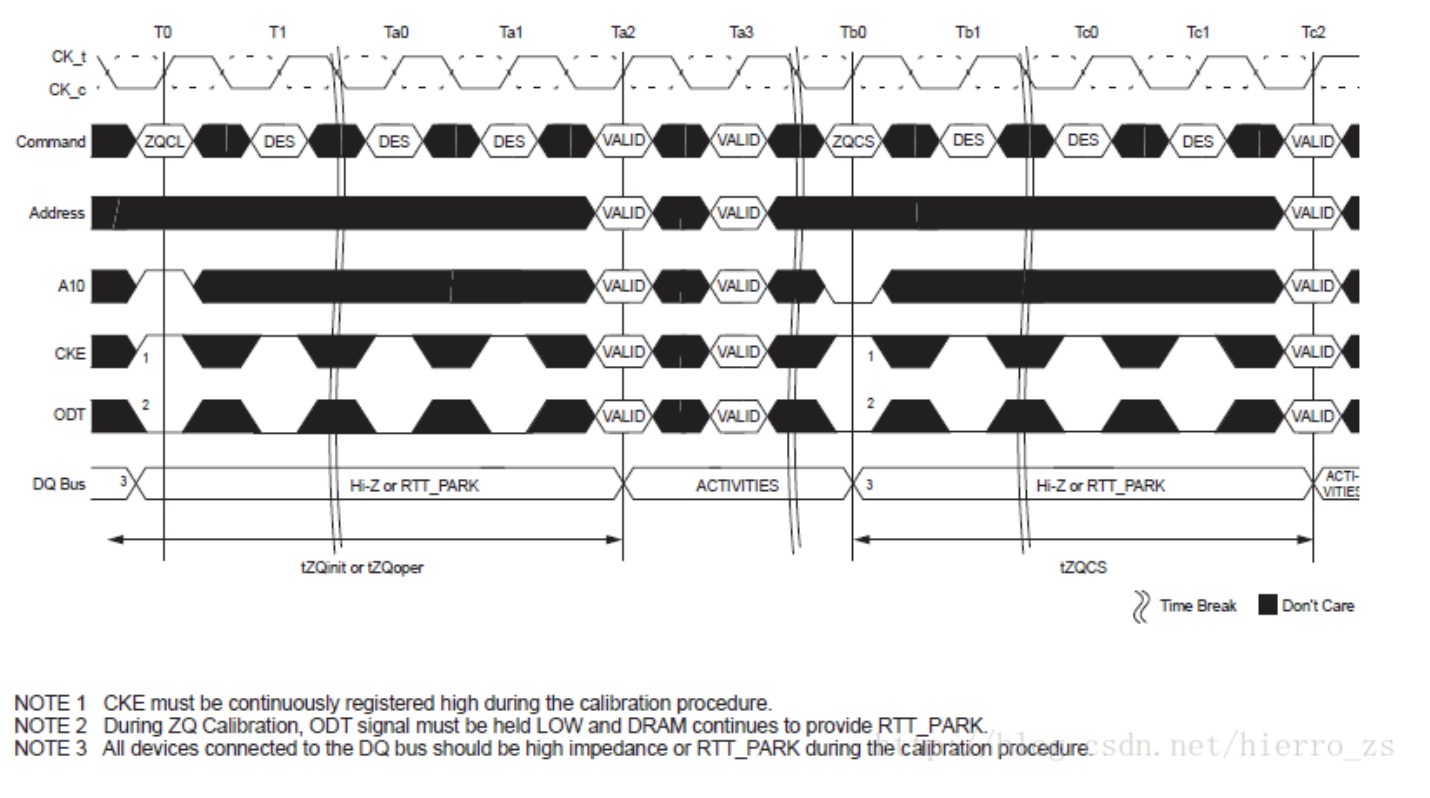

ZQ校准命令是用来校准SDRAM的Ron与ODT阻值的。在DDR4 SDRAM中,在初始化Ron与ODT电阻时,需要更长的校准时间,但是在后期执行周期性的校准时所需的时间则会更少。

ZQCL命令是在SDRAM上电初始化期间执行第一次校准时使用的。此命令可由控制器根据系统环境决定在任何时间发送至SDRAM。ZQCL命令可触发SDRAM内部的阻抗校准引擎,一旦校准完成,校准值将会使用更新的握手协议从引擎传送至IO口,以更新IO引脚的Ron与ODT电阻。

在完成复位之后,ZQCL命令执行时间为tZQinit,此时间包含了一个完整的校准过程,以及校准结果的传输时间。

ZQCS命令是用来执行周期性的校准,以补偿电压与温度变化带来的差异。此命令所需的时间比ZQCL要小,由参数tZQCS来定义。一个ZQCS命令最小可补偿Ron与ODT错误的0.5%,并在所有的引脚速度下与最大的敏感度下,仅需128个CK周期即可完成。具体描述在“Output Driver Voltage and Temperature Sensitivity”与 “ODT Voltage and Temperature Sensitivity”表格中。通过这些表格中和其他的参数,可确定一个最合适的ZQCS命令校准间隔。一种计算ZQCS命令之间间隔的公式如下所示,需要给出SDRAM在应用中电压与温度漂移速度(Tdriftrate & Vdriftrate):

tZQCSinterval = ZQCorrection / ((TSens * Tdriftrate) + (VSens * Vdriftrate))

在上面公式中,TSens = max(dRTTdT, dRONdTM)、VSens = max(dRTTdV, dRONdVM),这两个参数定义了SDRAM的温度与电源敏感度。

例如,假设TSens = 1.5% / oC, VSens = 0.15% / mV, Tdriftrate = 1 oC / sec and Vdriftrate = 15 mV / sec,那么ZQCS命令时间间隔可得到如下结果:

0.5/((1.5*1)+(0.15*15))=0.133

约为128ms

在时间参数tZQinit, tZQoper或tZQCS内,不允许有其他的请求访问SDRAM,无访问时间保证了Ron与ODT电阻的精确校准。并且在SDRAM完成校准之后,会将ZQ引脚上的电流关闭以减小功耗。

在控制器发射ZQCL或ZQCS命令之前所有的Bank都必须被关闭,即控制器需要发射Precharge ALL命令,且需要满足时间tRP的要求。ZQCL和ZQCS命令的真值表需要参考4.1章节中的表格“Command Truth

Table”。

在退出自刷新以后,ZQ校准命令可在DLL Lock时间内发送。在退出自刷新之后,SDRAM不会执行IO的校准动作,除非收到明确的ZQ校准命令。在SRX命令之后可发送ZQ校准命令的时间最短可参考XS, XS_Abort/ XS_FAST,具体选择需要根据实际操作来决定。

若在一个系统中,有多个设配共享ZQ电阻,那么控制器需要确定这些设备的tZQoper, tZQinit或tZQCS没有任何重叠。

4.13 DQ Vref训练

概述(非标准中所述):仅在系统引导过程中进行VRefDQ训练。一旦训练完毕,并最优VRefDQ_t (DC)电压电平是确定的,该

最佳VRefDQ_t (DC)电压电平将系统在运行时使用。在VRefDQ训练期间, VRefDQ从VDD的40%扫到VDD的60%至

找到最优VRefDQ_t (DC)电压电平。一旦找到最佳VRefDQ_t (直流)被设置时,它必须在它的设定值的±1%的停留以及不能少

低于VDD的45%或超过VDD的55%。

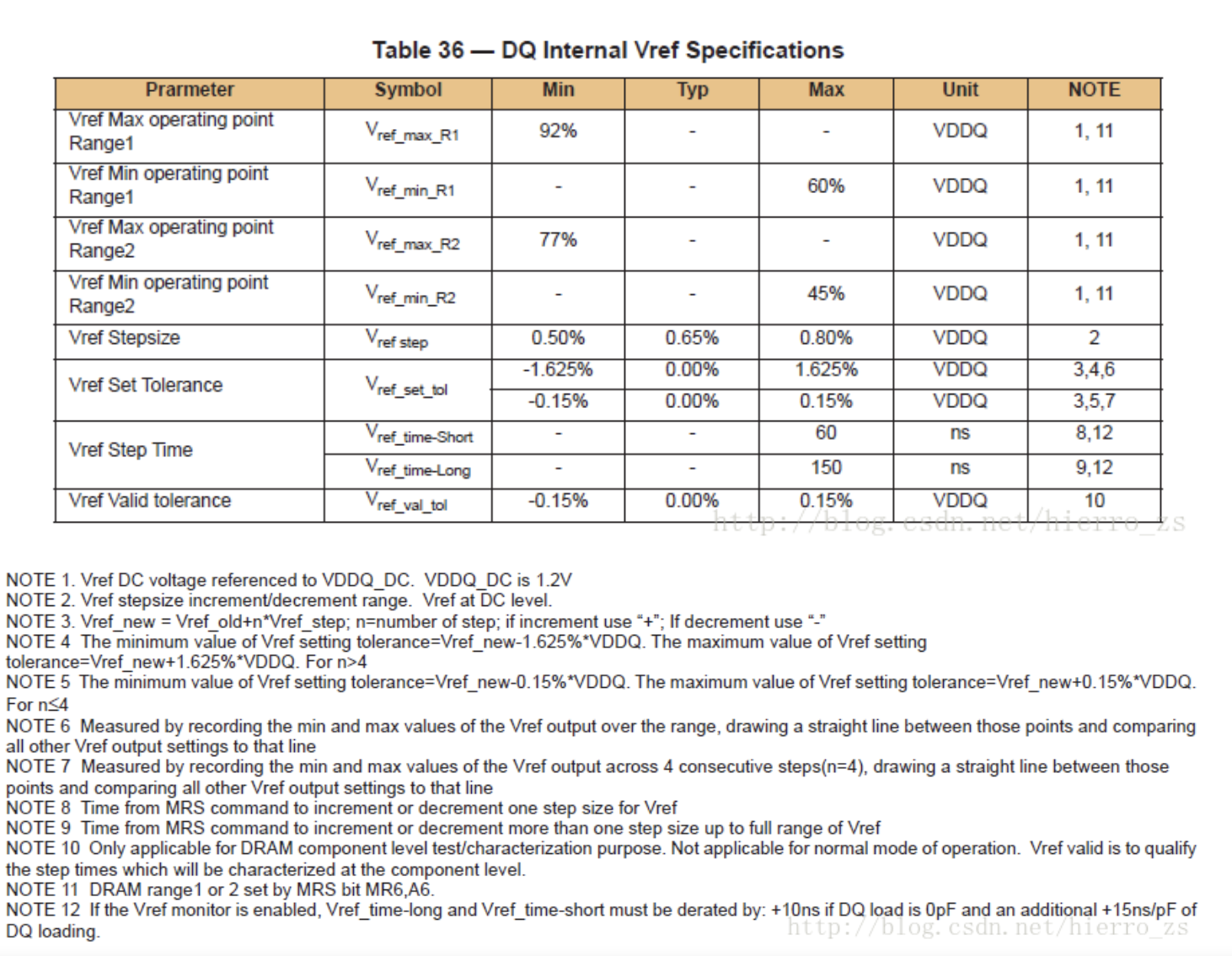

SDRAM内部的DQ Vref规格参数包含:operating voltage range, stepsize, Vref step time, Vref full step time与Vref valid level.

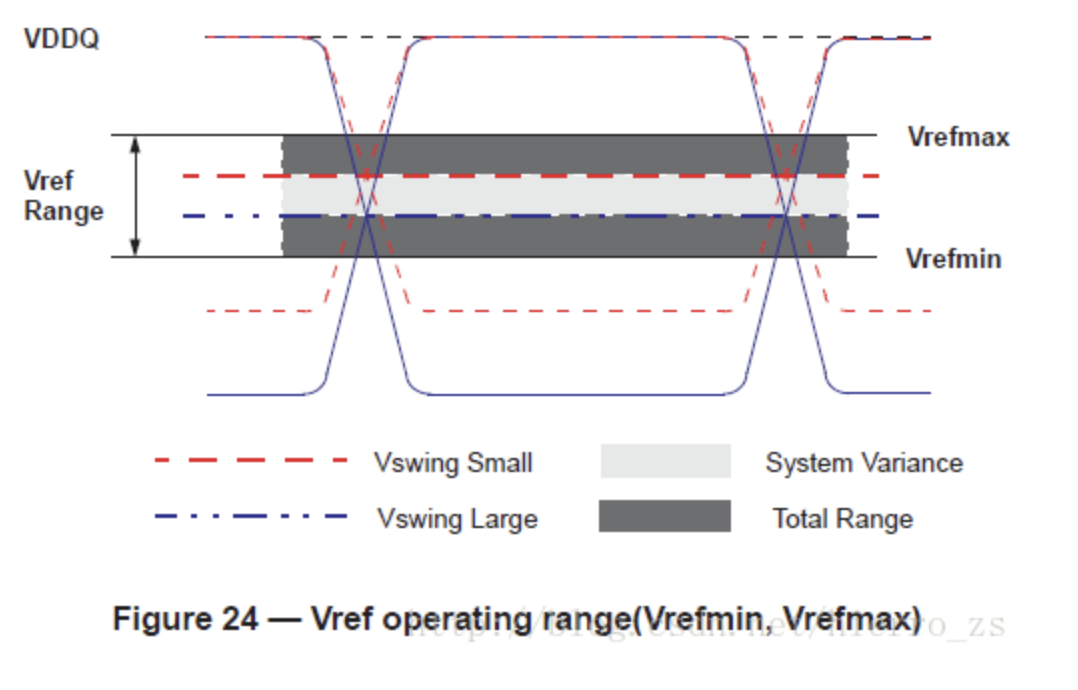

Operating Voltage Range描述了DDR4 SDRAM设备要求的Vref设定范围的最小值。最小范围是由下图中描述的Vrefmax与Vrefmin来确定的。

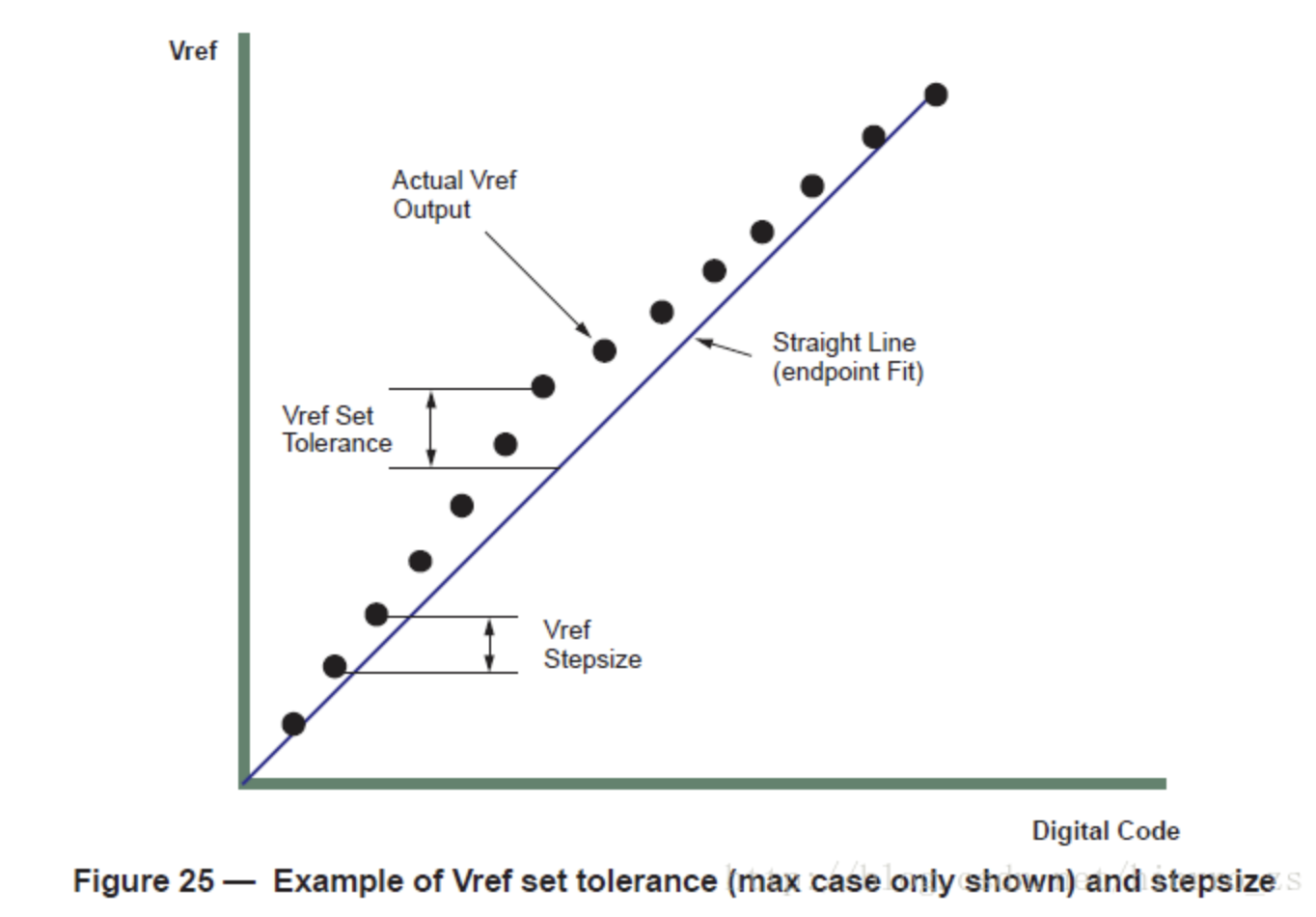

Vref Stepsize是定义了两个相邻的step之间的步长。Vref Stepsize的范围是0.5% VDDQ到0.8% VDDQ。但是在一个确定的系统中,SDRAM的Vref Stepsize为此范围中的一个固定的值。

Vref set tolerance定义为实际Vref电压到理想值之间的变化量。此参数表明了多个步骤之间的错误。Vref set tolerance的不确定度有两个范围。此参数的不确定度是一个关于步骤数(step n)的函数。

Vref set tolerance是相对于基于两个端点的理想线的测量。这两个端点分别位于Vref标准值的最大值与最小值。下图描述了Stepsize与Vref set tolerance。

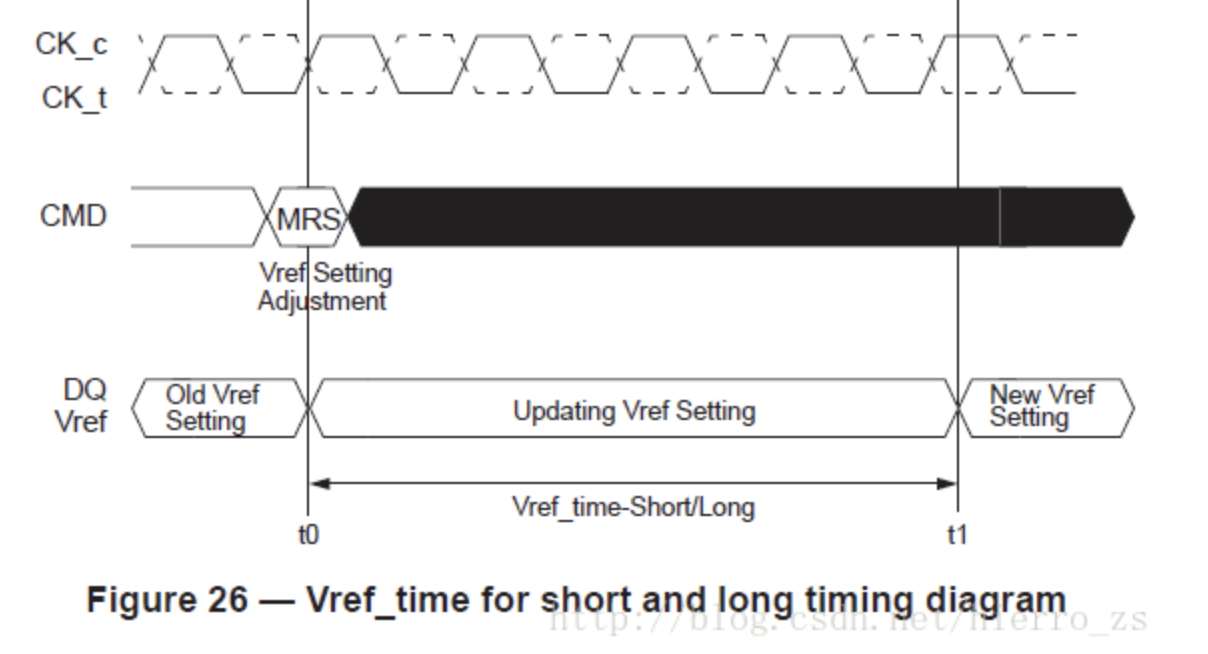

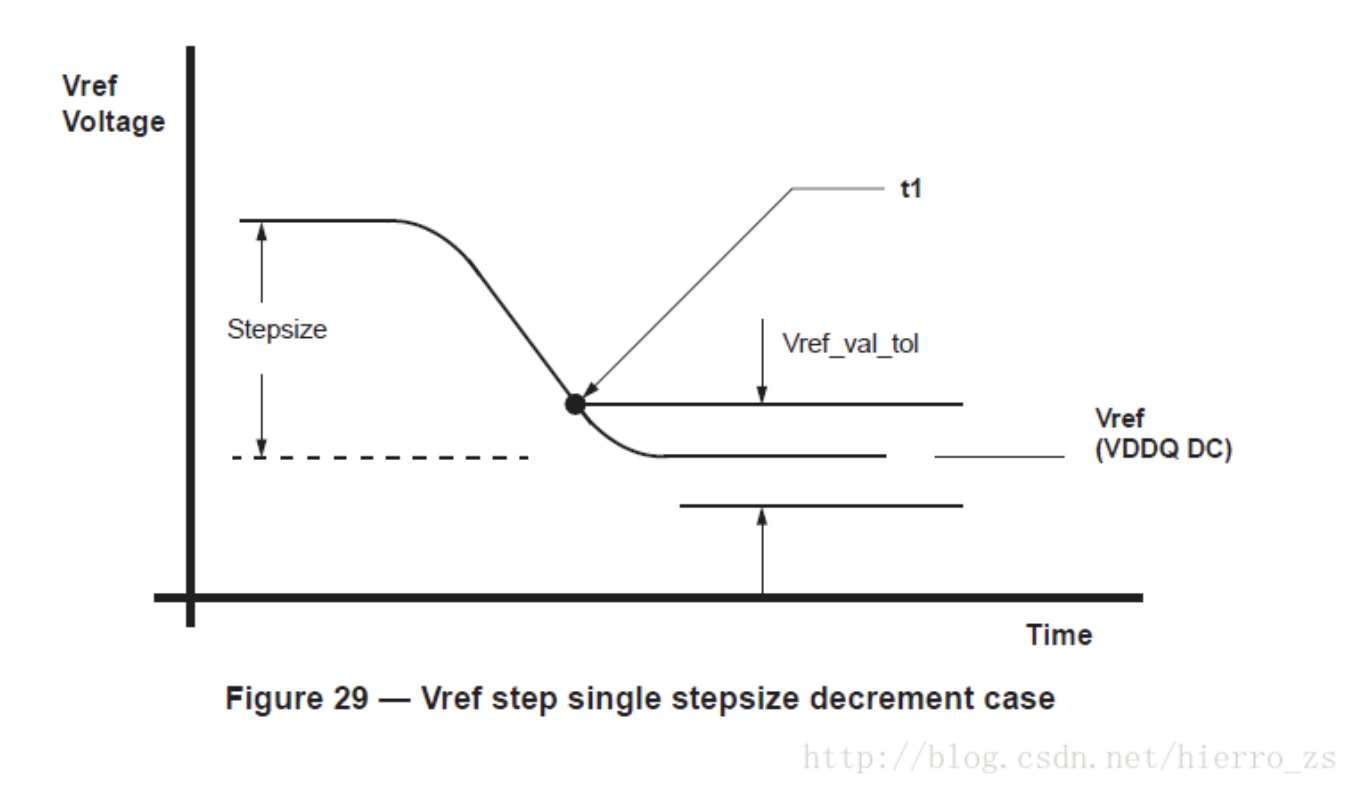

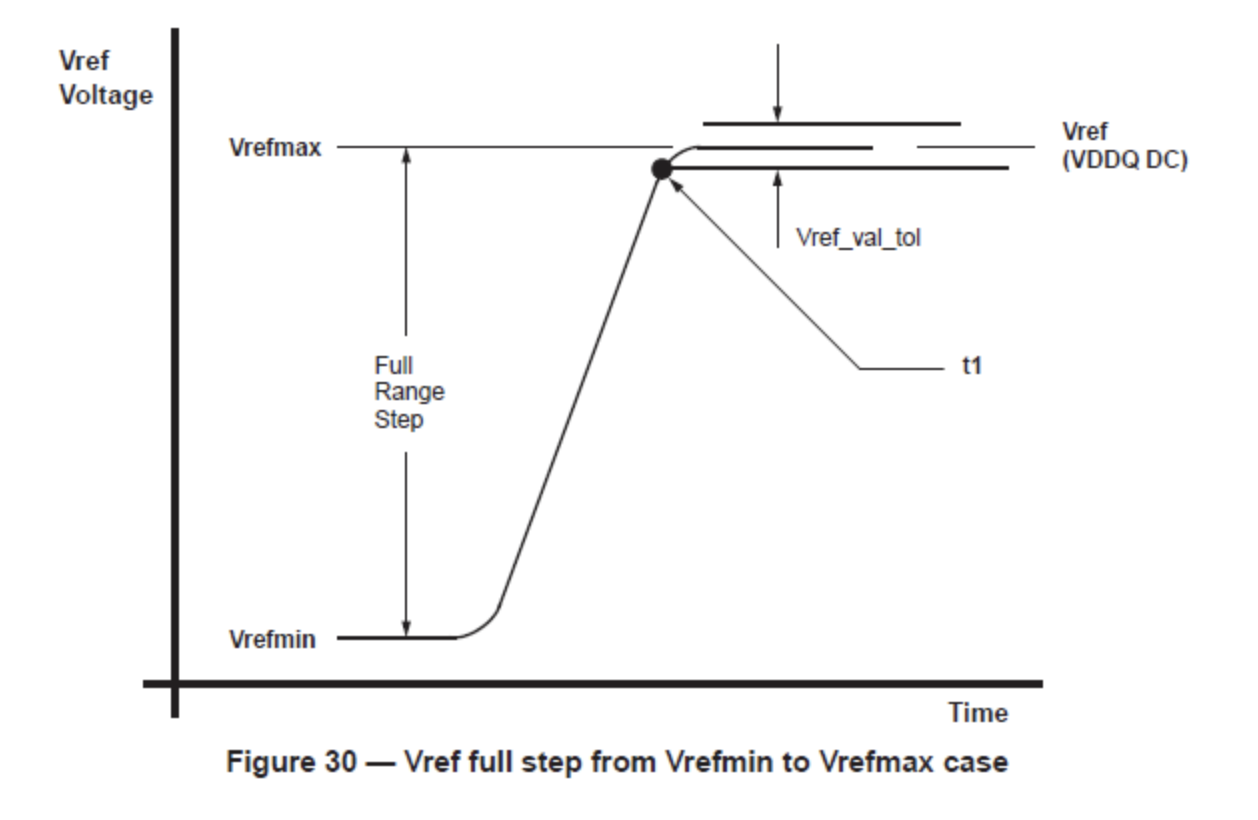

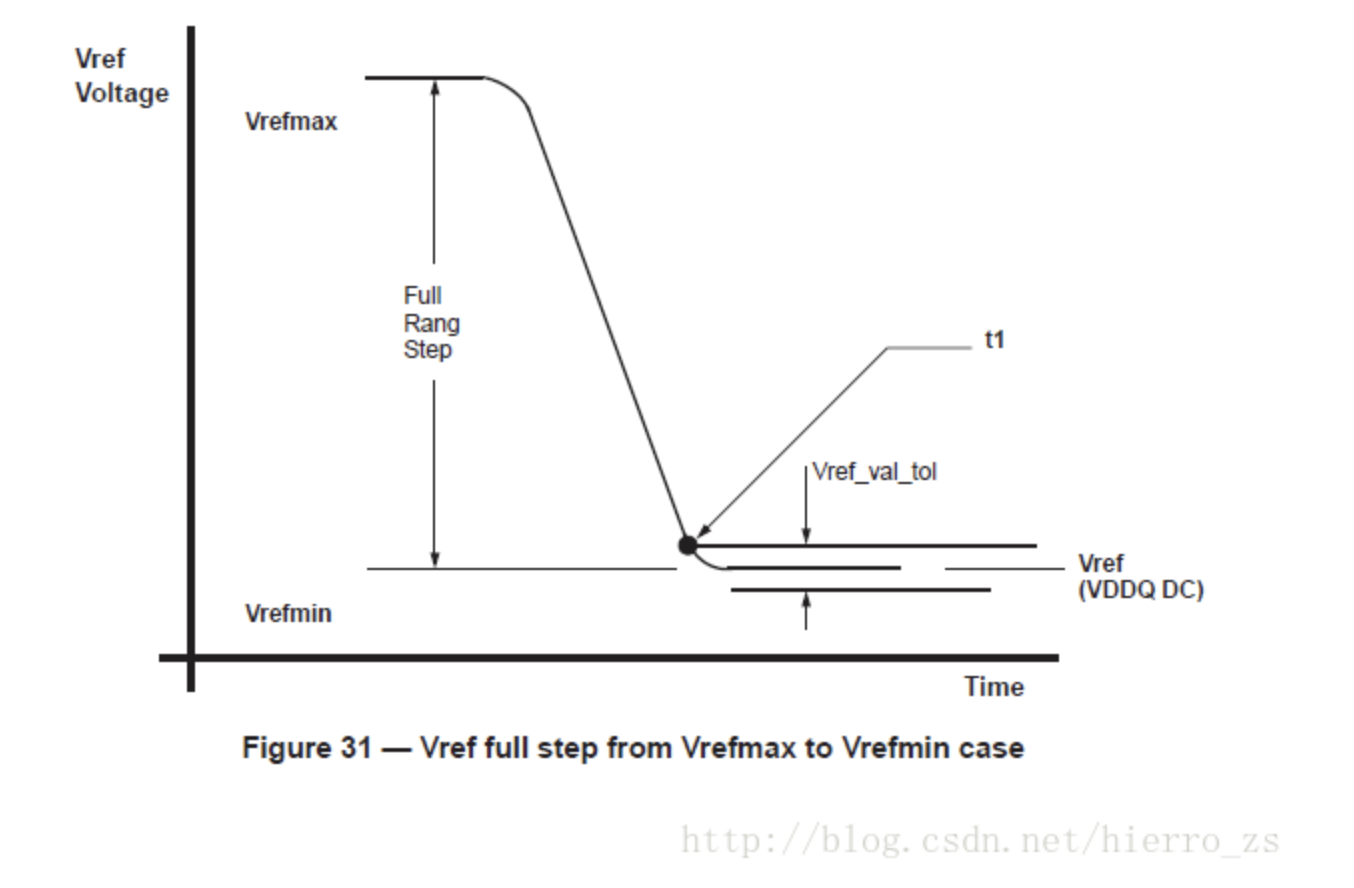

Vref增加或减少的步骤时间为参数Vref_time-short与Vref_time-long。在下图中,Vref_time-short与long的定义为t0时刻到t1时刻。t1时刻为vref达到可参考的DC水平,并在vref valid公差范围之内(Vref_val_tol)。

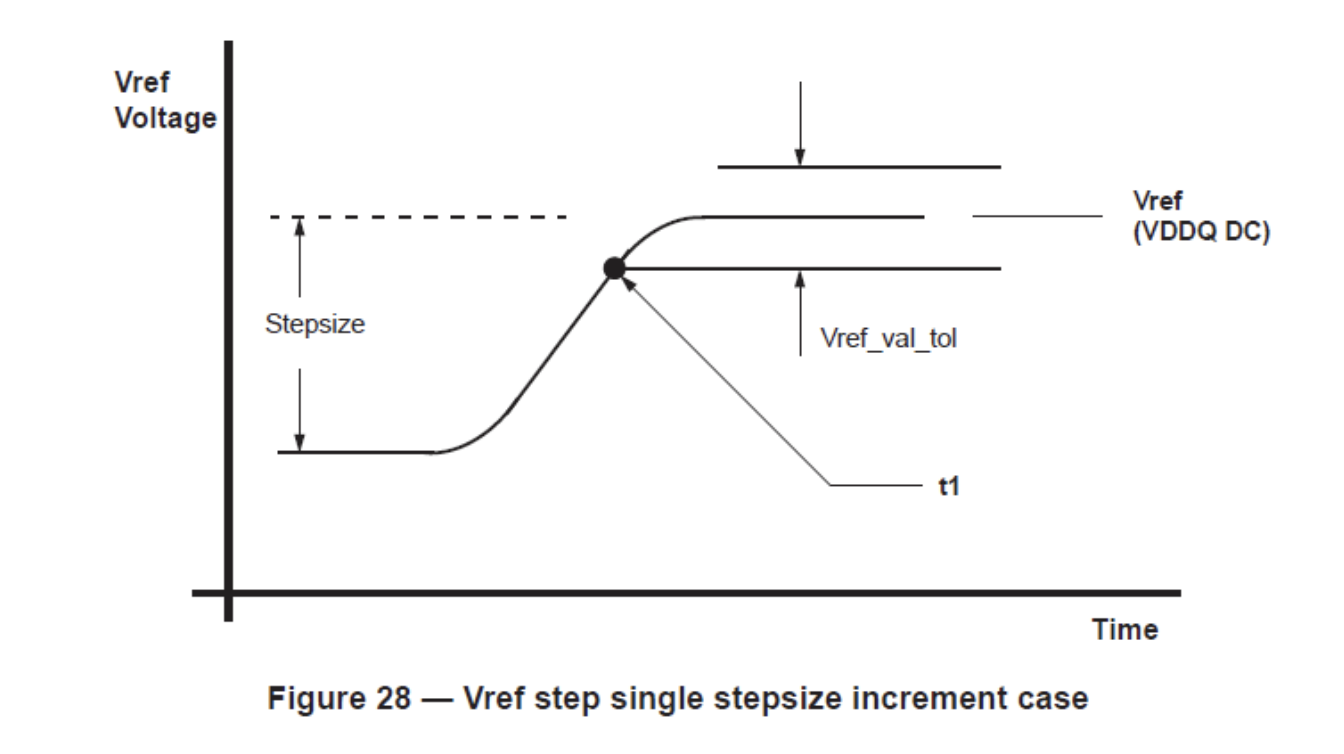

如下图所示,vref 有效电平由Vref_val公差来确定,从而保证了t1步骤的时间。该参数用于在任何Vref增量/减量调整之后,确保电压电平变化时的时间常数RC行为是合适的。此参数仅适用于DRAM组件级验证与表征。

Vref_time-Short表示在Vref电压增加与减少中的单步步长。

Vref_time-Long表示在Vref电压从最大值变化到最小值或从最小值变化到最大值的时间。

t0参考的是MRS命令的时钟

t1参考的是vref_val_tol

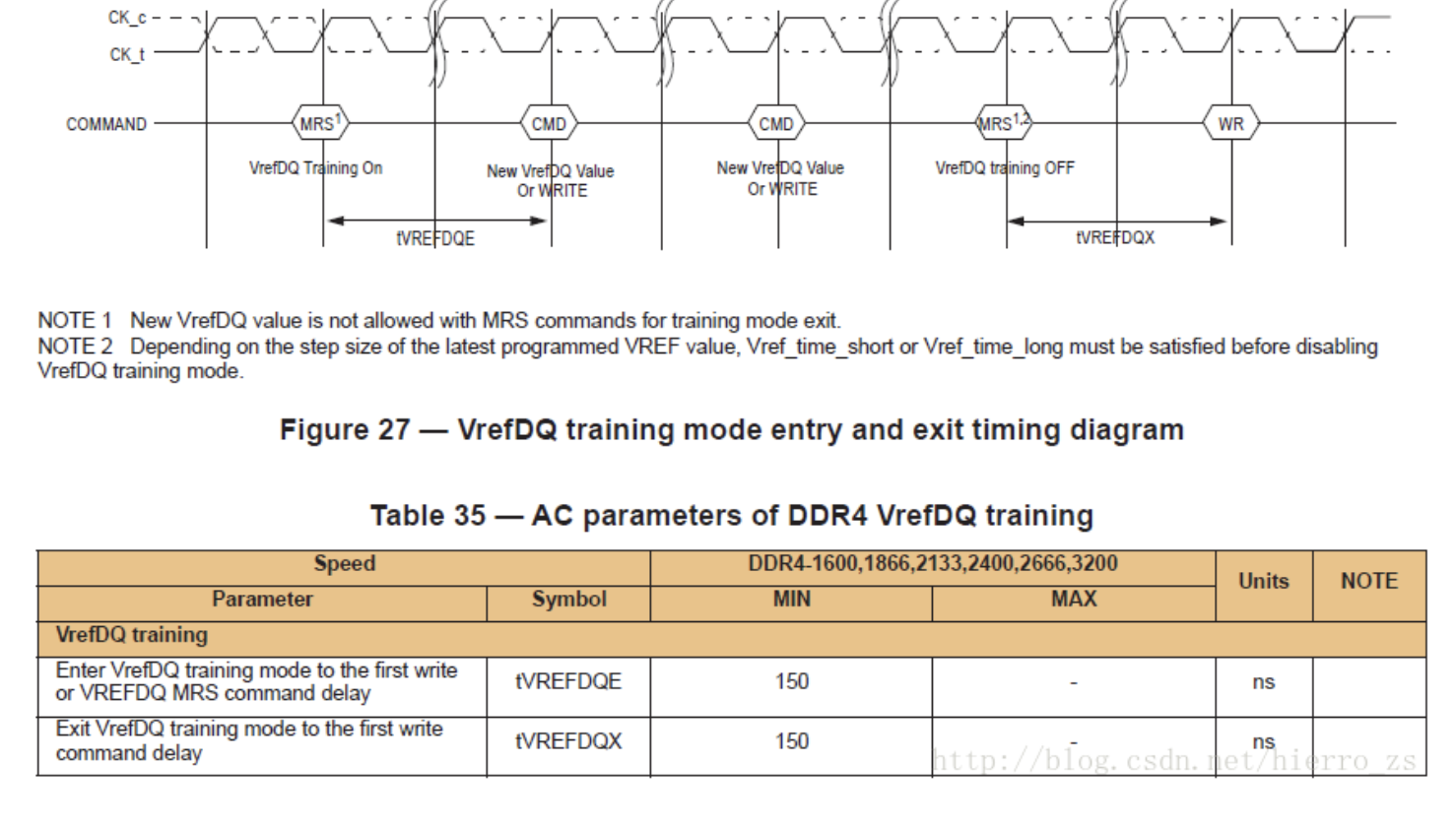

MR6的[5:0]是用来配置vref值,并可通过MRS命令设置此寄存器的[5:0]来改变vref值。VrefDQ训练模式可通过MR6.A7来使能或禁止,训练范围可通过MR6.A6来配置。当进入或退出VrefDQ模式时,需要满足下图中的时序参数,以防止电流消耗与操作的不稳定性。

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.8-4.9)

- JESD79-4 第4章 SDRAM命令描述与操作(4.5-4.7)

- JESD79-4 第4章 SDRAM命令描述与操作(4.1-4.4)

- JESD79-4 第3章 功能描述

- JESD79-4 第2章 DDR4 SDRAM 的引脚封装与寻址

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。