4.14 DRAM单片可寻址能力

DDR4中允许在同一个Rank上对不同的设备进行编程。下面例子中描述了在同一Rank不同设备上对ODT与Vref值分别进行不同配置。

- 在进入DRAM单片可寻址(PDA)模式之前,需要先完成Write Leveling。

- 在进入PDA模式之前,以下配置是可以的。

RTT_PARK MR5 {A8:A6} = Enable

RTT_NOM MR1 {A10:A9:A8} = Enable - 通过将MR3.A4配置为1,来使能PDA模式。

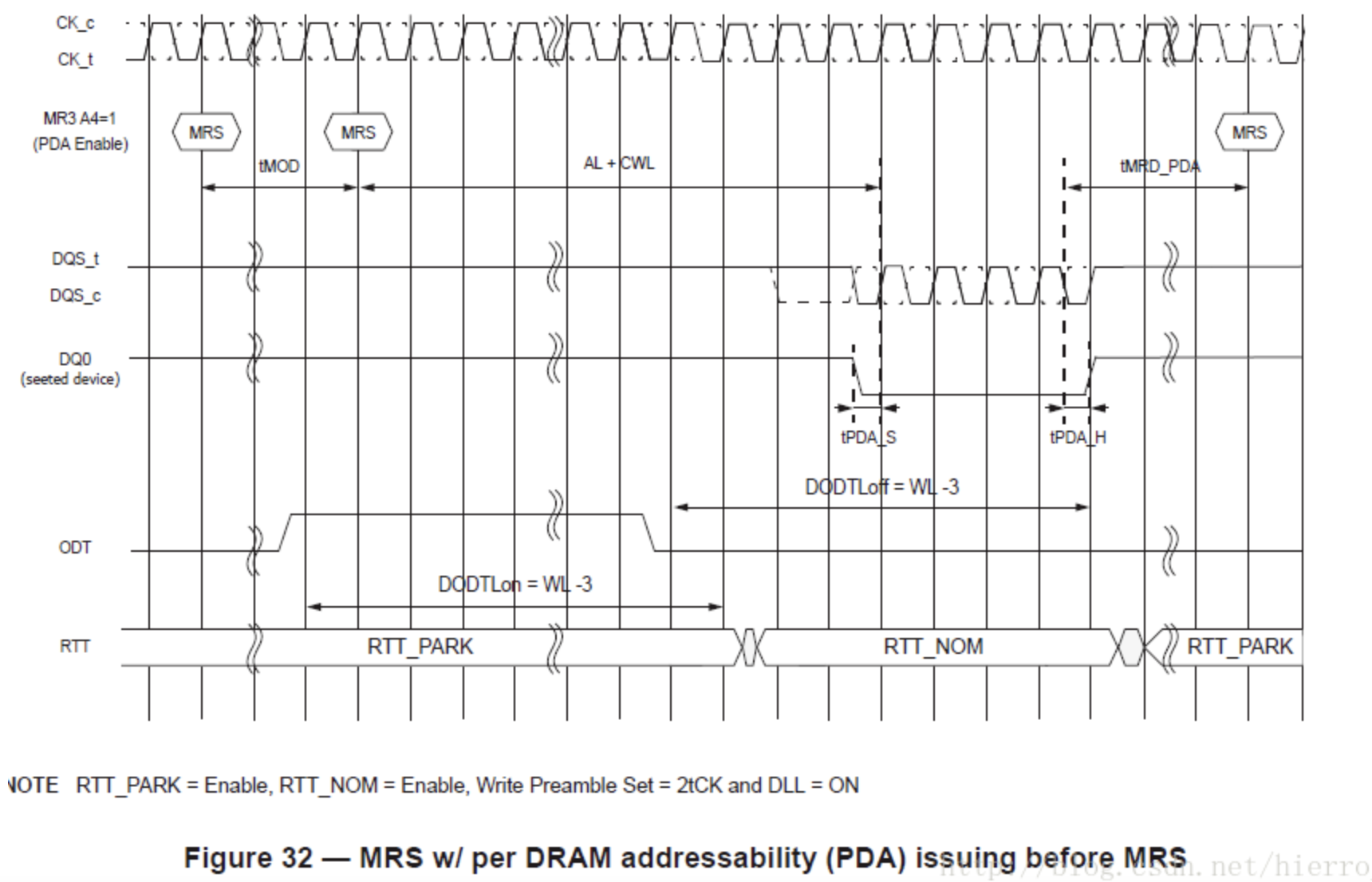

- 在PDA模式中,所有的MRS命令都是通过DQ0来确定有效性的。如下图中所示,DRAM通过DQS_c/DQS_t这对差分信号来采样DQ0信号。若DQ0为0则执行当前的MRS命令,若DQ0为1则忽略当前的MRS命令。控制器可选择性的将所有DQ驱动为同一值。

- 通过MRS命令与DQ0来对期望的设备进行编程。

- 在PDA模式中仅允许执行MRS命令。

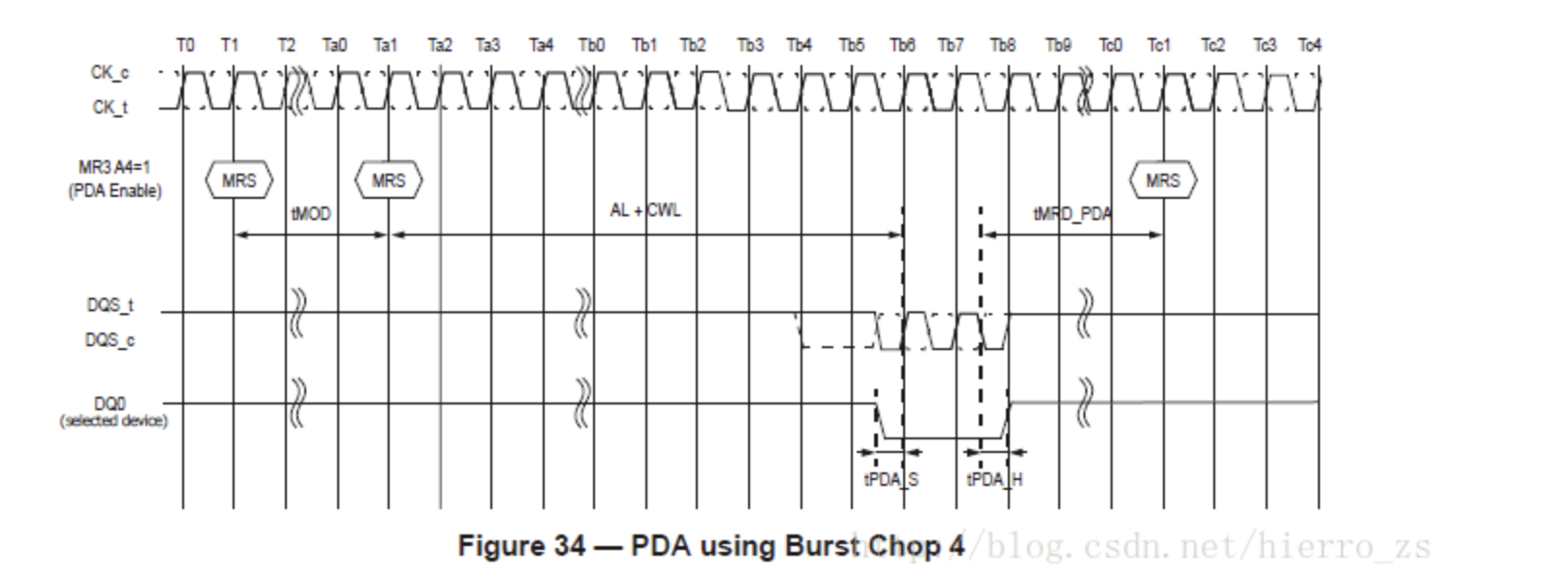

- PDA模式中,MRS命令设定好命令需要的周期。写入一个模式寄存器所需的最小时间与两个MRS命令之间的最小时间都是AL + CWL + 3.5nCK + tMRD_PDA。

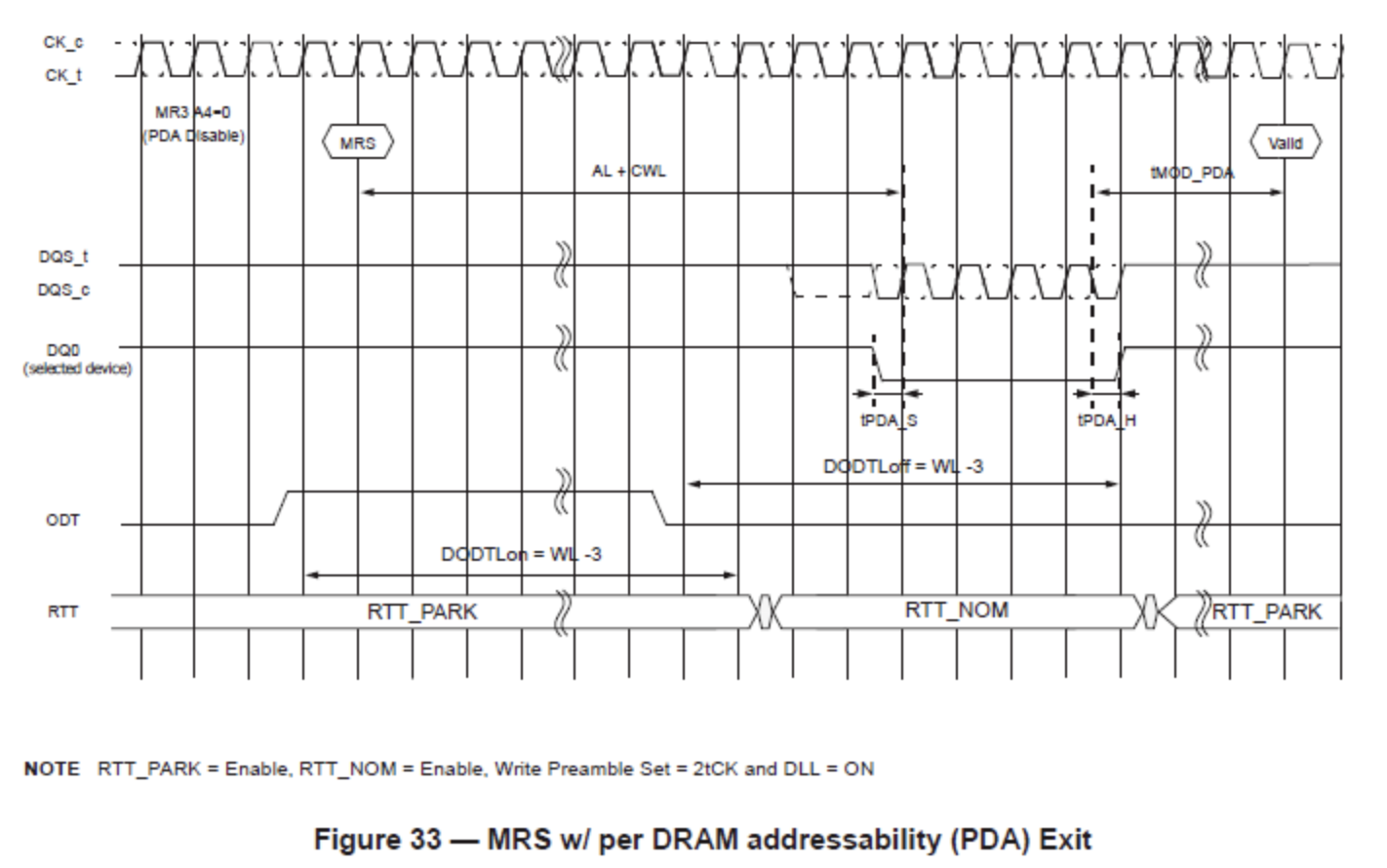

- 如下图所示,退出PDA模式仅需将MR3.A4配置为0,且此时的DQ0需要保持为0。

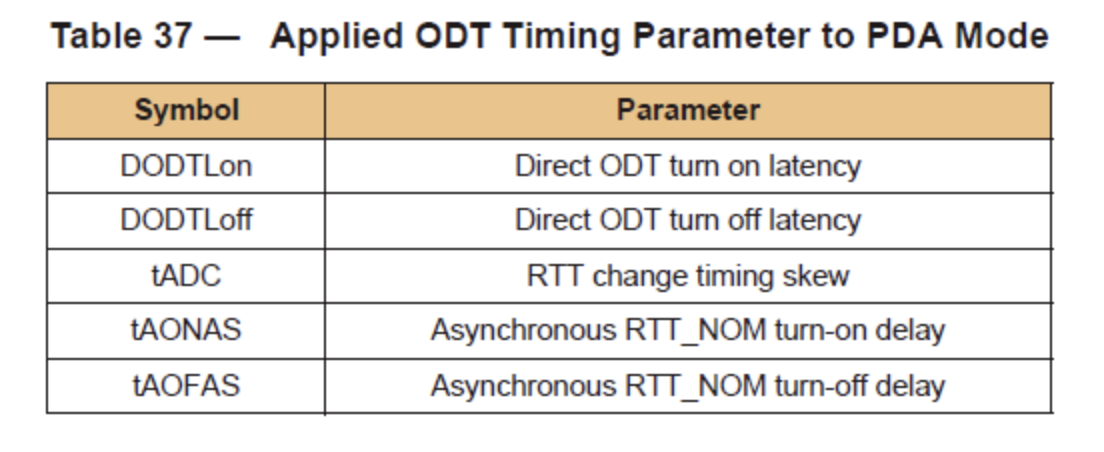

需要注意的是,在退出PDA模式时,由于MRS命令每次需要将所有的模式寄存器值都写一遍,那么在发送退出命令时,会导致在同一Rank上的每个设备都会被影响。因此PDA模式使能位被安排在了一个没有任何DRAM单片控制位的寄存器上。在PDA模式中,DRAM通过DQS_c/DQS_t这对差分信号来采样DQ0信号。但是不支持动态ODT功能。当RTT_NOM MR1 {A10:A9:A8} = Enable且外部关心此时的ODT设置,DDR4 SDRAM的数据终结电阻需要通过ODT引脚来控制。此时的ODT时序参数与直接控制ODT时的参数相同。如下图示。

在所有的DDR4速率中,tPDA_S = tDS 以及 tPDA_H = tDH。

由于在PDA模式中,可能会配置DRAM的最佳vref,这有可能导致在DQS的第一个上升沿与DQS的最后一个下降沿采不到DQ0的正确值。所以推荐在DRAM上,对DQ0进行采样时,使用DQS的第一个下降沿或第二个上升沿。这种采样方法可作为DRAM上针对BL8与BC4的一种通用的实施方案。同时,控制器被要求在BL8或BC4数据有效时间内将DQ0驱动成一个稳定的高电平或低电平。

4.15 CAL模式(CS_n到命令地址的延迟)

4.15.1 CAL模式描述

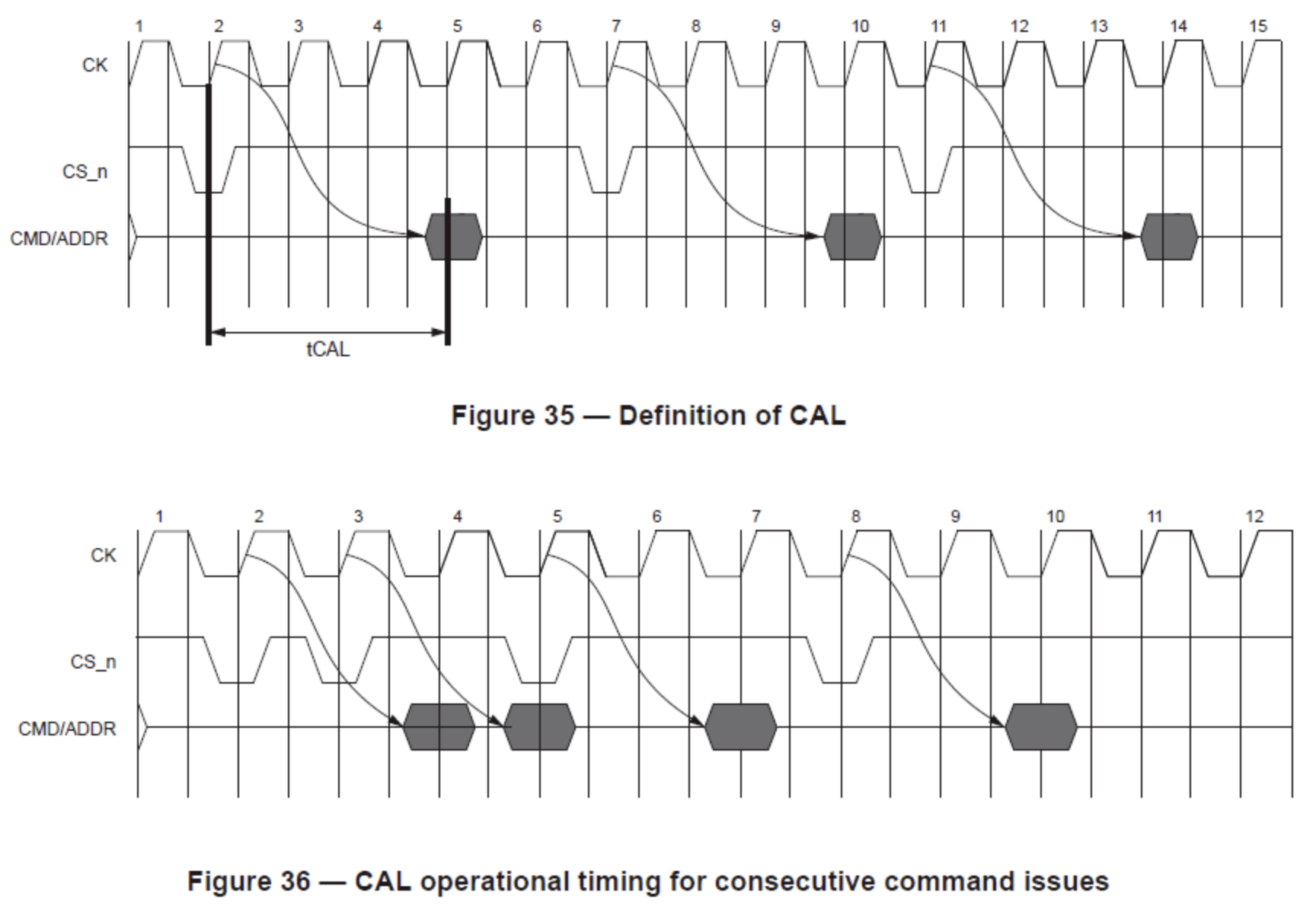

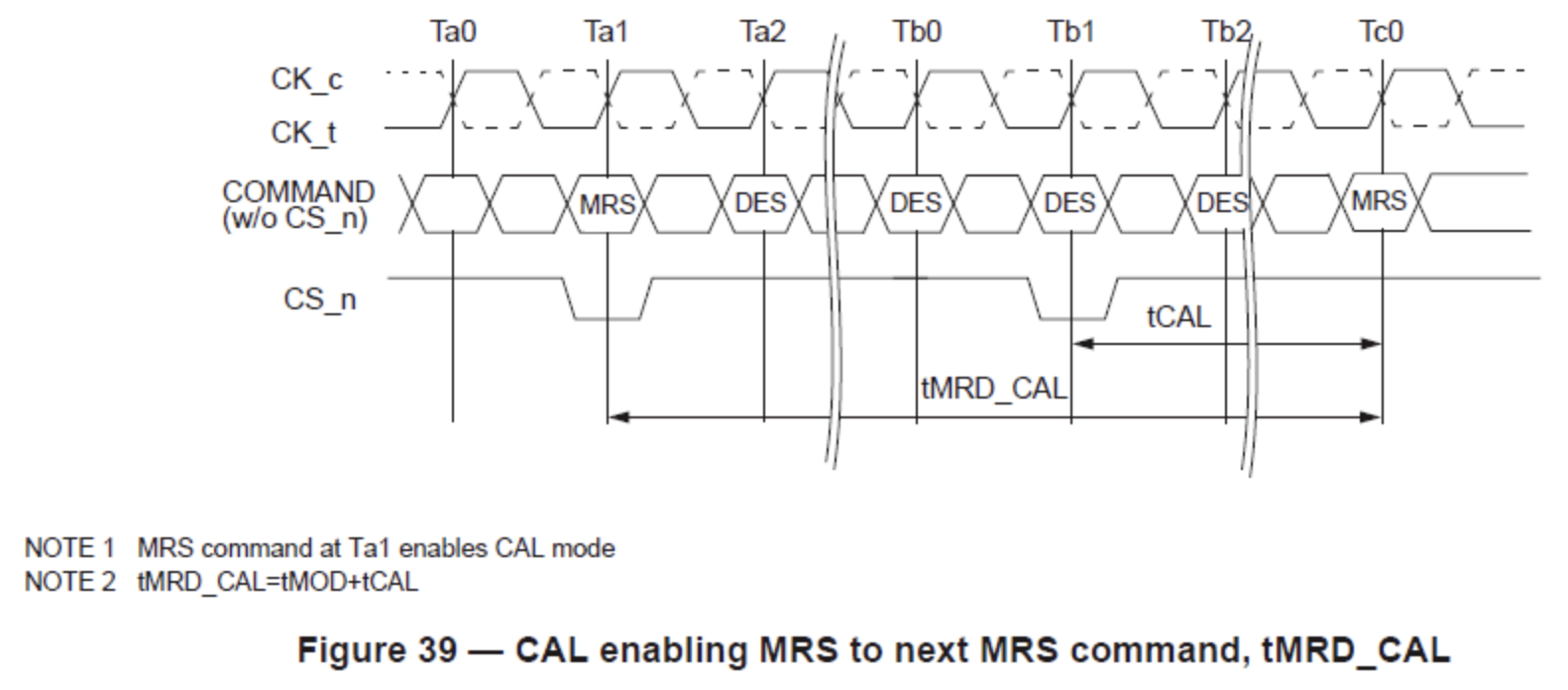

DDR4 SDRAM中支持命令地址延迟功能,此功能作为一种低功耗的功能,可将CS_n信号有效与命令的有效地址时间错开。如下图所示。由模式寄存器MR4[A8:A6]来控制此功能。

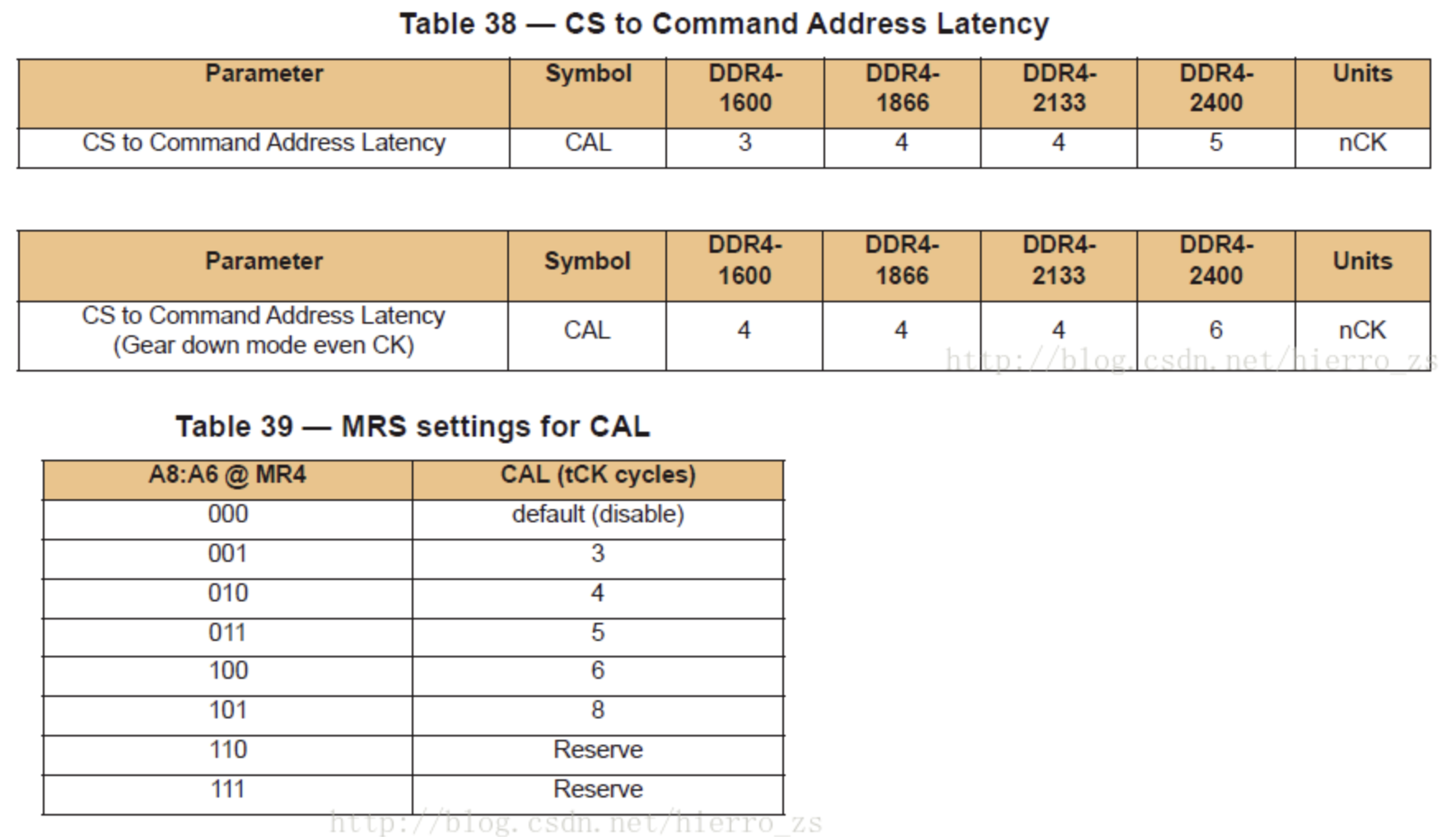

在DRAM上,CAL功能使得命令与地址信号的接收器可在命令到达前的一段时间再打开。且一旦命令与地址已经完成锁存,那么这些信号的接收器也可以关闭了。在连续命令中,接收器会在每个命令之间的空隙时间打开。

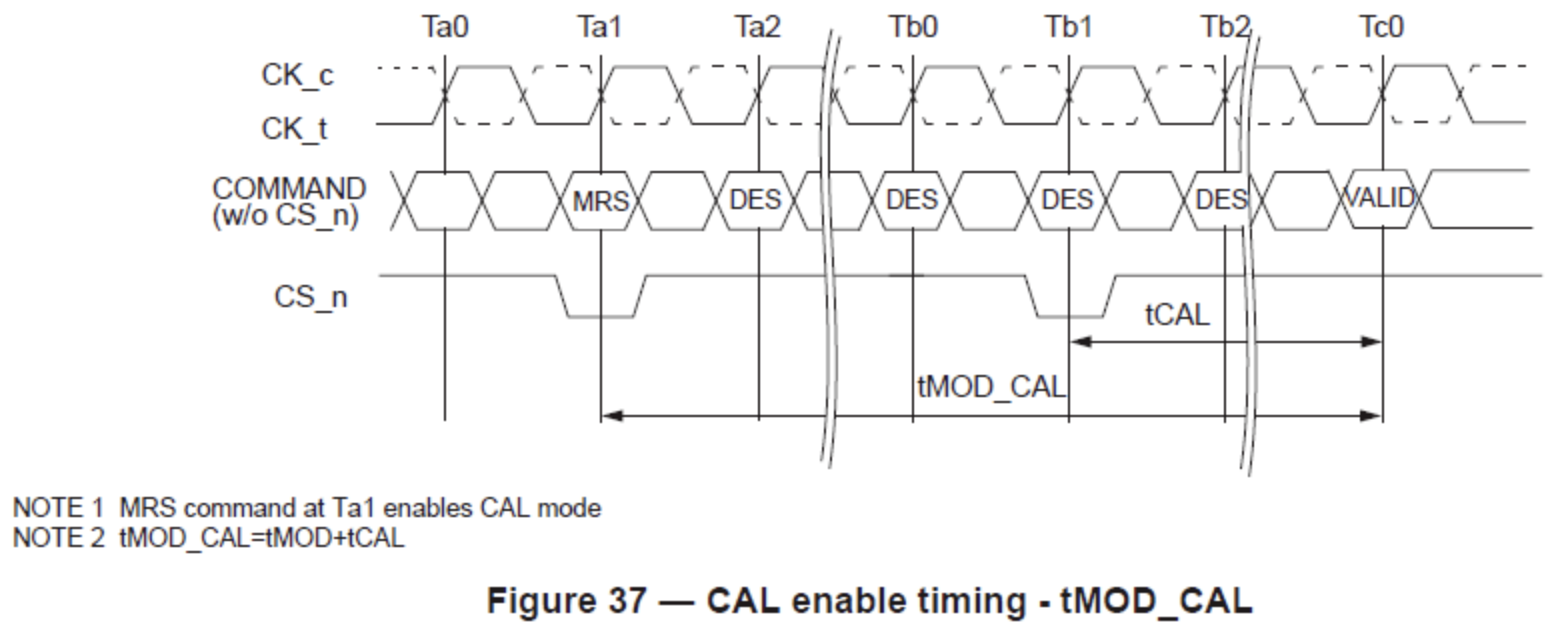

下面表格中的参数为t在各种速率下的CAL的时序要求与MRS设置。

CAL模式使能时的MRS命令

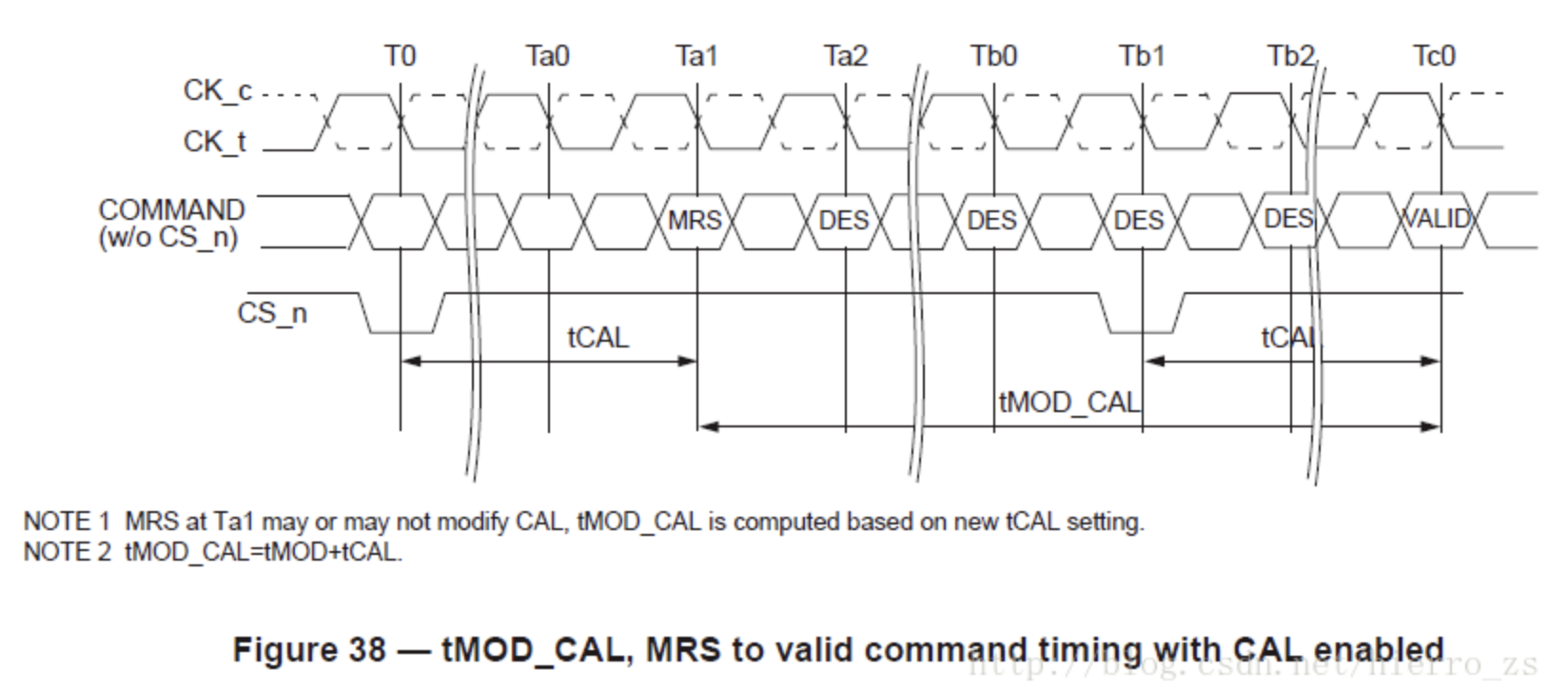

当CAL模式使能时,MRS命令需要更多的时间来完成。当CAL模式已经开启,或通过MRS命令正在开启时,MRS后的第一个有效命令需要遵循时间参数tMOD_CAL=tMOD+tCAL.

处于或正在进入CAL模式时,下一个MRS命令需要遵循时间参数tMRD_CAL=tMOD+tCAL。

4.16 CRC

4.16.1 CRC多项式与逻辑方程式

DDR4 SDRAM中对写操作支持CRC,但对读操作不支持CRC。DDR4中的CRC多项式为:

1 ATM-8 HEC, X^8+X^2+X^1+1对于一个72-bits数据和8-bitsCRC的组合逻辑实现,包含了272个双输入XOR门,组成了8个6 XOR门树深度。(?这句话不是太明白)在DDR4中的CRC多项式与逻辑方程式与GDDR5中的相同。

以下为CRC的代码实现

module CRC8_D72;

// polynomial: (0 1 2 8)

// data width: 72

// convention: the first serial data bit is D[71]

// initial condition all 0 implied

function [7:0]

nextCRC8_D72;

input [71:0] Data;

reg [71:0] D;

reg [7:0] NewCRC;

begin

D = Data;

NewCRC[0] = D[69] ^ D[68] ^ D[67] ^ D[66] ^ D[64] ^ D[63] ^ D[60] ^

D[56] ^ D[54] ^ D[53] ^ D[52] ^ D[50] ^ D[49] ^ D[48] ^

D[45] ^ D[43] ^ D[40] ^ D[39] ^ D[35] ^ D[34] ^ D[31] ^

D[30] ^ D[28] ^ D[23] ^ D[21] ^ D[19] ^ D[18] ^ D[16] ^

D[14] ^ D[12] ^ D[8] ^ D[7] ^ D[6] ^ D[0] ;

NewCRC[1] = D[70] ^ D[66] ^ D[65] ^ D[63] ^ D[61] ^ D[60] ^ D[57] ^

D[56] ^ D[55] ^ D[52] ^ D[51] ^ D[48] ^ D[46] ^ D[45] ^

D[44] ^ D[43] ^ D[41] ^ D[39] ^ D[36] ^ D[34] ^ D[32] ^

D[30] ^ D[29] ^ D[28] ^ D[24] ^ D[23] ^ D[22] ^ D[21] ^

D[20] ^ D[18] ^ D[17] ^ D[16] ^ D[15] ^ D[14] ^ D[13] ^

D[12] ^ D[9] ^ D[6] ^ D[1] ^ D[0];

NewCRC[2] = D[71] ^ D[69] ^ D[68] ^ D[63] ^ D[62] ^ D[61] ^ D[60] ^

D[58] ^ D[57] ^ D[54] ^ D[50] ^ D[48] ^ D[47] ^ D[46] ^

D[44] ^ D[43] ^ D[42] ^ D[39] ^ D[37] ^ D[34] ^ D[33] ^

D[29] ^ D[28] ^ D[25] ^ D[24] ^ D[22] ^ D[17] ^ D[15] ^

D[13] ^ D[12] ^ D[10] ^ D[8] ^ D[6] ^ D[2] ^ D[1] ^ D[0];

NewCRC[3] = D[70] ^ D[69] ^ D[64] ^ D[63] ^ D[62] ^ D[61] ^ D[59] ^

D[58] ^ D[55] ^ D[51] ^ D[49] ^ D[48] ^ D[47] ^ D[45] ^

D[44] ^ D[43] ^ D[40] ^ D[38] ^ D[35] ^ D[34] ^ D[30] ^

D[29] ^ D[26] ^ D[25] ^ D[23] ^ D[18] ^ D[16] ^ D[14] ^

D[13] ^ D[11] ^ D[9] ^ D[7] ^ D[3] ^ D[2] ^ D[1];

NewCRC[4] = D[71] ^ D[70] ^ D[65] ^ D[64] ^ D[63] ^ D[62] ^ D[60] ^

D[59] ^ D[56] ^ D[52] ^ D[50] ^ D[49] ^ D[48] ^ D[46] ^

D[45] ^ D[44] ^ D[41] ^ D[39] ^ D[36] ^ D[35] ^ D[31] ^

D[30] ^ D[27] ^ D[26] ^ D[24] ^ D[19] ^ D[17] ^ D[15] ^

D[14] ^ D[12] ^ D[10] ^ D[8] ^ D[4] ^ D[3] ^ D[2];

NewCRC[5] = D[71] ^ D[66] ^ D[65] ^ D[64] ^ D[63] ^ D[61] ^ D[60] ^

D[57] ^ D[53] ^ D[51] ^ D[50] ^ D[49] ^ D[47] ^ D[46] ^

D[45] ^ D[42] ^ D[40] ^ D[37] ^ D[36] ^ D[32] ^ D[31] ^

D[28] ^ D[27] ^ D[25] ^ D[20] ^ D[18] ^ D[16] ^ D[15] ^

D[13] ^ D[11] ^ D[9] ^ D[5] ^ D[4] ^ D[3];

NewCRC[6] = D[67] ^ D[66] ^ D[65] ^ D[64] ^ D[62] ^ D[61] ^ D[58] ^

D[54] ^ D[52] ^ D[51] ^ D[50] ^ D[48] ^ D[47] ^ D[46] ^

D[43] ^ D[41] ^ D[38] ^ D[37] ^ D[33] ^ D[32] ^ D[29] ^

D[28] ^ D[26] ^ D[21] ^ D[19] ^ D[17] ^ D[16] ^ D[14] ^

D[12] ^ D[10] ^ D[6] ^ D[5] ^ D[4];

NewCRC[7] = D[68] ^ D[67] ^ D[66] ^ D[65] ^ D[63] ^ D[62] ^ D[59] ^

D[55] ^ D[53] ^ D[52] ^ D[51] ^ D[49] ^ D[48] ^ D[47] ^

D[44] ^ D[42] ^ D[39] ^ D[38] ^ D[34] ^ D[33] ^ D[30] ^

D[29] ^ D[27] ^ D[22] ^ D[20] ^ D[18] ^ D[17] ^ D[15] ^

D[13] ^ D[11] ^ D[7] ^ D[6] ^ D[5];

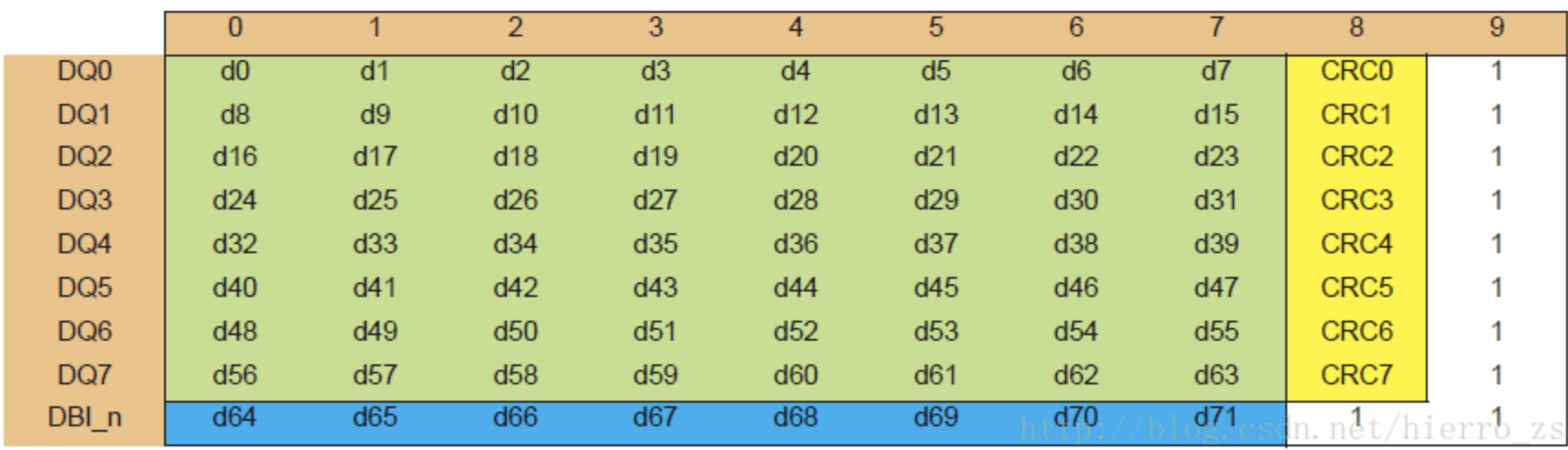

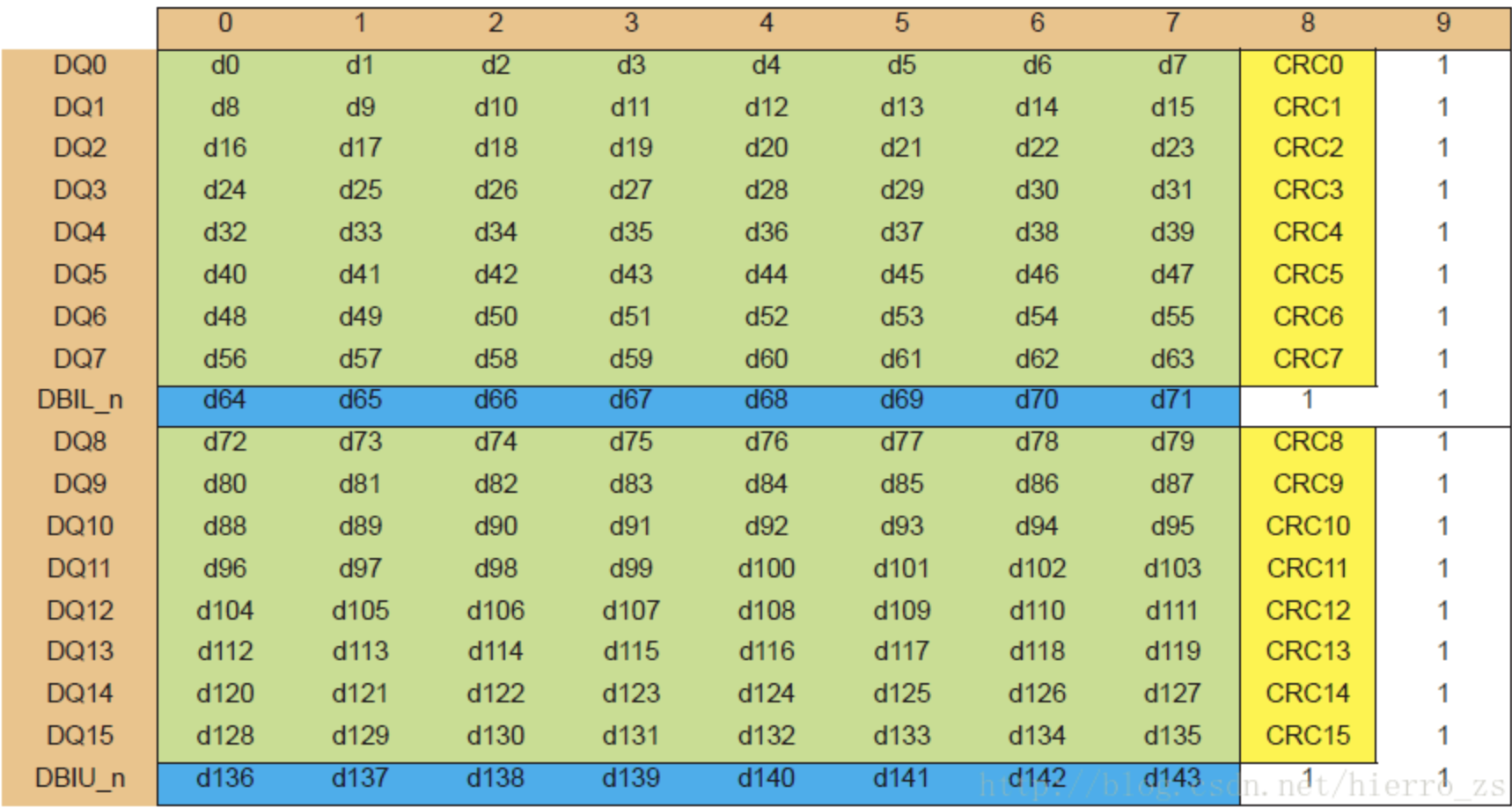

nextCRC8_D72 = NewCRC;4.16.2 x8设备的CRC数据位映射

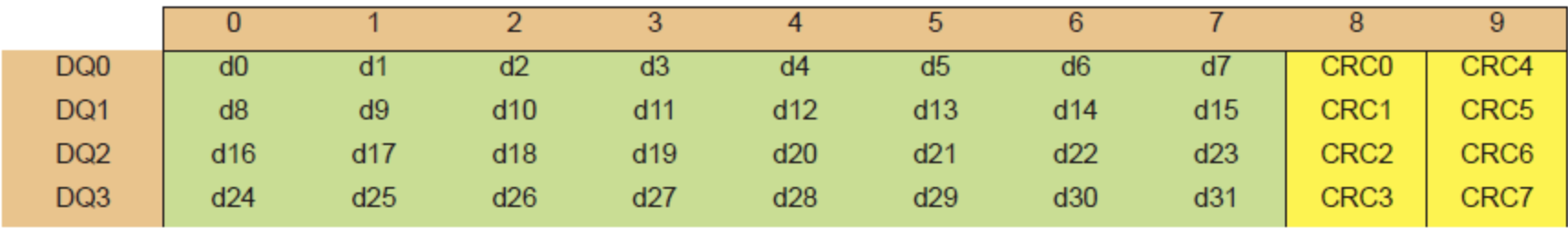

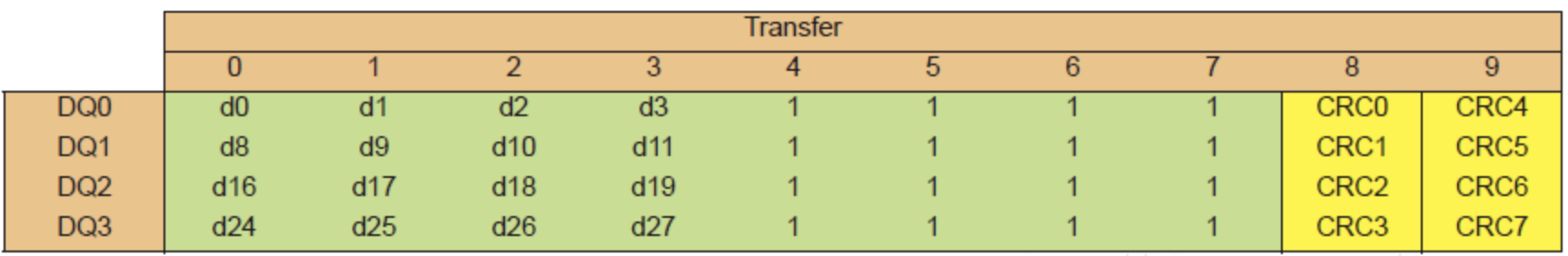

4.16.3 x4设备的CRC数据位映射

4.16.4 x16设备的CRC数据位映射

4.16.5 x4,x8,x16设备写操作的CRC

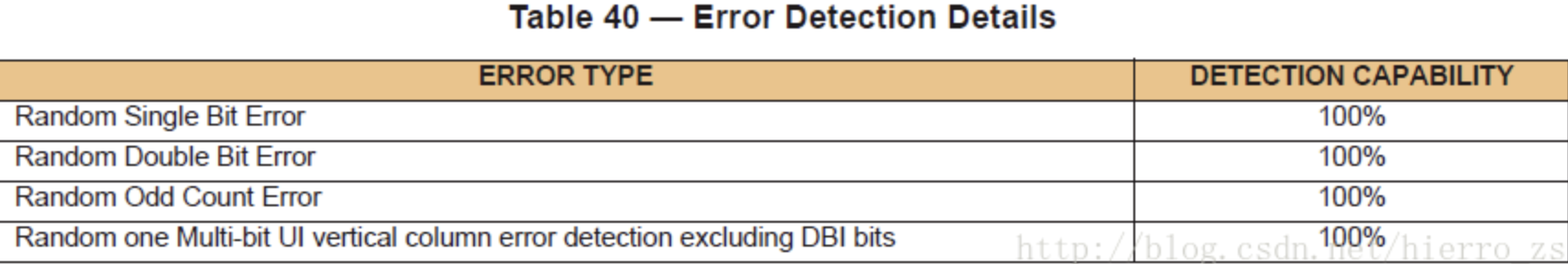

控制器按照章节4.16.1到4.16.4中的描述来生成CRC校验和,以及写数据结构。

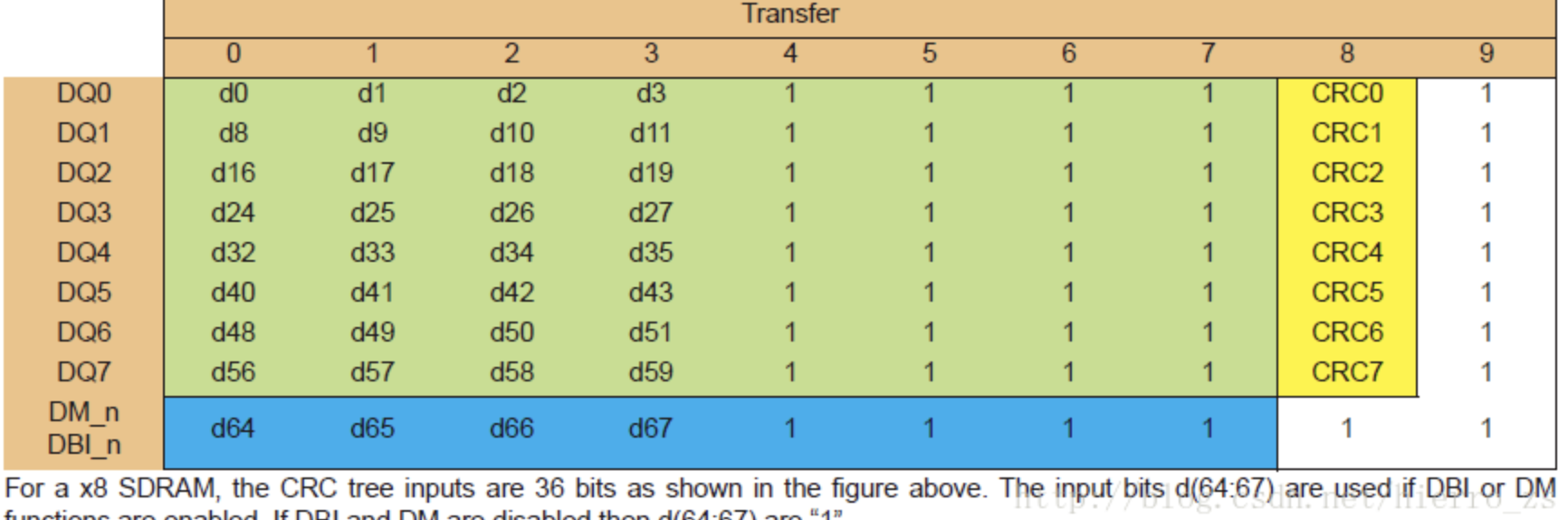

在x8与x16设备中,当CRC功能开启时,每9位数据至少需要一个1。在DBI功能启动时,一位CRC可校验9位数据,否则一位CRC校验8位数据。

当控制器收到返回的72位数据时,根据计算得到的CRC校验和可与返回的校验和进行比较,如果遇到校验错误,则通过将ALERT_n信号拉高来报告错误。

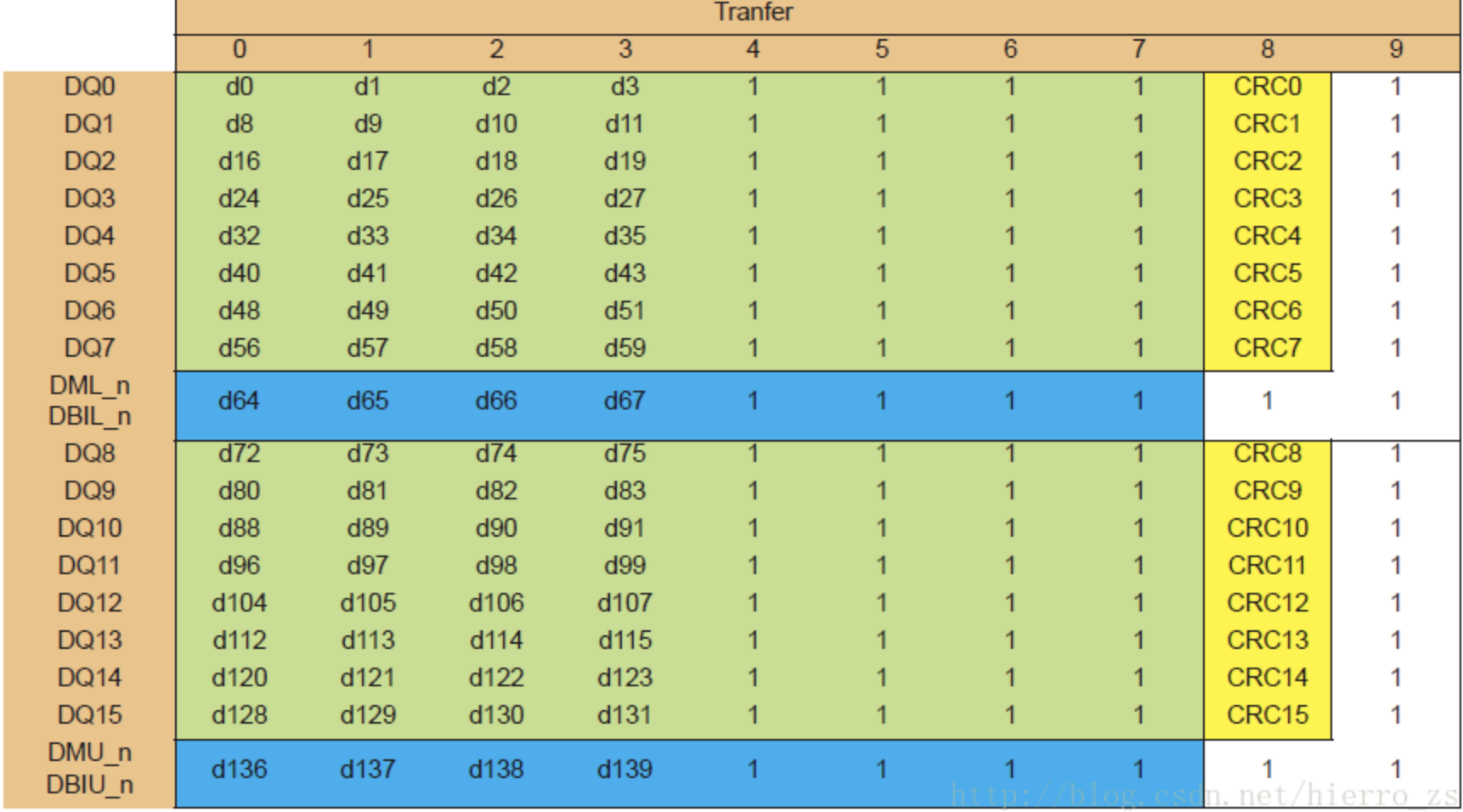

在x8设备中,若数据为72位,当DBI功能开启时,数据的高8位为DBI信号;当DBI功能关闭时,数据的高8位必须为全1。在x16设备中,每72位数据中都有一套相同的且独立的CRC树,与x8类似,当DBI功能开启时,D[71:64]与D[143:136]为DBI信号;当DBI功能关闭时,D[71:64]与D[143:136]必须为全1。对于32位数据输入的x4器件,输入的高40位D[71:32]都为1。

DRAM会直接将写数据写入阵列,即使DRAM core没有完成CRC校验。如果CRC校验发生错误,那么需要控制器重新写入并覆盖错误数据,数据的一致性需要由控制器来保证。

4.16.6 RC错误的处理

在校验写入SDRAM的CRC报错机制中,ALERT_n作为错误信号,同时命令与地址奇偶校验(Parity)也使用了此信号。当ALERT_n信号有效时,控制器无法直接判断此时是哪一种错误,除非通过查询模式寄存器来获取错误信息。

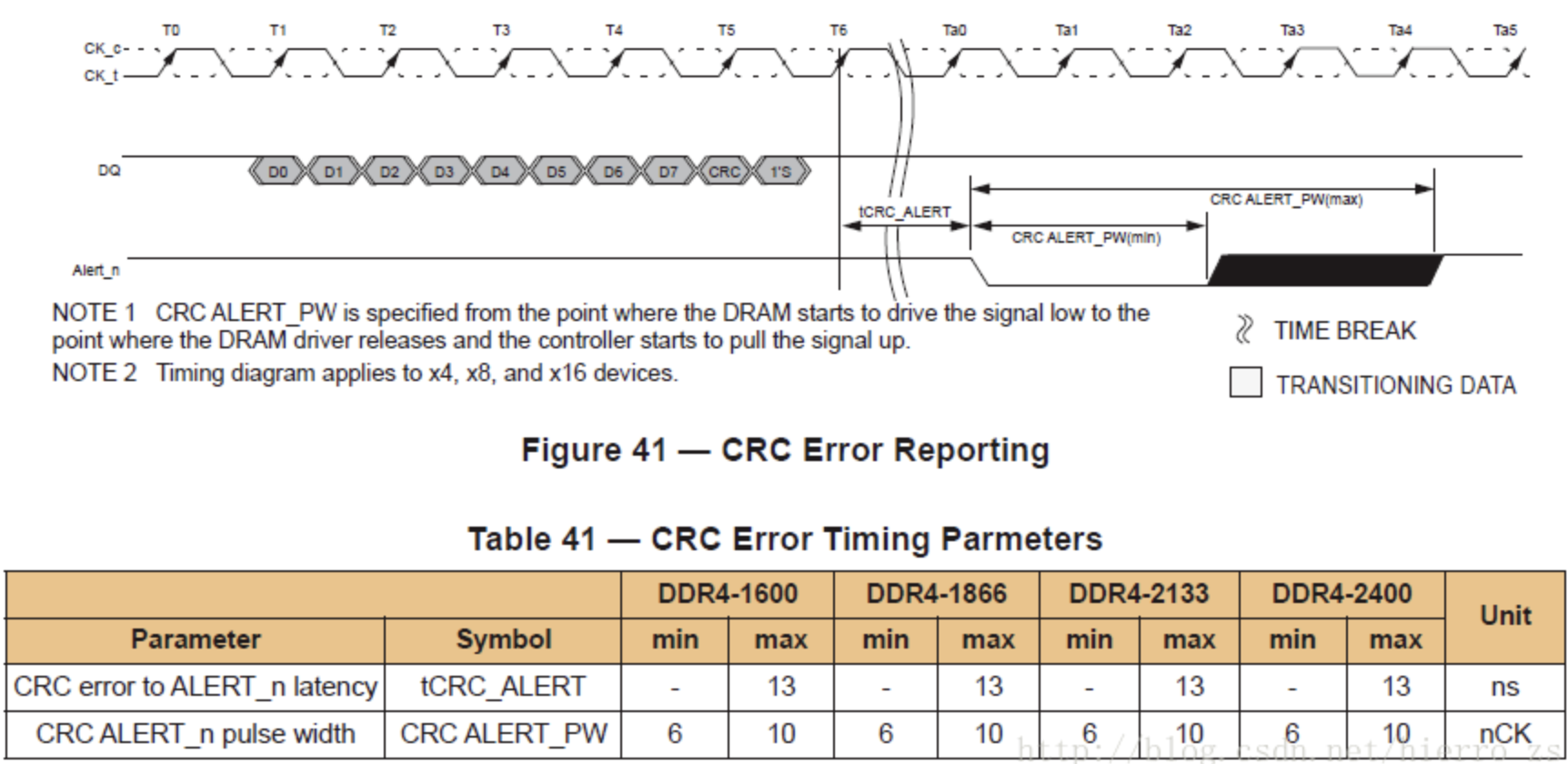

为了尽快恢复CRC错误,CRC错误仅保持一个脉冲。最小脉冲宽度为2个时钟周期。ALERT_n信号的延迟遵循时序参数tCRC_ALERT,如下图所示。

MR5.A4为CRC错误清除位。MR3的page 1中包含了CRC错误的状态位,当出现CRC错误时,相关状态位将变为1。CRC错误清除位将保持为1,除非用户通过MRS命令来配置此位。

控制器若检测到CRC错误脉冲,将重新执行错误的写命令。控制器能够通过初始化了解ALERT_n信号的最大延迟,并对每一次的读写操作进行备份,或更加智能,将写CRC错误关联到一个特殊的Rank或传输。控制器需要保证在打开不同的page或重启的写操作完成时的一致性。

在控制器端看到的ALERT_n脉冲有肯能大于两个周期,当多个连续的CRC错误出现时,ALERT_n信号可能形成一个链。

4.16.7 BC4中的CRC结果格式

DDR4 SDRAM中的BC4写操作支持CRC校验。CRC可通过模式寄存器开启,并在写操作时进行校验操作。

当CRC校验开启的数据结构格式为固定10个UI,同时对BL8与BC4有效时。DDR4 SDRAM可支持Burst Length OTF的CRC校验。此功能可通过模式寄存器开启。

在x4设备的BC4中,数据映射关系如下图。

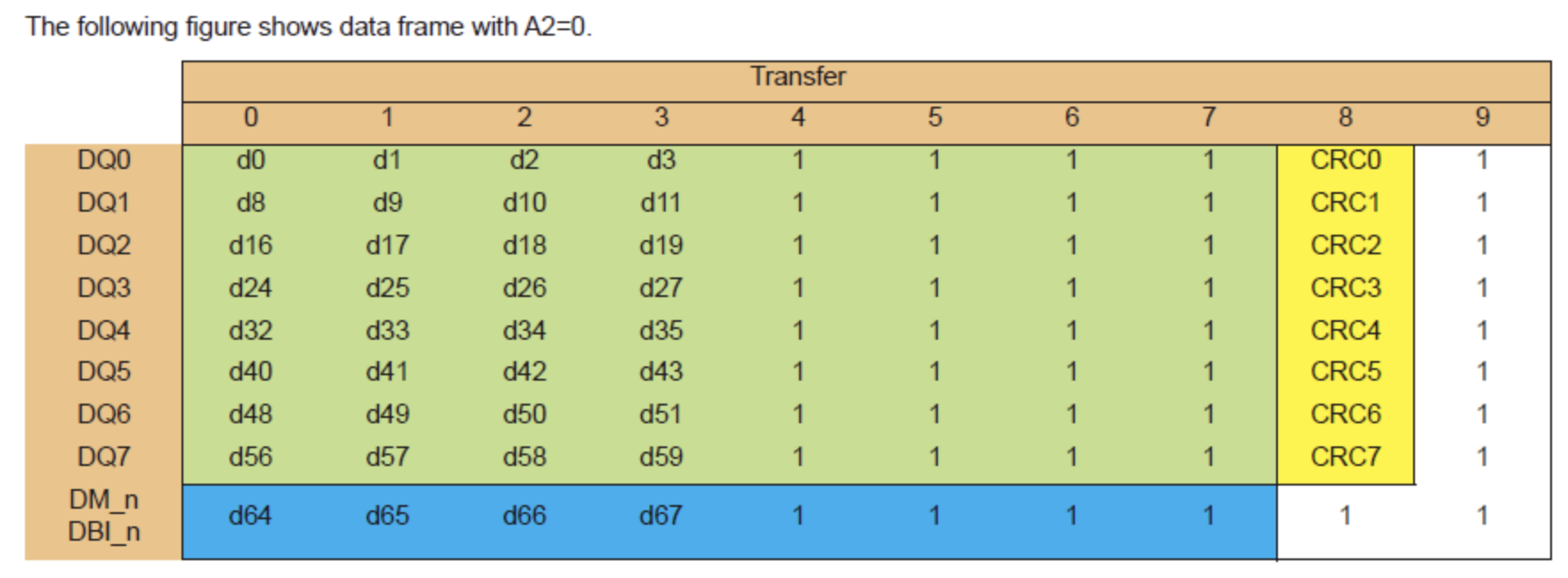

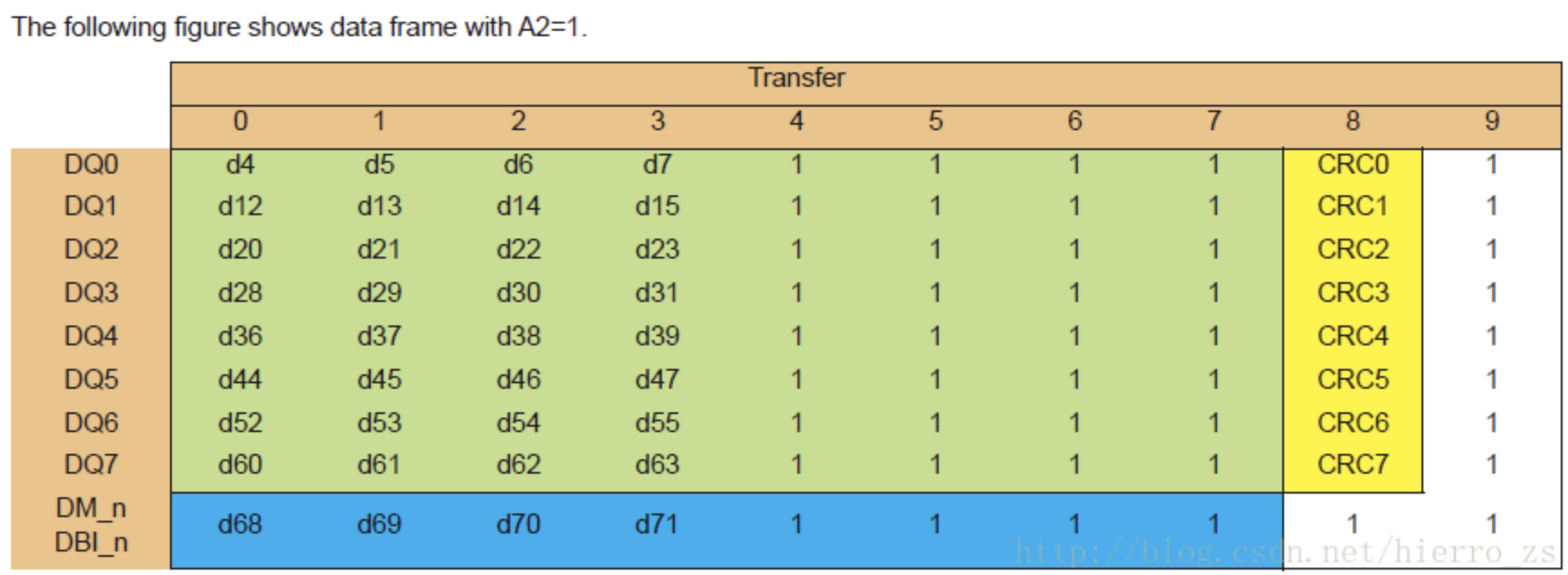

在x8设备的BC4中,数据映射关系如下图。

在x16设备的BC4中,数据映射关系如下图。

x16设备中有两个相同且独立的CRC树。低位的CRC树有36位输入数据,如下图所示。当DBI功能开启时,D[63:67]作为DBI信号使用,当DBI功能关闭时,D[64:67]必须为全1。高位的CRC树有36位输入数据,如下图所示。当DBI功能开启时,D[136:139]作为DBI信号使用,当DBI功能关闭时,D[136:139]必须为全1。

DBI与CRC验证

写操作,SDRAM会计算接受到的CRC码与D[71:0]数据。在进行CRC计算之前数据不会根据DBI信号而翻转,等到真正写入SDRAM阵列的时候则会根据DBI信号来对数据进行相应的翻转。

CRC开启时的BC4突发顺序

当CRC开启,A2作为BC4写操作的第一个数据地址使用,下表中描述了BC4时,且DBI功能开启的数据结构。

x8设备中的BC4的逻辑等式如下所示(A2=0)

CRC[0] = D[69]=1 ^ D[68]=1 ^ D[67] ^ D[66] ^ D[64] ^ D[63]=1 ^ D[60]=1 ^ D[56] ^ D[54]=1 ^ D[53]=1 ^ D[52]=1 ^ D[50] ^ D[49] ^ D[48] ^ D[45]=1 ^ D[43] ^ D[40] ^ D[39]=1 ^ D[35] ^ D[34] ^ D[31]=1 ^ D[30]=1 ^ D[28]=1 ^ D[23]=1 ^ D[21]=1 ^ D[19] ^ D[18] ^ D[16] ^ D[14]=1 ^ D[12]=1 ^ D[8] ^ D[7]=1 ^ D[6] =1 ^ D[0] ;

CRC[1] = D[70]=1 ^ D[66] ^ D[65] ^ D[63]=1 ^ D[61]=1 ^ D[60]=1 ^ D[57] ^ D[56] ^ D[55]=1 ^ D[52]=1 ^ D[51] ^ D[48] ^ D[46]=1 ^ D[45]=1 ^ D[44]=1 ^ D[43] ^ D[41] ^ D[39]=1 ^ D[36]=1 ^ D[34] ^ D[32] ^ D [30]=1 ^ D[29]=1 ^ D[28]=1 ^ D[24] ^ D[23]=1 ^ D[22]=1 ^ D[21]=1 ^ D[20]=1 ^ D[18] ^ D[17] ^ D[16] ^ D[15]=1 ^ D[14]=1 ^ D[13]=1 ^ D[12]=1 ^ D[9] ^ D[6]=1 ^ D[1] ^ D[0];

CRC[2] = D[71]=1 ^ D[69]=1 ^ D[68]=1 ^ D[63]=1 ^ D[62]=1 ^ D[61]=1 ^ D[60]=1 ^ D[58] ^ D[57] ^ D[54]=1 ^ D[50] ^ D[48] ^ D[47]=1 ^ D[46]=1 ^ D[44]=1 ^ D[43] ^ D[42] ^ D[39]=1 ^ D[37]=1 ^ D[34] ^ D[33] ^ D[29]=1 ^ D[28]=1 ^ D[25] ^ D[24] ^ D[22]=1 ^ D[17] ^ D[15]=1 ^ D[13]=1 ^ D[12]=1 ^ D[10] ^ D[8] ^ D[6]=1 ^ D[2] ^ D[1]

^ D[0];

CRC[3] = D[70]=1 ^ D[69]=1 ^ D[64] ^ D[63]=1 ^ D[62]=1 ^ D[61]=1 ^ D[59] ^ D[58] ^ D[55]=1 ^ D[51] ^ D[49] ^ D[48] ^ D[47]=1 ^ D[45]=1 ^ D[44]=1 ^ D[43] ^ D[40] ^ D[38]=1 ^ D[35] ^ D[34] ^ D[30]=1 ^ D[29]=1 ^ D[26] ^ D[25] ^ D[23]=1 ^ D[18] ^ D[16] ^ D[14]=1 ^ D[13]=1 ^ D[11] ^ D[9] ^ D[7]=1 ^ D[3] ^ D[2] ^ D[1];

CRC[4] = D[71]=1 ^ D[70]=1 ^ D[65] ^ D[64] ^ D[63]=1 ^ D[62]=1 ^ D[60]=1 ^ D[59] ^ D[56] ^ D[52]=1 ^ D[50] ^ D[49] ^ D[48] ^ D[46]=1 ^ D[45]=1 ^ D[44]=1 ^ D[41] ^ D[39]=1 ^ D[36]=1 ^ D[35] ^ D[31]=1 ^ D[30]=1 ^ D[27] ^ D[26] ^ D[24] ^ D[19] ^ D[17] ^ D[15]=1 ^ D[14]=1 ^ D[12]=1 ^ D[10] ^ D[8] ^ D[4]=1 ^ D[3] ^ D[2];

CRC[5] = D[71]=1 ^ D[66] ^ D[65] ^ D[64] ^ D[63]=1 ^ D[61]=1 ^ D[60]=1 ^ D[57] ^ D[53]=1 ^ D[51] ^ D[50] ^ D[49] ^ D[47]=1 ^ D[46]=1 ^ D[45]=1 ^ D[42] ^ D[40] ^ D[37]=1 ^ D[36]=1 ^ D[32] ^ D[31]=1 ^ D[28]=1 ^ D[27] ^ D[25] ^ D[20]=1 ^ D[18] ^ D[16] ^ D[15]=1 ^ D[13]=1 ^ D[11] ^ D[9] ^ D[5]=1 ^ D[4]=1 ^ D[3];

CRC[6] = D[67] ^ D[66] ^ D[65] ^ D[64] ^ D[62]=1 ^ D[61]=1 ^ D[58] ^ D[54]=1 ^ D[52]=1 ^ D[51] ^ D[50] ^ D[48] ^ D[47]=1 ^ D[46]=1 ^ D[43] ^ D[41] ^ D[38]=1 ^ D[37]=1 ^ D[33] ^ D[32] ^ D[29]=1 ^ D[28]=1 ^ D[26] ^ D[21]=1 ^ D[19] ^ D[17] ^ D[16] ^ D[14]=1 ^ D[12]=1 ^ D[10] ^ D[6]=1 ^ D[5]=1 ^ D[4]=1;

CRC[7] = D[68]=1 ^ D[67] ^ D[66] ^ D[65] ^ D[63]=1 ^ D[62]=1 ^ D[59] ^ D[55]=1 ^ D[53]=1 ^ D[52]=1 ^ D[51] ^ D[49] ^ D[48] ^ D[47]=1 ^ D[44]=1 ^ D[42] ^ D[39]=1 ^ D[38]=1 ^ D[34] ^ D[33] ^ D[30]=1 ^ D [29]=1 ^ D[27] ^ D[22]=1 ^ D[20]=1 ^ D[18] ^ D[17] ^ D[15] =1^ D[13]=1 ^ D[11] ^ D[7]=1 ^ D[6]=1 ^ D[5]=1;x8设备中的BC4的逻辑等式如下所示(A2=1)

CRC[0] = 1 ^ 1 ^ D[71] ^ D[70] ^ D[68] ^ 1 ^ 1 ^ D[60] ^ 1 ^ 1 ^ 1 ^ D[54] ^ D[53] ^ D[52] ^ 1 ^ D[47] ^ D[44] ^ 1 ^ D[39] ^ D[38] ^ 1^ 1 ^ 1 ^ 1 ^ 1 ^ D[23] ^ D[22] ^ D[20] ^ 1 ^ 1 ^ D[12] ^ 1 ^ 1 ^ D[4] ;

CRC[1] = 1 ^ D[70] ^ D[69] ^ 1 ^ 1 ^ 1 ^ D[61] ^ D[60] ^ 1 ^ 1 ^ D[55] ^ D[52] ^ 1 ^ 1 ^ 1 ^ D[47] ^ D[45] ^ 1 ^ 1 ^ D[38] ^ D[36] ^ 1 ^ 1 ^ 1 ^ D[28] ^ 1 ^ 1 ^ 1 ^ 1 ^ D[22] ^ D[21] ^ D[20] ^1 ^ 1 ^1 ^ 1 ^ D[13] ^ 1 ^ D[5] ^ D[4];

CRC[2] = 1 ^ 1 ^ 1 ^1 ^1 ^ 1 ^ 1 ^ D[62] ^ D[61] ^ 1 ^ D[54] ^ D[52] ^ 1 ^ 1 ^ 1 ^ D[47] ^ D[46] ^ 1 ^ 1 ^ D[38] ^ D[37] ^ 1 ^ 1 ^ D[29] ^ D[28] ^ 1 ^ D[21] ^ 1 ^ 1 ^ 1 ^ D[14] ^ D12] ^1 ^ D[6] ^ D[5] ^ D[4];

CRC[3] = 1 ^ 1 ^ D[68] ^ 1 ^ 1 ^ 1 ^ D[63] ^ D[62] ^ 1 ^ D[55] ^ D[53] ^ D[52] ^ 1 ^ 1 ^ 1 ^ D[47] ^ D[44] ^ 1 ^ D[39] ^ D[38] ^ 1 ^ 1 ^ D[30] ^ D[29] ^ 1 ^ D[22] ^ D[20] ^ 1 ^ 1 ^ D[15] ^ D[13] ^ 1 ^ D[7] ^ D[6] ^ D[5];

CRC[4] = 1 ^1 ^ D[69] ^ D[68] ^ 1 ^ 1 ^ 1 ^ D[63] ^ D[60] ^ 1 ^ D[54] ^ D[53] ^ D[52] ^ 1 ^1 ^ 1 ^ D[45] ^ 1 ^ 1 ^ D[39] ^1 ^ 1 ^ D[31] ^ D[30] ^ D[28] ^ D[23] ^ D[21] ^ 1 ^ 1 ^ 1 ^ D[14] ^ D[12] ^ 1 ^ D[7] ^ D[6];

CRC[5] = 1 ^ D[70] ^ D[69] ^ D[68] ^ 1 ^ 1 ^ 1 ^ D[61] ^ 1 ^ D[55] ^ D[54] ^ D[53] ^ 1 ^ 1 ^ 1 ^ D[46] ^ D[44] ^ 1 ^ 1 ^ D[36] ^ 1 ^ 1 D[31] ^ D[29] ^ 1 ^ D[22] ^ D[20] ^ 1 ^ 1 ^ D[15] ^ D[13] ^ 1 ^ 1 ^ D[7];

CRC[6] = D[71] ^ D[70] ^ D[69] ^ D[68] ^ 1 ^ 1 ^ D[62] ^ 1 ^ 1 ^ D[55] ^ D[54] ^ D[52] ^ 1 ^1 ^ D[47] ^ D[45] ^ 1 ^ 1 ^ D[37] ^ D[36] ^1 ^ 1 ^ D[30] ^ 1 ^ D[23] ^ D[21] ^ D[20] ^ 1 ^ 1 ^ D[14] ^ 1 ^ 1 ^ 1;

CRC[7] = 1 ^ D[71] ^ D[70] ^ D[69] ^ 1 ^ 1 ^ D[63] ^ 1 ^ 1 ^ 1 ^ D[55] ^ D[53] ^ D[52] ^ 1 ^ 1 ^ D[46] ^ 1 ^ 1 ^ D[38] ^ D[37] ^ 1 ^ 1 ^ D[31] ^ 1 ^ 1 ^ D[22] ^ D[21] ^ 1^ 1 ^ D[15] ^ 1 ^ 1 ^ 1;4.16.8 DM功能与CRC校验同时开启

当DM与CRC同时开启时,DRAM会在写入存储阵列之前先进行CRC校验,一旦CRC校验出现错误,DRAM会阻塞当前的写请求,并丢弃当前的写数据。

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.11-4.13)

- JESD79-4 第4章 SDRAM命令描述与操作(4.8-4.9)

- JESD79-4 第4章 SDRAM命令描述与操作(4.5-4.7)

- JESD79-4 第4章 SDRAM命令描述与操作(4.1-4.4)

- JESD79-4 第3章 功能描述

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。