3 功能描述

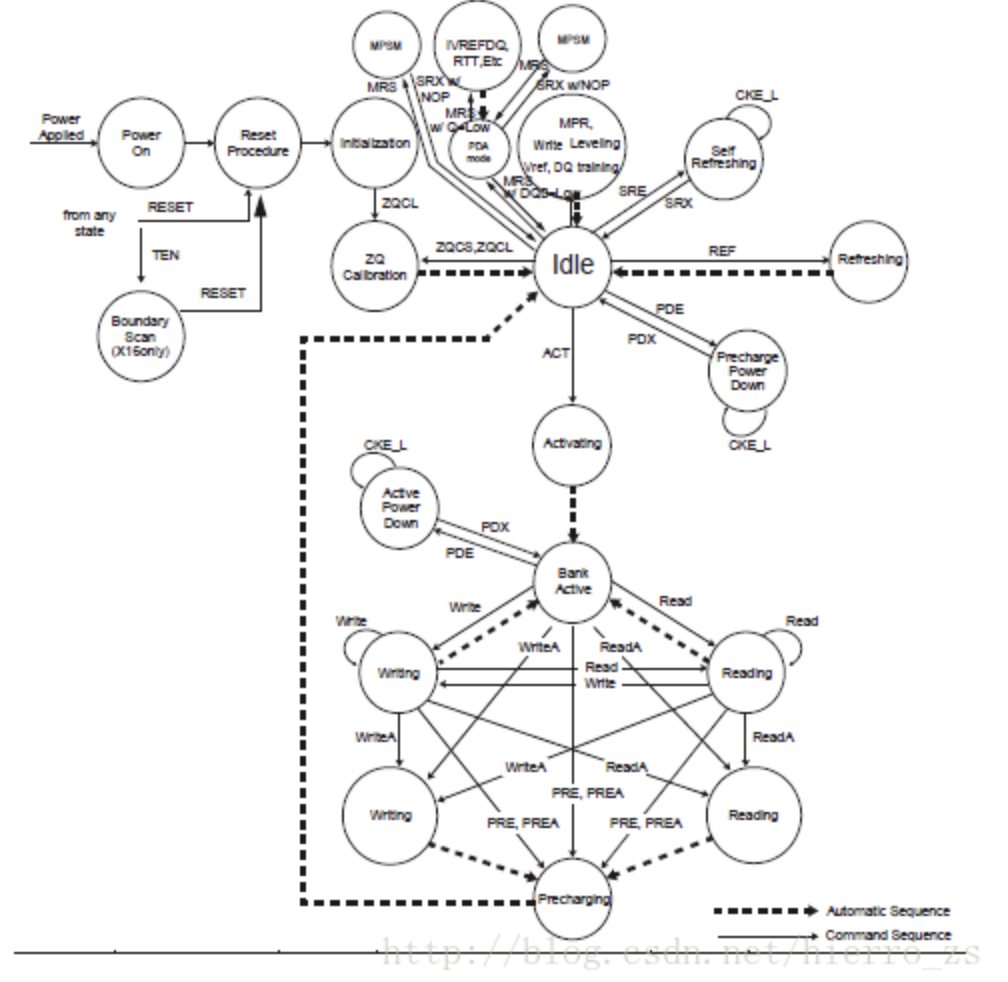

3.1 简化的状态转换图

NOTE 此简化的状态机仅提供可能的状态转换与命令控制的概观。尤其,打开多bank与使能ODT等其他的操作的细节是没有包含进来的。

3.2 基本功能

DDR4 SDRAM是一个高速动态随机访问存储器。在x4与x8系统中,SDRAM内部配置为16个BANK,共分成4个BANK组,每个BANK组为4个BANK。在x16系统中,SDRAM内部配置为8个BANK,共分成2个BANK组,每个BANK组为4个BANK。DDR4 SDRAM采用了8倍预取的体系结构,以达到高速操作。8倍预取体系结构在IO接口上,采取了没一拍时钟传输两次数据的设计。每一次单次的读写操作的数据量都是SDRAM数据总线宽度的8倍,传输周期为四个时钟周期,也就是说,每半个周期IO接口就能够完成一次数据传输。

DDR4 SDRAM中的读写操作都是以burst为基础的,当选定一个起始地址后,接着完成八个burst长度的传输,或者是以内部定义好的序列完成4次的突发传输。操作以ACT命令被锁存为起始,后面再续以读或者写命令。在ACT命令发出时,相应的地址会选定需要激活的BANK地址与ROW地址。(BG0-BG1 in x4/8 and BG0 in x16 select the bankgroup; BA0-BA1 select the bank; A0-A17 select the row; refer to “DDR4 SDRAM Addressing” on Section 2.7 for specific requirements)。 在读写命令发出时,相应的地址会选定本次burst操作的COL地址。操作完成后是否需要PRE命令是由此时的A10地址来控制的,BC4与BL8则是由A12来控制的,如果模式寄存器中使能了OTF。

在进行所有操作之前,DDR4 SDRAM必须完成预先定义好的上电以及初始化流程。

下面的内容描述了设备复位与初始化、寄存器定义、命令描述以及设备操作的具体信息。

3.3 复位与初始化流程

在上电与复位过程中,为了防止DRAM默认状态的功能性错误,需要保证以下MR寄存器的值为下面所描述的值。

- Gear down mode (MR3 A[3]): 0 = 1/2 Rate

- Per DRAM Addressability (MR3 A[4]): 0 = Disable

- Max Power Saving Mode (MR4 A[1]): 0 = Disable

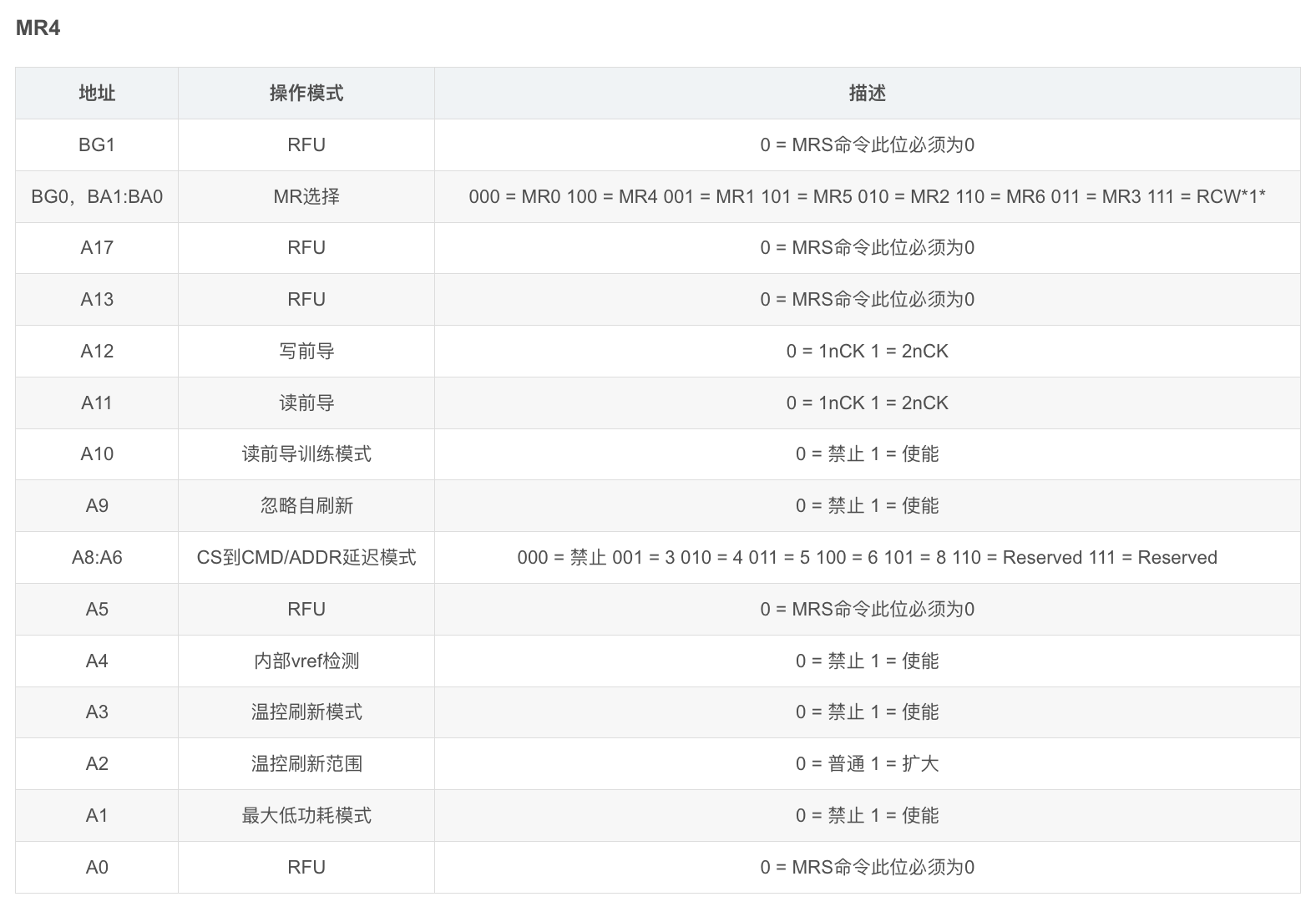

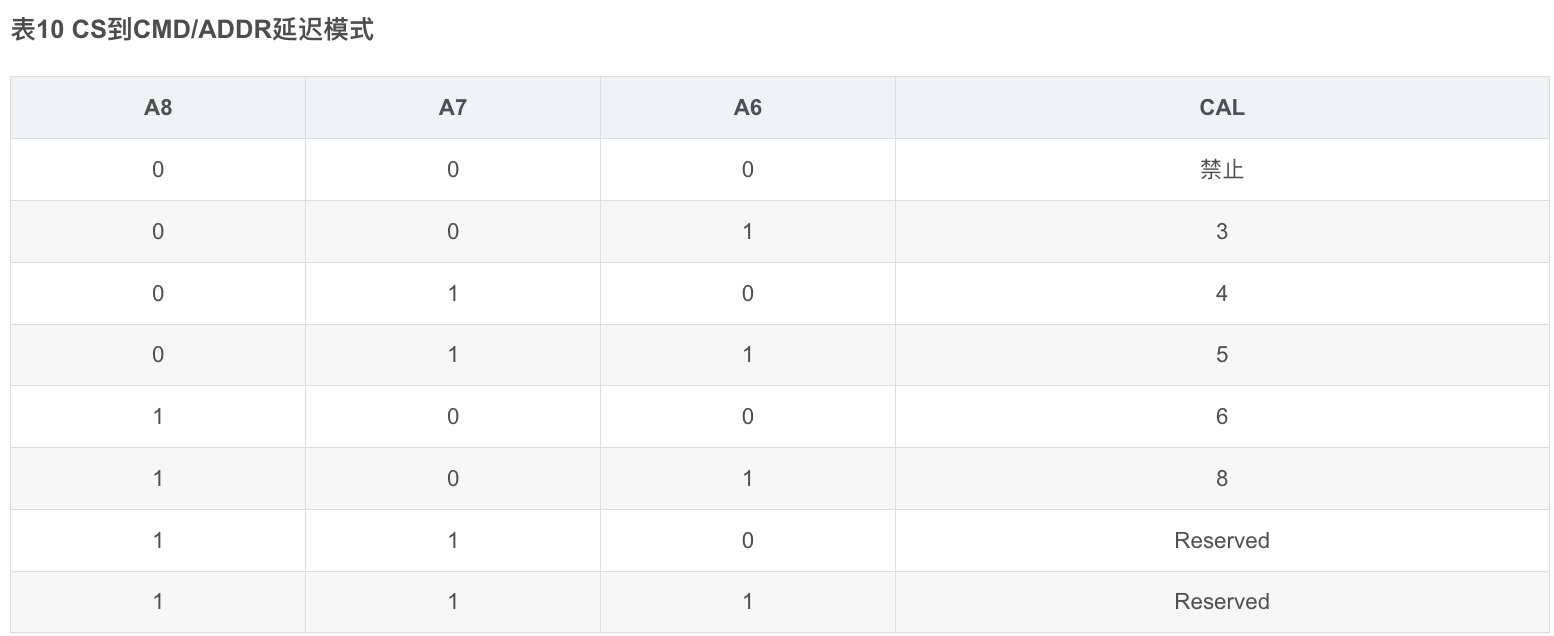

- CS to Command/Address Latency (MR4 A[8:6]): 000 = Disable

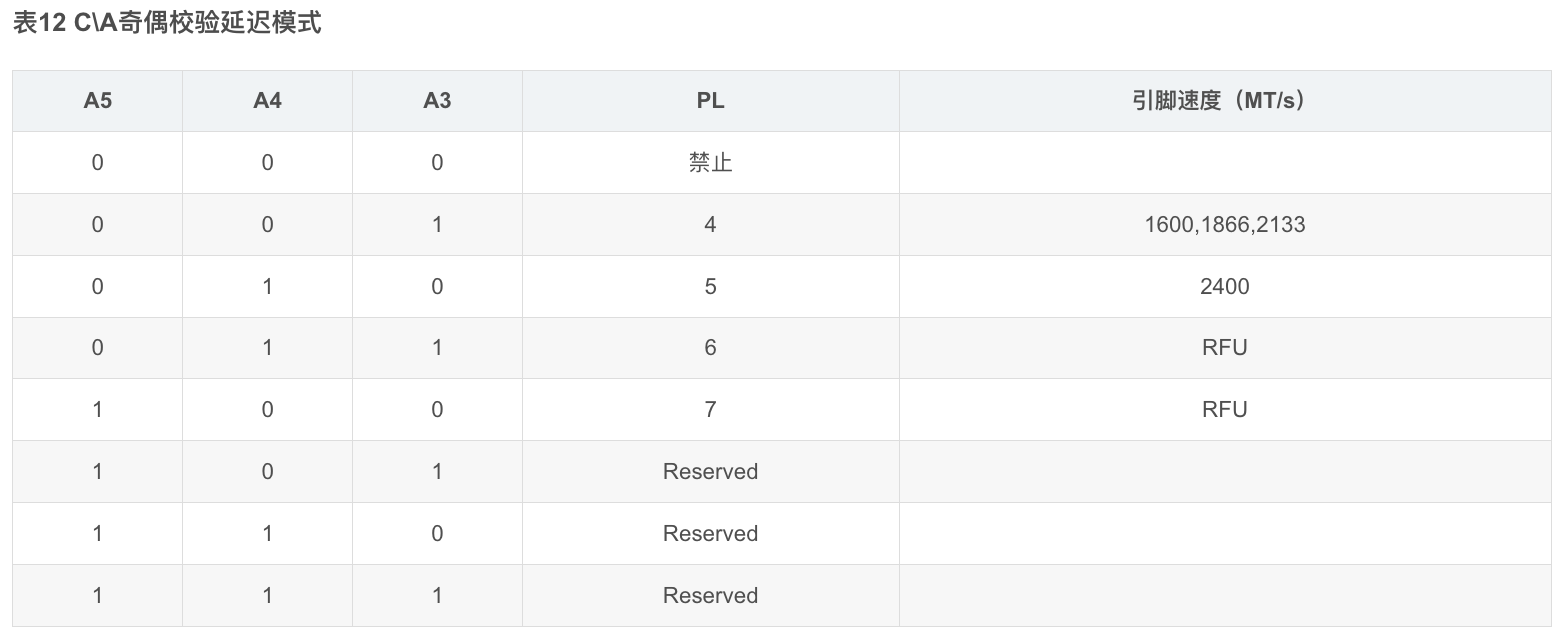

- CA Parity Latency Mode (MR5 A[2:0]): 000 = Disabl

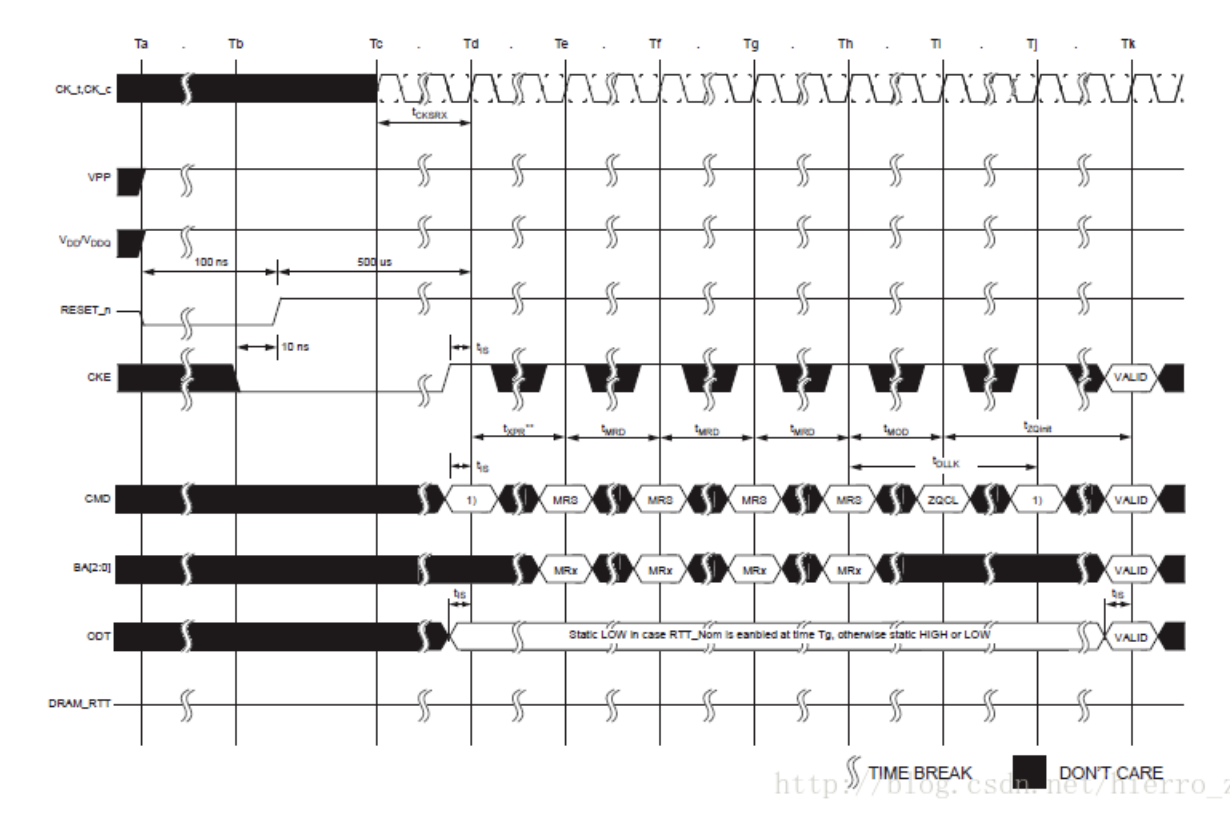

3.3.1 上电初始化流程

上电与初始化流程如下面序列所描述,且在下图中有所描述。

- 上电(RESET_n推荐保持在0.2xVDD一下,其他输入未定义)。当供电稳定之后,REASET_n至少保持200us为低电平。CKE可在RESET_n无效之前的任何时候拉成低电平(最小时间10ns)。电压从300mV升到vDD和VPP的时间不得大于200ms,且在过程中要保持VDD ≥ VDDQ 以及 (VDD-VDDQ) < 0.3v。VPP的上升时间不得小于VDD,且VPP的电压值不得小于VDD。

- VDD与VDDQ必须是由同一个电源转换器输出

- 除了VDD\VDDQ\VSS\VSSQ之外的所有引脚的电压值都不能大于VDDQ与VDD,且不能小于VSSQ与VSS。此外,在上电完成时VTT必须小于或等于TBDV最大值。

- VrefCA寻迹TBD。

- 或者

- VDD在VDDQ之前完成上电

- VDDQ在VTT与VrefCA之前完成上电

- VPP在VDD之前完成上电

除了VDD\VDDQ\VSS\VSSQ之外的所有引脚的电压值都不能大于VDDQ与VDD,且不能小于VSSQ与VSS。

- 在RESET_n失效之后,CKE需要等待500us才能变成有效。在此段时间内,DRAM内部会进行初始化,并且与外部时钟没有关系。

- CK_t与CK_c需要再CKE变成有效之前的10ns或5tck(两者间的最大值)开始并稳定。因为CKE是一个同步信号,此信号的建立时间(tIS)必须要满足。同时,DES命令必须要在td周期被锁存。一旦在复位后CKE信号被锁存为高电平,那么在整个初始化期间CKE都必须保持为高电平,包括tDLLK与tZQinit时间范围内。

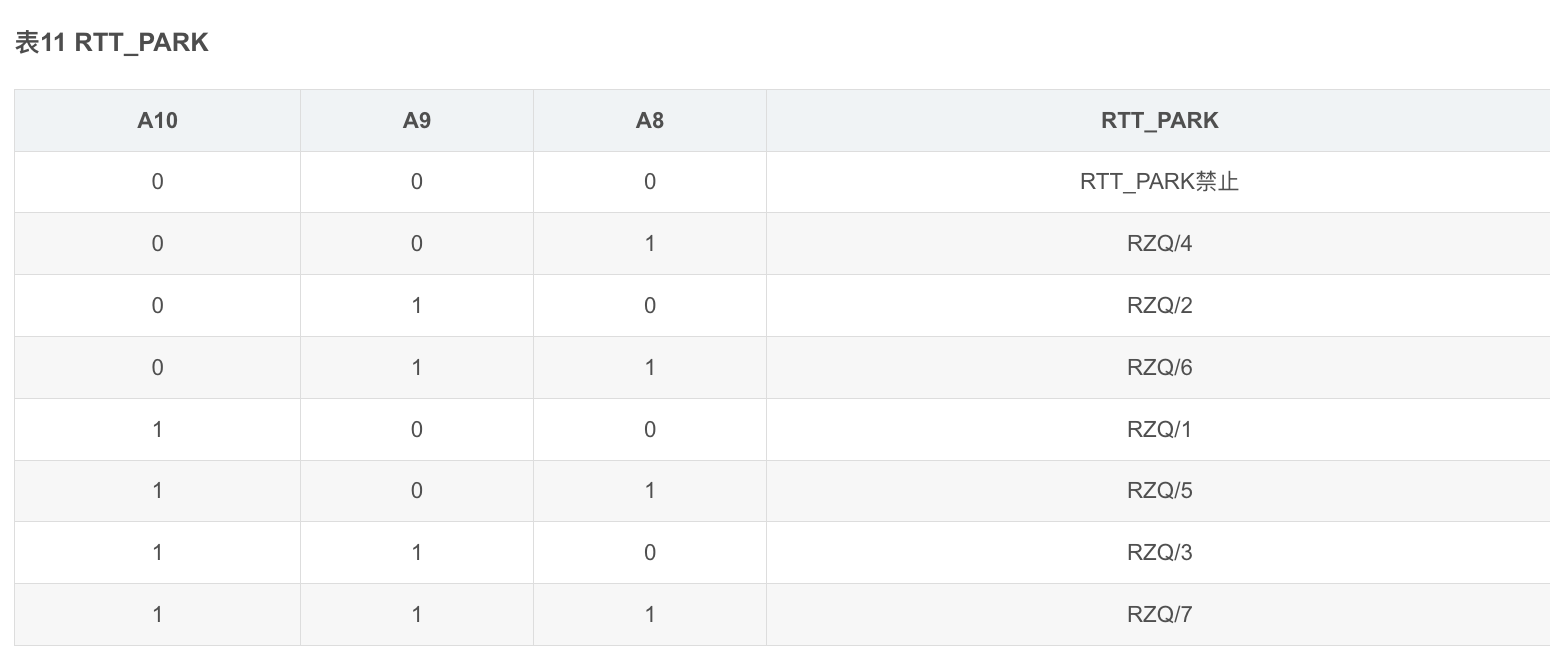

- 复位之后DDR4 SDRAM的ODT阻值会保持在一个高阻状态。并且在复位释放到CKE锁存为高电平这个阶段内ODT阻值也保持为高阻状态。ODT输入在CKE锁存为高电平之前都会定义为一个不定态,而当CKE锁存为高电平之后,ODT输入信号可能问稳定的保持在高电平或低电平。如果MR1中的RTT_NOM没有别使能,那么ODT信号就在整个初始化序列过程中都必须保持为低电平,包括整个tDLLK与tZQinit时间内。

- 在CKE锁存为高电平之后,等待tXPR时间(最小的复位时时钟使能退出时间),然后就能够向SDRAM发出第一个MRS命令了。tXPR=Max(tXS, 5nCK)。

- 配置MR3寄存器

- 配置MR6寄存器

- 配置MR5寄存器

- 配置MR4寄存器

- 配置MR2寄存器

- 配置MR1寄存器

- 配置MR0寄存器

- 向SDRAM发送ZQCL命令,触发ZQ校准

- 等待tDLLK与tZQinit时间完成

- 此时DDR4 SDRAM已经完成初始化状态,并且已经为接下来的读写训练做好准备了(包括vref训练与Write Leveling)。

NOTE 1 在Td与Tk之间,MRS与ZQCL命令之间必须有DES命令。

NOTE 2 MRS命令必须配置所有需要设置的模式寄存器

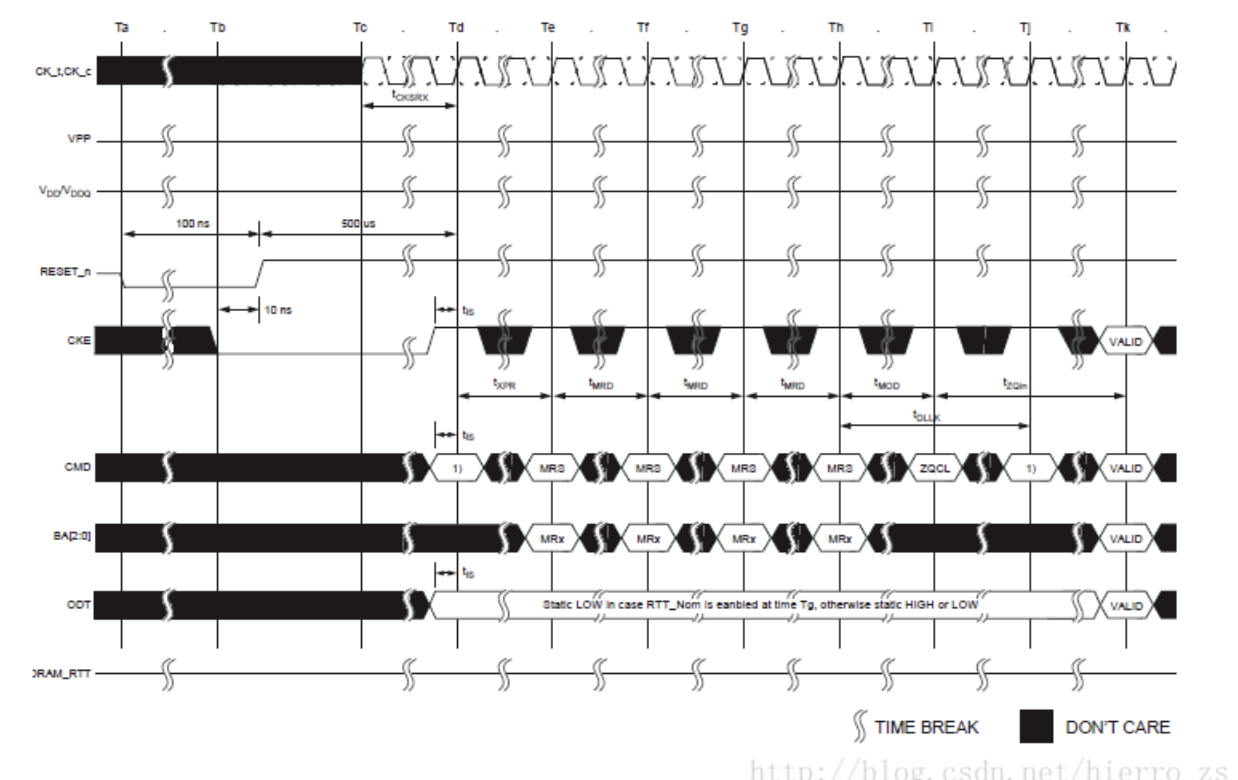

3.3.2 稳定电源情况下的复位初始化

一下的初始化流程是需要再没有电源中断的情况下进行复位初始化的。

- 当需要激活RESET_n时,将此信号拉低至0.2 * VDD(其他的信号没有要求)。RESET_n至少需要保持tPW_RESET的最小值。CKE可在RESET_n无效之前的任何时候拉成低电平(最小时间10ns)

- 执行3.3.1章节中的2-10步

- 复位序列完成,并且已经为接下来的读写训练做好准备了(包括vref训练与Write Leveling)。

NOTE 1 在Td与Tk之间,MRS与ZQCL命令之间必须有DES命令。

NOTE 2 MRS命令必须配置所有需要设置的模式寄存器

3.4 寄存器定义

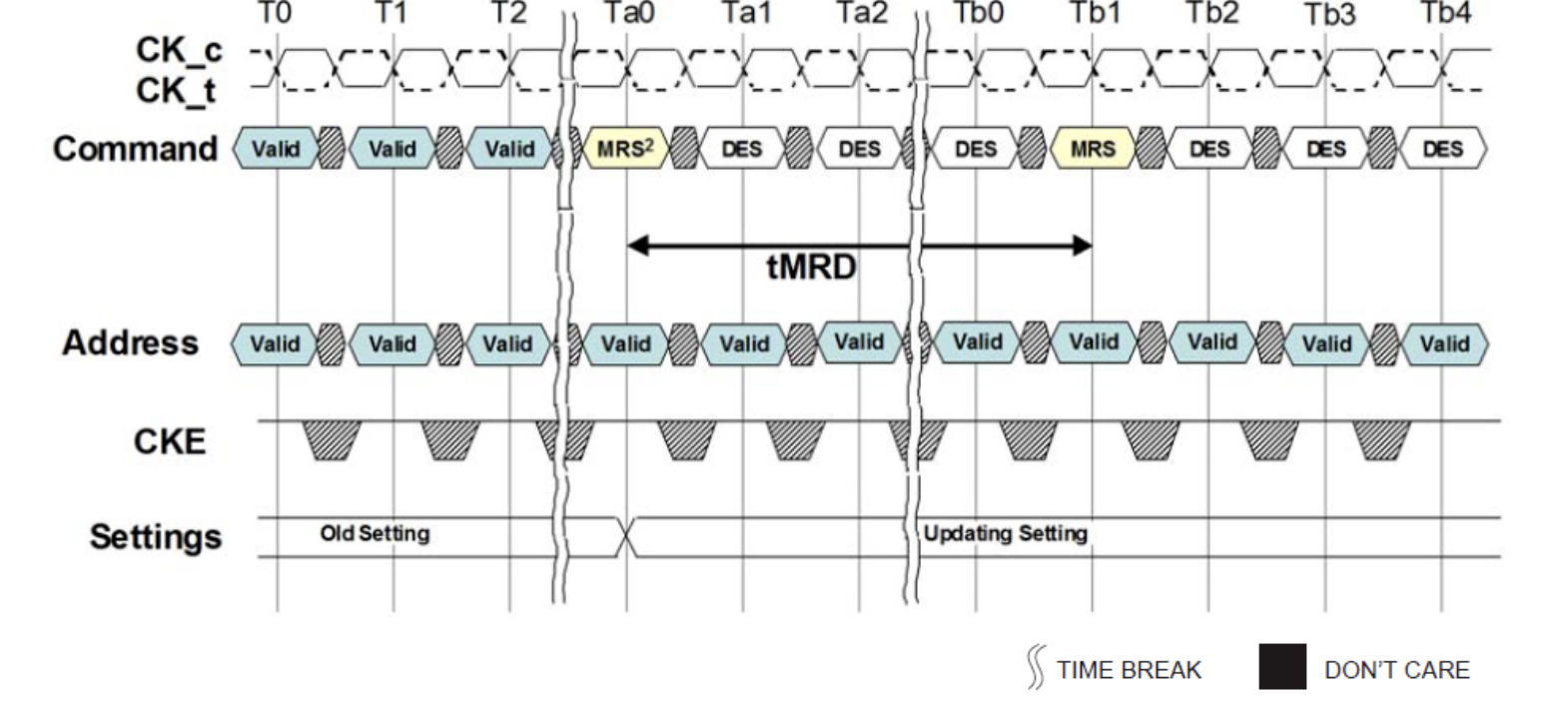

3.4.1 对模式寄存器进行编程

为了提高程序的易用性,DDR4 SDRAM提供了7个模式寄存器,包含了DDR4 SDRAM的多种功能,特性以及模式的配置,用户可通过MRS命令来配置需要的值。模式寄存器根据功能或模式分成了多个寄存器域。并不是所有的模式寄存器都有缺省值,所以需要初始化或者重新初始化,例如在上电或者复位后都要向模式寄存器写入合适的值。在普通的操作中,模式寄存器也可以通过重新执行MRS命令来更新其中的值。当执行MRS命令来编程模式寄存器时,即使用户指向修改寄存器中的某些位,模式寄存器地址对应的所有区域都会被修改,也就是说MRS命令不支持mask操作。MRS命令与DLL复位操作不会影响存储阵列中的内容,因此这两种命令可以在上电完成后的任何时间内执行。模式寄存器的操作周期为tMRD,即此时间为MRS完成写模式寄存器的最小时间,也是两个MRS命令之间的最小时间。

NOTE 此时序图所表示的是C/A奇偶校验延迟模式关闭的状态

NOTE 以下模式不需要遵循tMRD时间

- Gear down mode

- C/A Parity Latency mode

- CS to Command/Address Latency mode

- Per Dran Addressability mode

- VrefDQ training Value, VrefDQ Training mode and VrefDQ training Range

某些模式寄存器的设定可能会影响地址、命令、控制输入的功能性,在这些情况下,只有当前MRS命令完成功能更新时,下一次的MRS命令才能继续发出。这种类型的MRS命令也不需要遵循tMRD的限制,如上图中note所示。在相应的功能描述中,可以对这种MRS命令流程的描述。

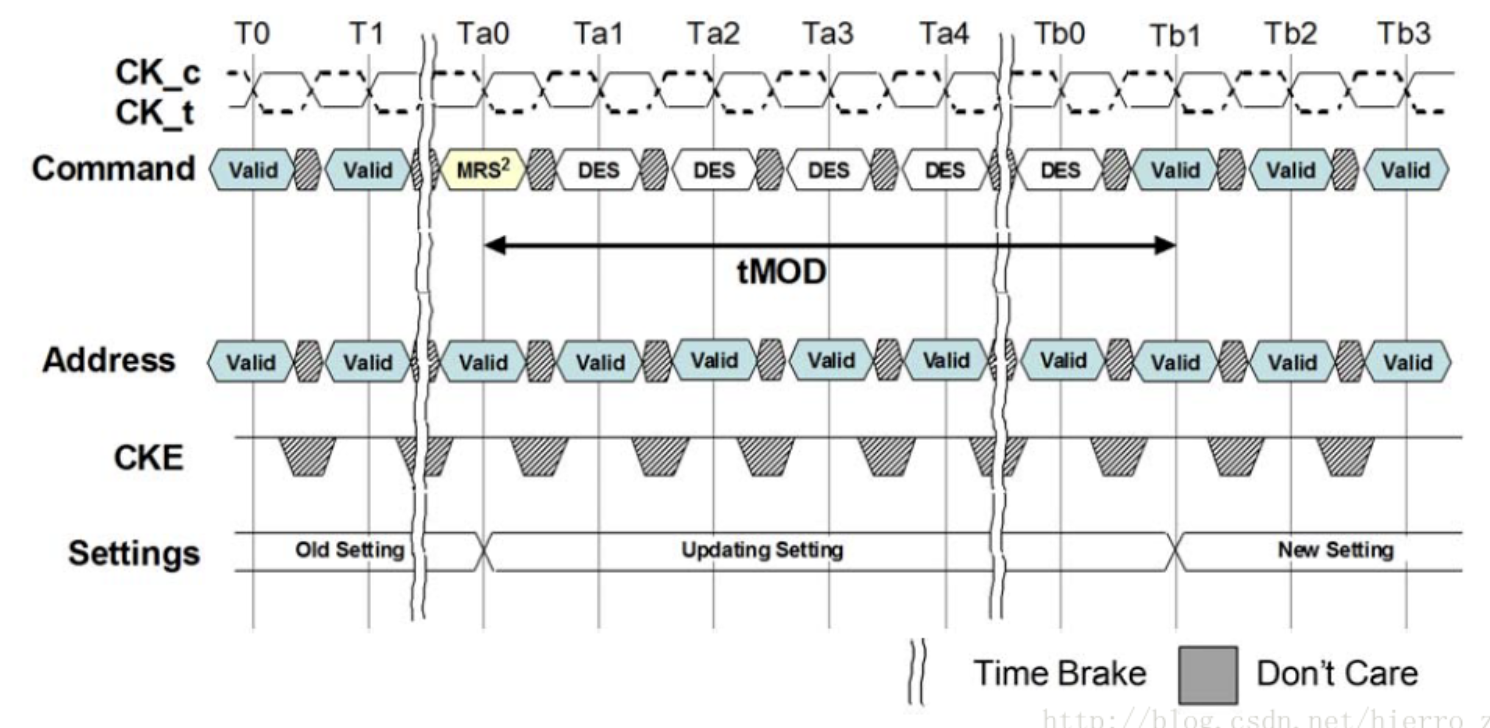

大部分的MRS命令到非MRS命令的延迟为tMOD,此延时是为了使DRAM能更新所有MR寄存器中配置的功能。MRS后tMOD时间内部运行除了DES以外的所有非MRS命令执行。

NOTE 此时序图所表示的是C/A奇偶校验延迟模式关闭的状态

NOTE 以下模式不需要遵循tMRD时间

- DLL Enable, DLL Reset

- VrefDQ training Value, internal Vref Monitor, VrefDQ Training mode and VrefDQ training Range

- Gear Down mode

- Per DRAM addressability mode

- Maximun Power saving mode

- CA Parity mode

只要DRAM处于空闲状态,模式寄存器可以在与普通操作同样的时间要求和命令下修改其中的值,例如所有的bank都已经完成预充电,并满足tPR时间,且所有的数据burst已经完成,CKE在MRS命令之间也是保持高电平。对于MRS命令,若RTT_Nom功能需要修改(使能到禁止,反之亦然),或者是DRAM 已经使能了RTT_Nom,那么在MRS命令使能或禁止RTT_Nom之前ODT信号必须锁存为低电平以保证RTT_Nom是处于关闭状态。如上图中所示,ODT信号可在MRS命令之后的tMOD时间外锁存为高电平。如果RTT_Nom功能在MRS命令之前或之后都是禁止的状态,那么SDRAM就不关心ODT信号的电平值了。

有些操作的功能更新时间会大于tMOD,如上图中NOTE所示。这些MRS流程的说在,相应的功能描述中会有详细说明。

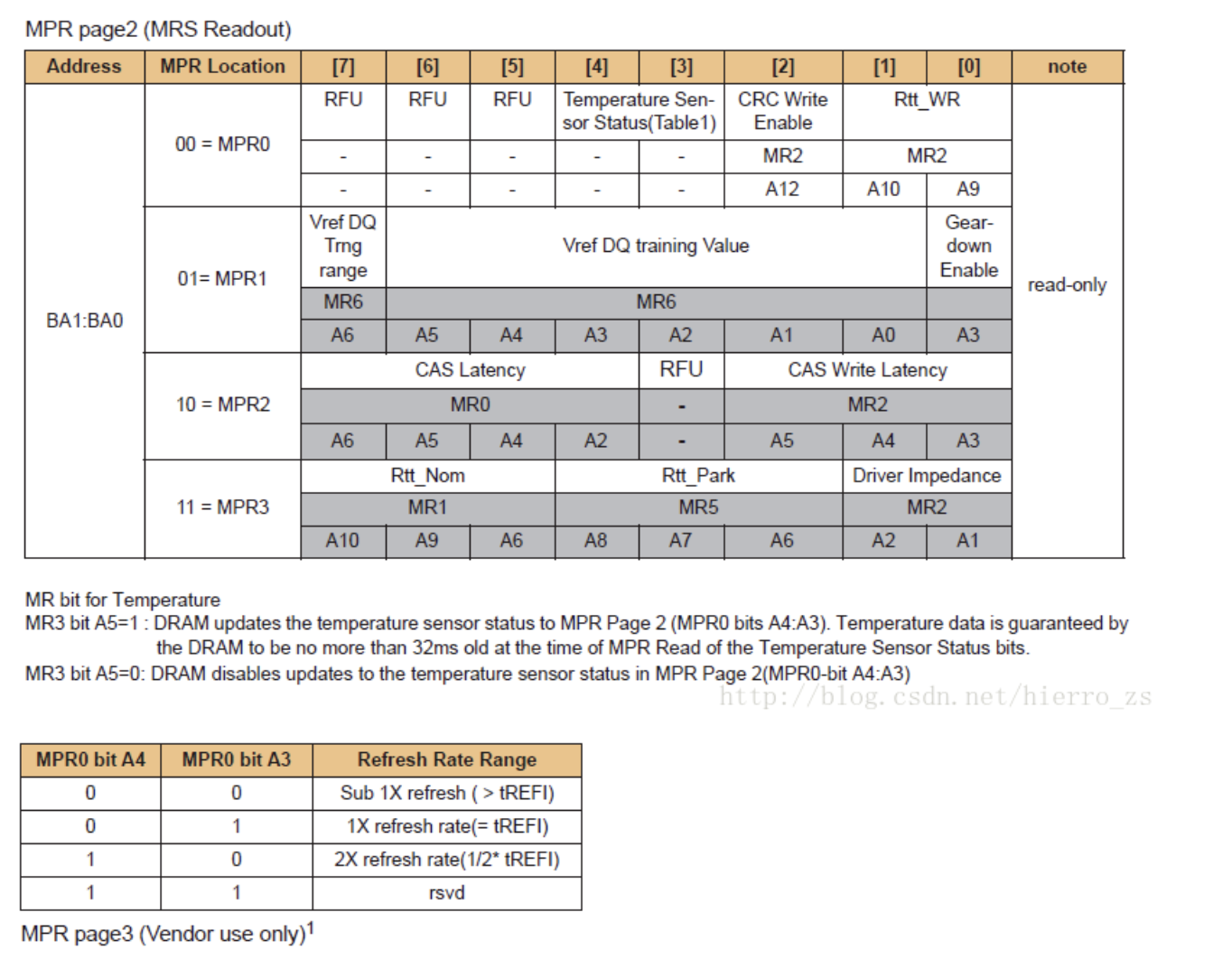

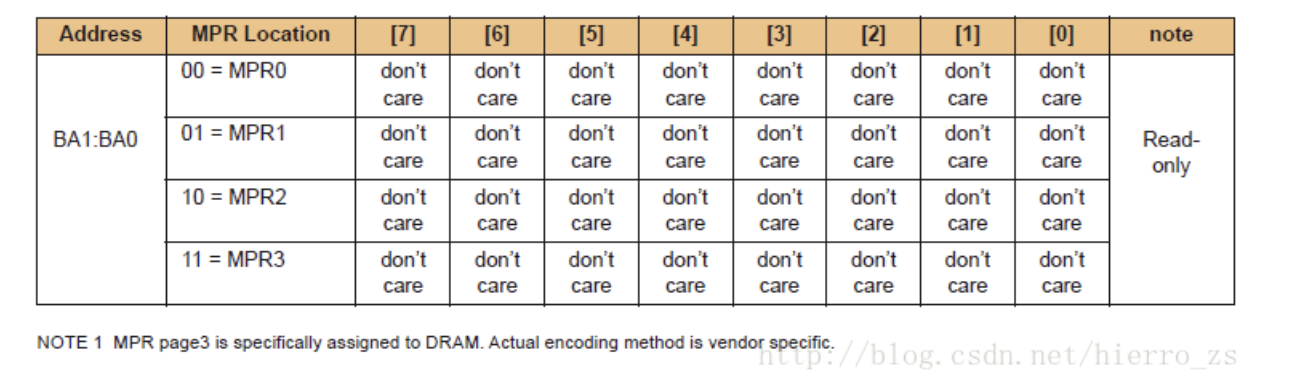

3.5 模式寄存器

注释:RFU->Reserved For Use;

TBD -> To Be Defined;

MR0

NOTE :

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

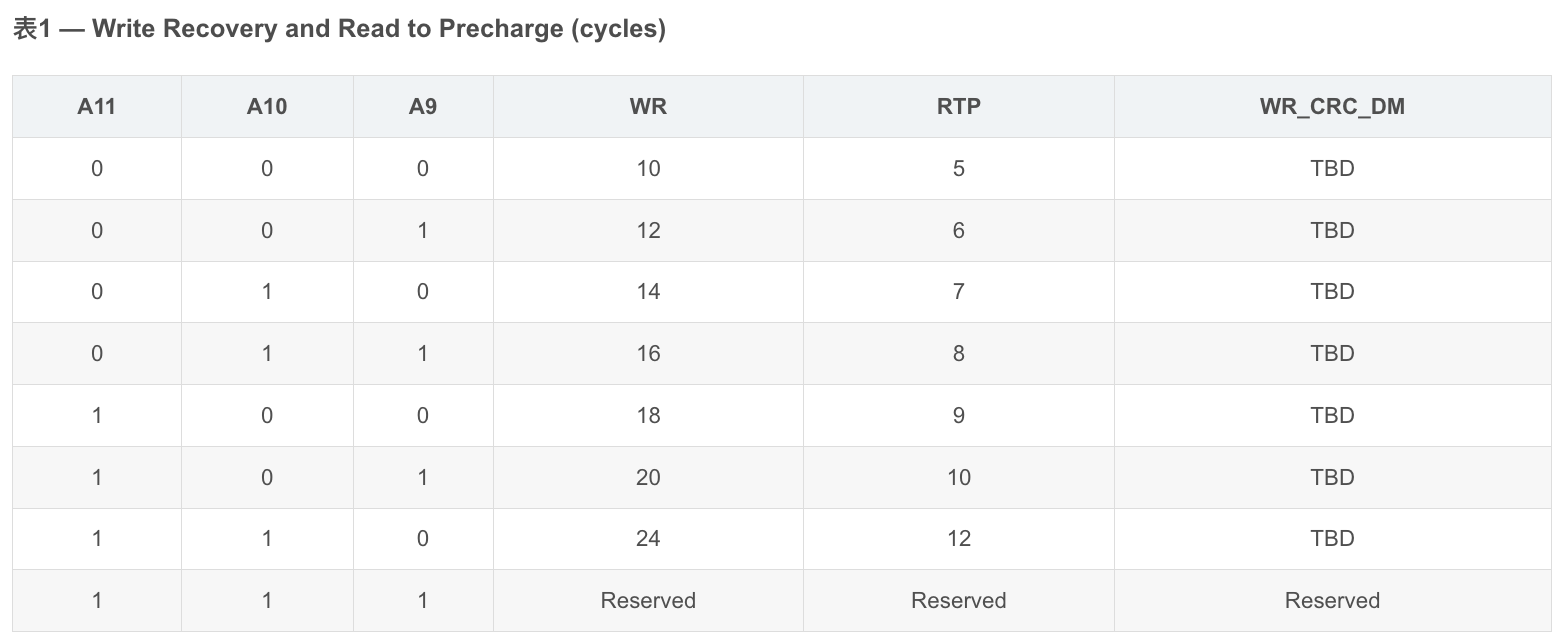

- WR为写恢复时间,此值的计算方式为将tWR除以tCK,并对其去尾加一取整。WR必须设置为一个不大于tWR最小时间的值,并且与tRP共同组成了tDAL。

- 表格中显示的写恢复时间为可编程的值,实际的tWR实际需要参考AC时序列表中的值。

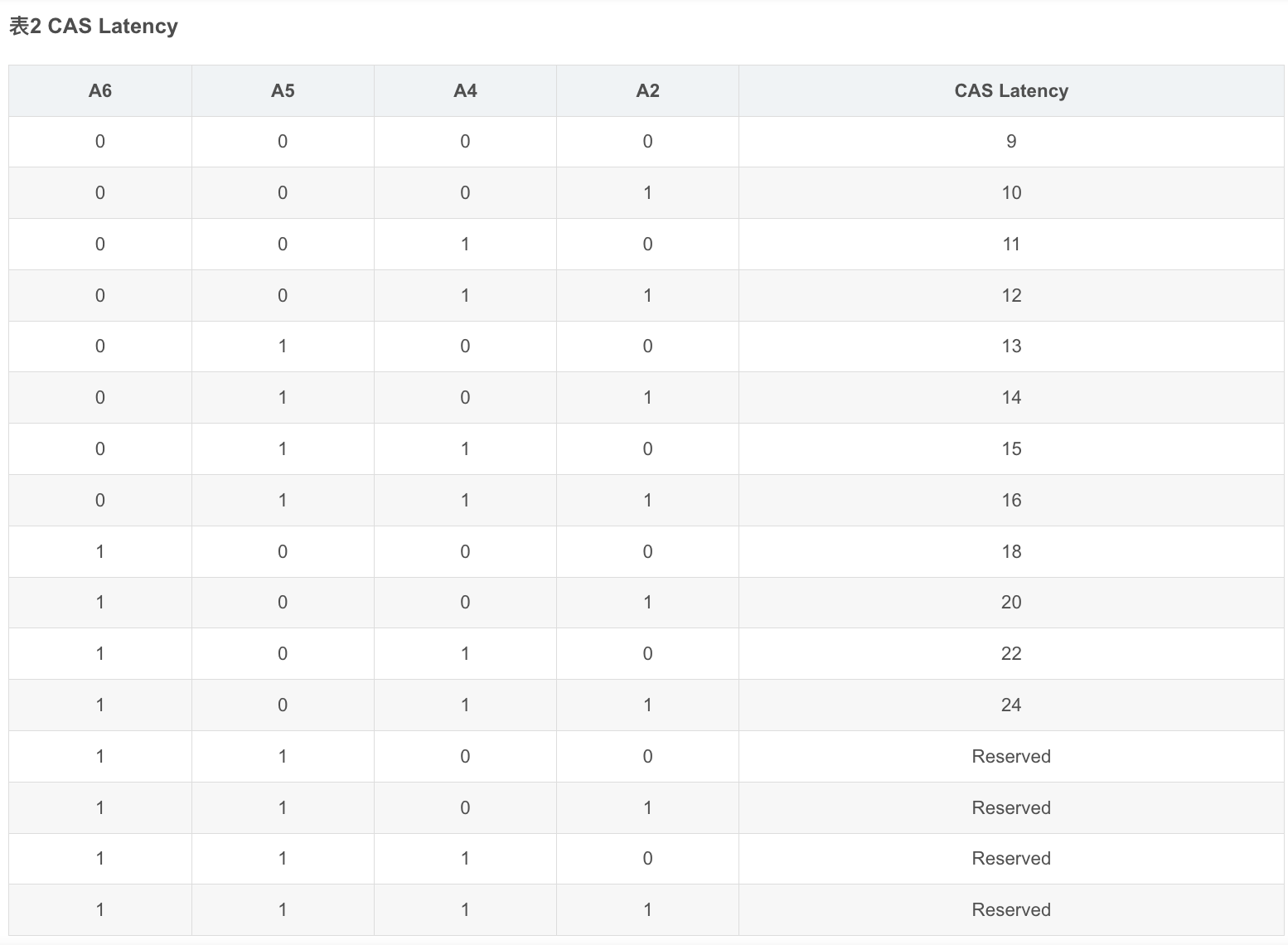

- 表格中显示的CAS延迟为可编程的值,实际的CAS延迟值需要参考AC时序列表中的值。

NOTE :

- 输出禁止包含-DQs,DQS_ts,DQS_cs

- 对于DDR4来说,0就等价于禁止状态

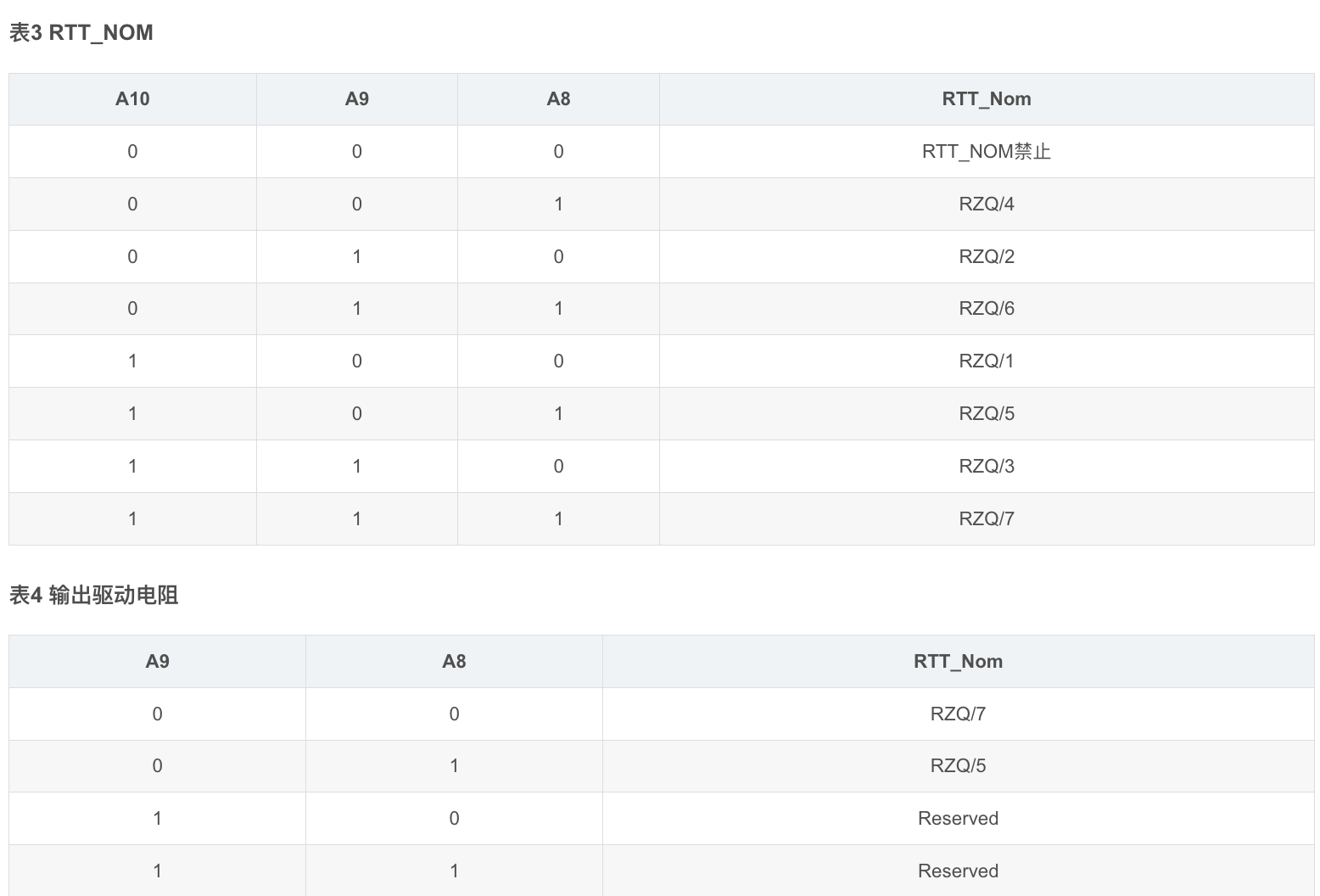

NOTE :

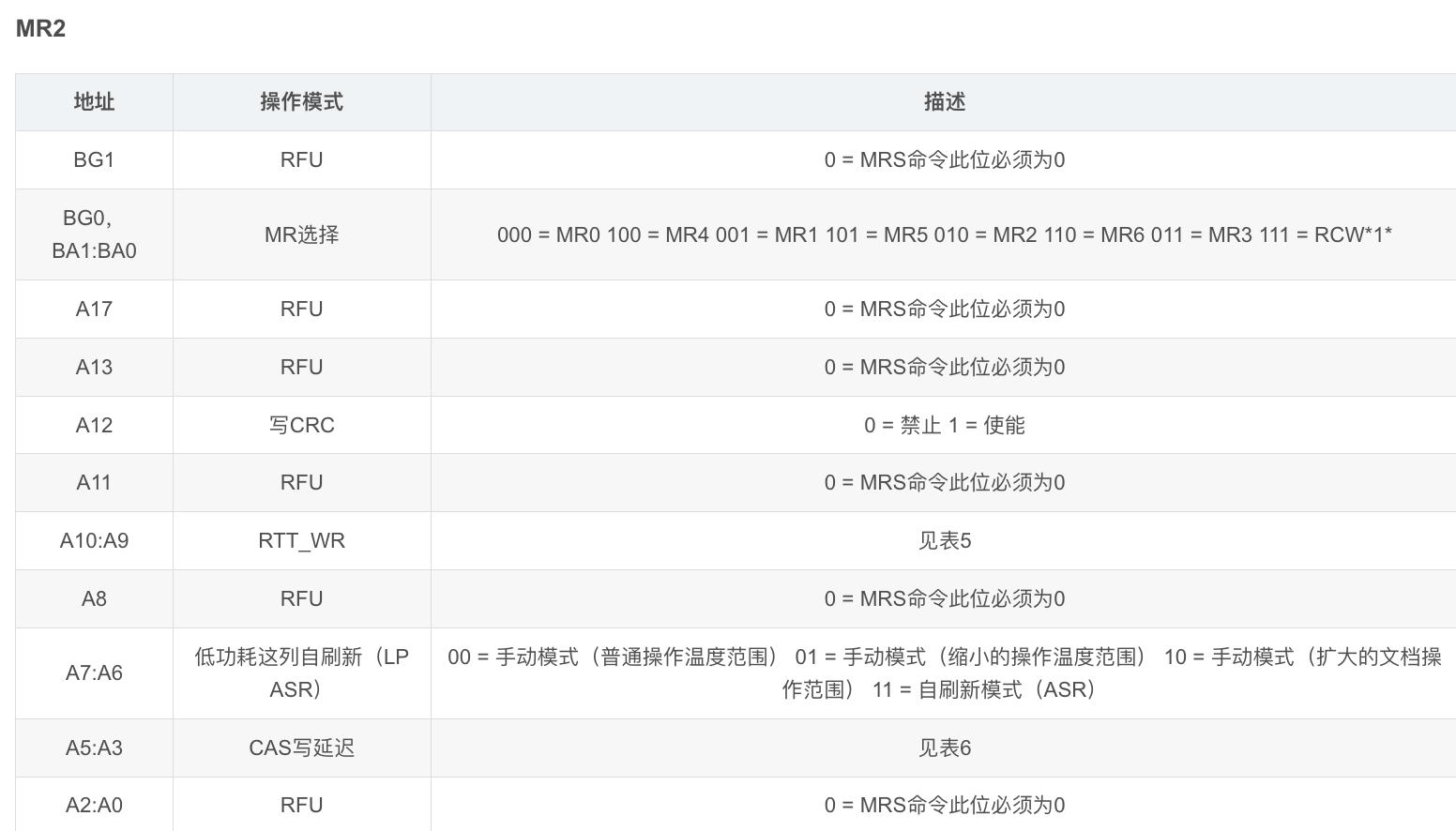

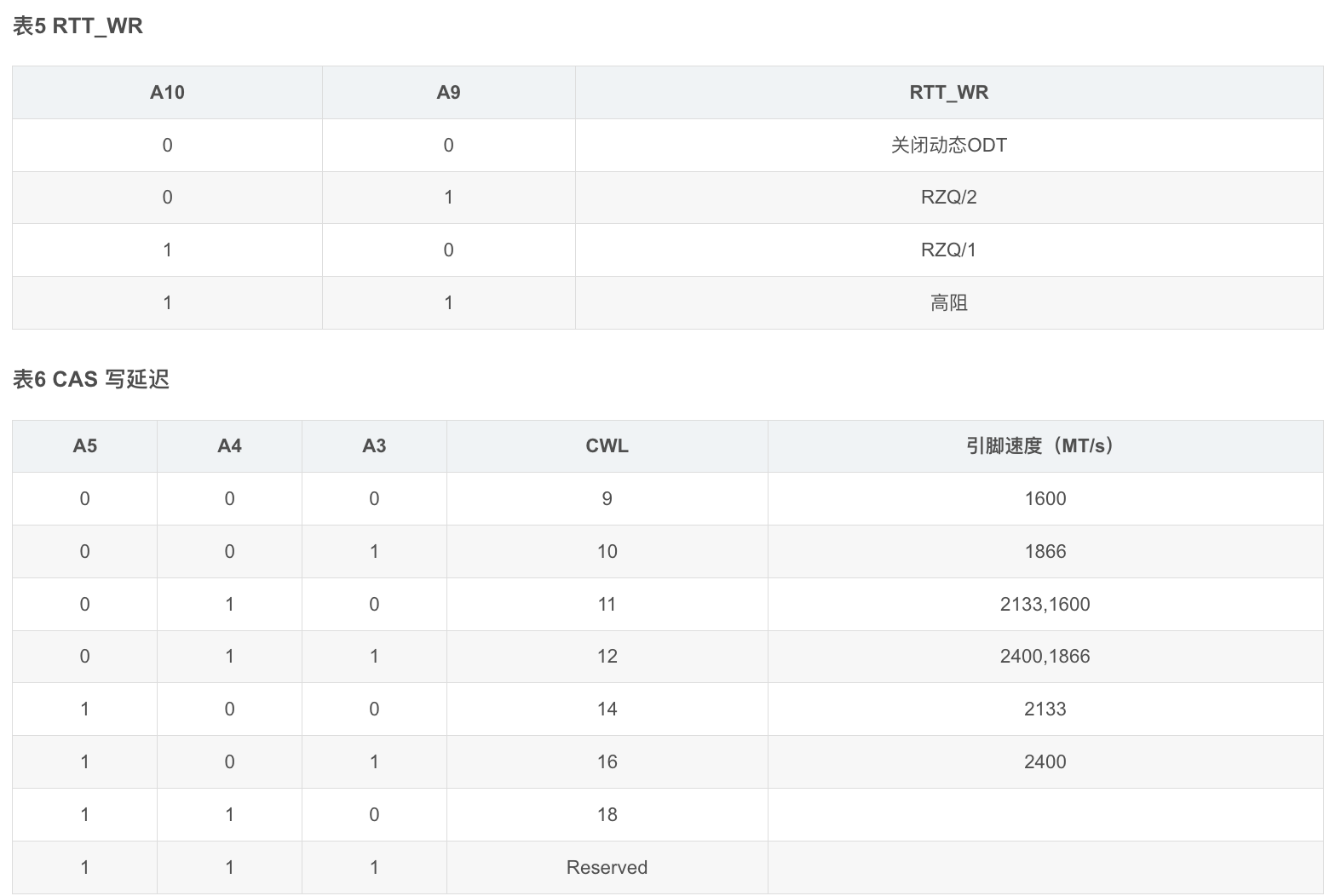

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

NOTE :

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

NOTE :

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

NOTE :

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

- 当MR1中的RTT_Nom禁止时,MR5中的A5也将被忽略

NOTE :

- 为寄存器控制字预留设置。DRAM将会忽略MRS命令的BG0,BA1;BA0=111,并不会有任何回应。当MR寄存器中的RFU被输入修改,DRAM中没有定义对应的操作。

DDR4 SDRAM中MR7忽略

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第2章 DDR4 SDRAM 的引脚封装与寻址

- JESD79-4 第4章 SDRAM命令描述与操作(4.28-4.29)

- JESD79-4 第4章 SDRAM命令描述与操作(4.26-4.27)

- JESD79-4 第4章 SDRAM命令描述与操作(4.25)

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。