4.26 刷新命令

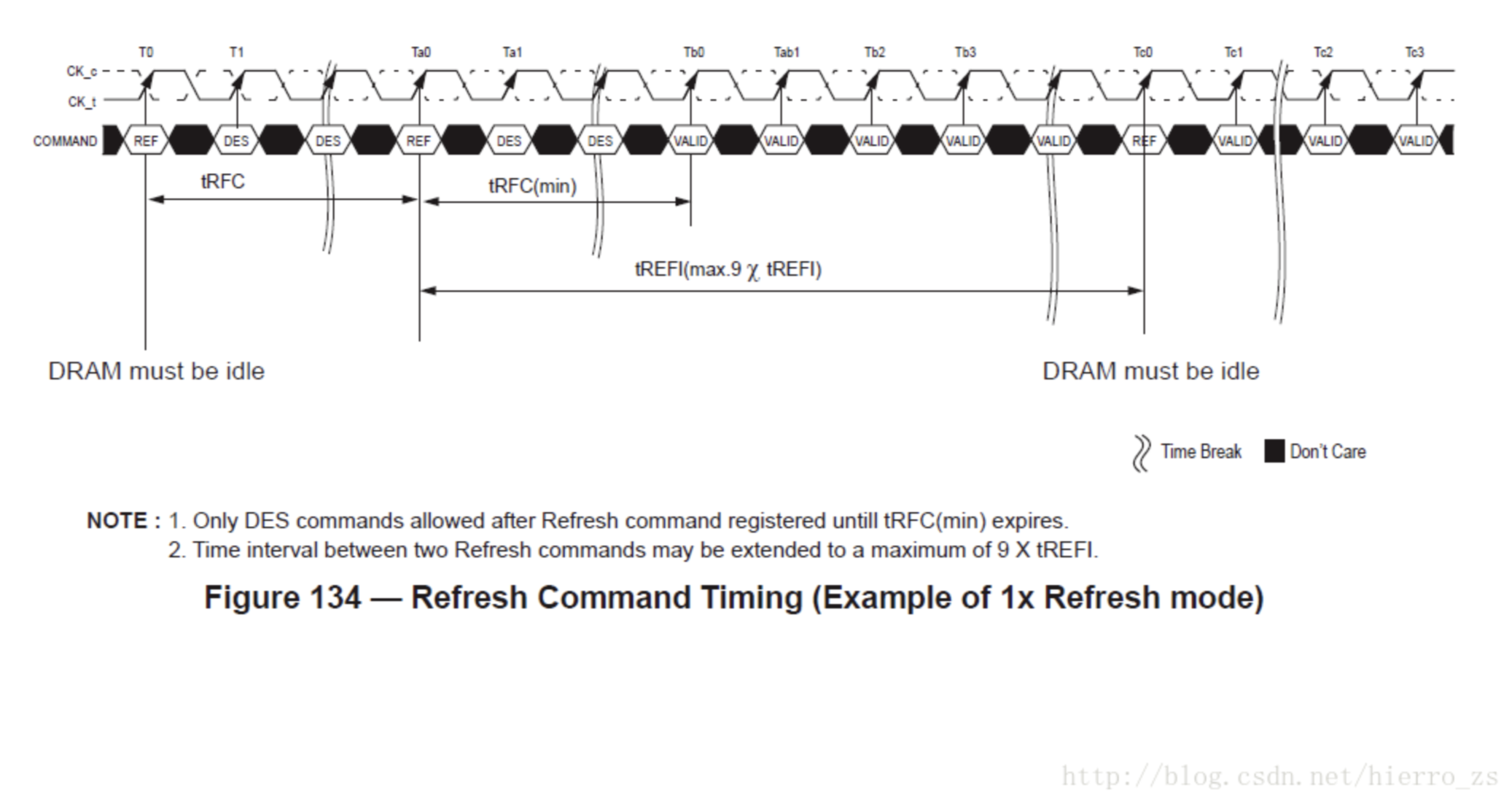

在DDR4 SDRAM中刷新命令是在不同的操作中使用的。此命令并不是一直持续的,因此控制器必须在需要刷新的时候向DRAM发送REF命令。DDR4 SDRAM的每次刷新间隔为tREFI。当时钟的上升沿,CS_n, RAS_n/A16以及 CAS_n/A15保持低电平,且WE_n/A14与ACT_n保持高电平时,DRAM就会进入刷新周期。在进入刷新之前,所有的Bank都必须先完成Precharge,且满足时序参数tRP。刷新地址则由DRAM内部的刷新内核来生成,因此在执行REF命令时,DRAM的地址总线的值是不关心的。当刷新周期完成时,所有的Bank都是出于IDLE状态的。在REF命令之后至少需要等待tRFC时间,才能想DRAM发送除了DES之外的有效命令。tRFC参数是与颗粒容量相关的。

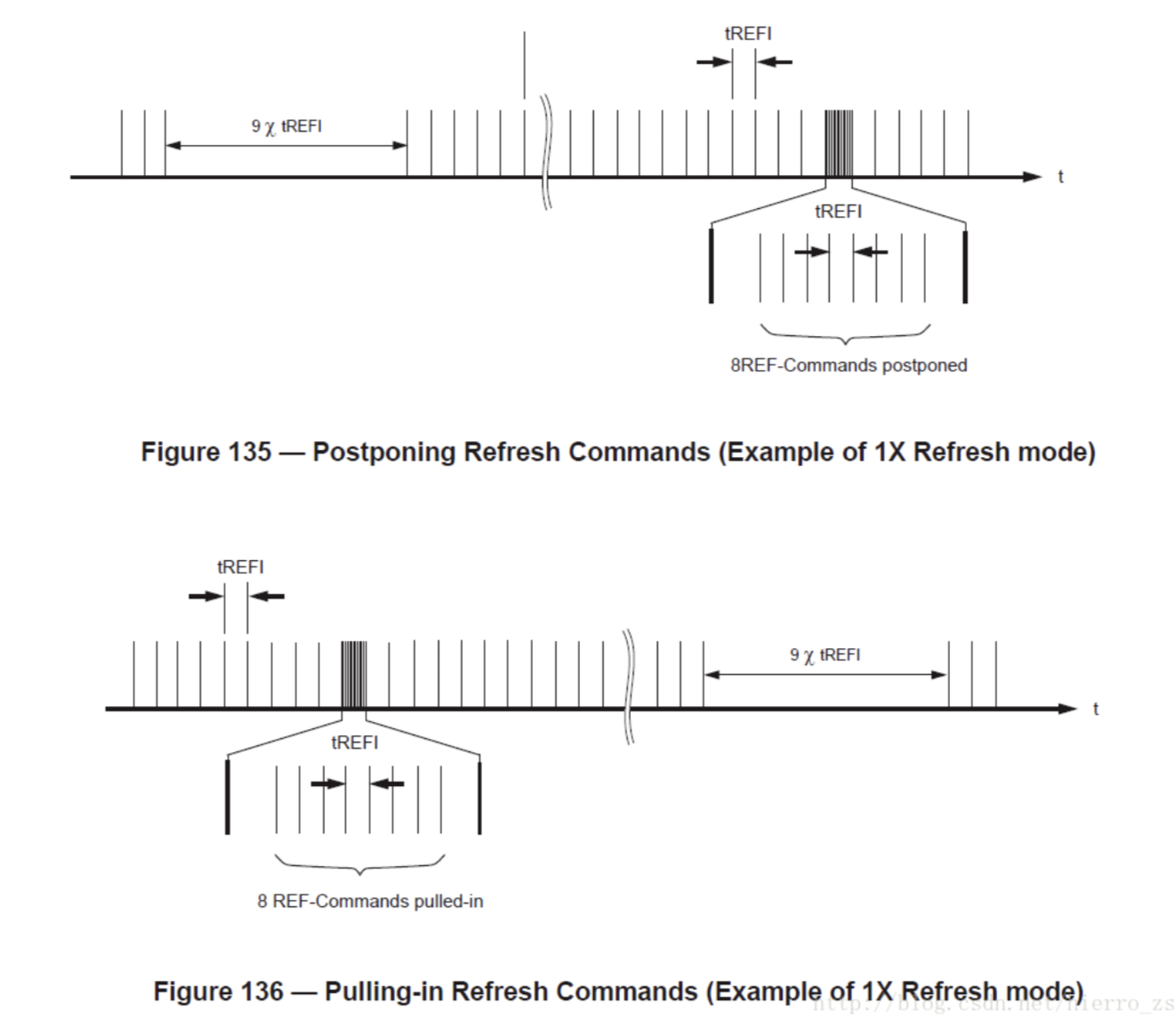

一般来说,在每个tREFI周期内都需要想DRAM发送一个REF命令。但是为了提高DRAM访问任务的高效与可切换性,REF命令允许一定灵活性,DRAM可支持REF命令的推迟与集中发送。在x1刷新模式下,最大可推迟8个REF刷新命令。在x2与x4刷新模式下,最大分别可以推迟16个与32个REF命令。也就是说,可推迟的REF命令个数在x1、x2、x4刷新模式下,分别是8、16、32。在推迟8个REF命令的情况下,REF命令之间的最大延迟可达到9 tREFI。同样的在x2与x4模式下,最大的刷新间隔为17 tREFI2与33 * tREFI。在任何情况下,最大的刷新间隔都是9 × tREFI , 17 x tRFEI2与33 x tREFI4,即使是控制器连续发送的REF命令大于8、16、32,刷新间隔也不能超过上述的时间。

4.27 自刷新操作

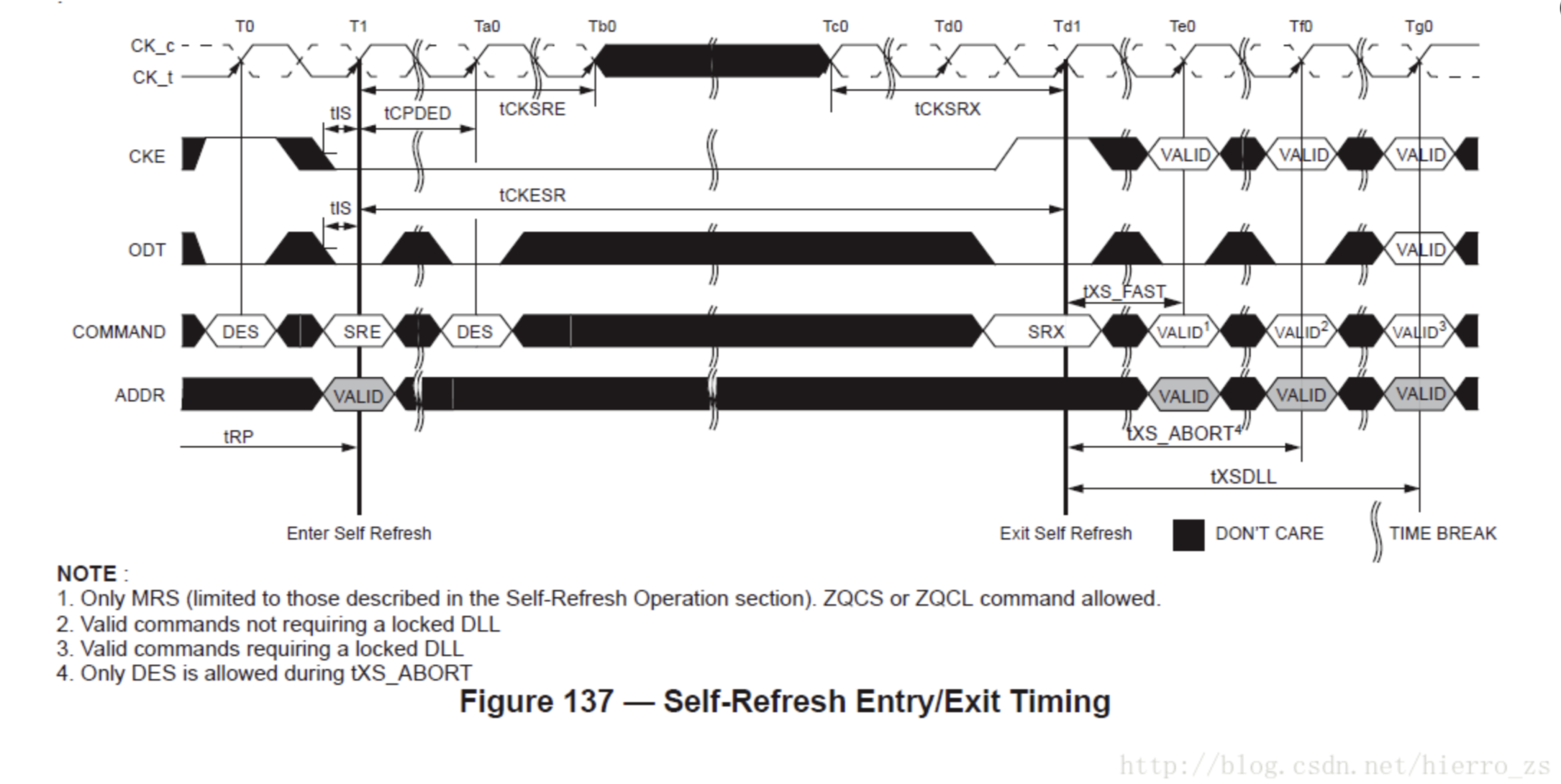

DDR4 SDRAM中自刷新超市是用来保存存储阵列中的数据,即使在系统中其他的部分都已经断电的情况下,仍可以保持其功能。DRAM内部存在一个计数器来调整自刷新操作。SRE命令的定义是在时钟上升沿时,CS_n, RAS_n/A16, CAS_n/ A15以及CKE保持低电平,WE_n/A14与ACT_n保持高电平。 在执行SRE命令之前,DRAM中的所有Bank都必须处于IDLE状态,即需要执行PRE ALL命令,且需要满足时间参数tRP。IDLE的定义是,所有的Bank都是关闭的(tRP,tDAL等),且没有正在进行的突发访问,且此时CKE为高电平。SRE命令之前的所有操作的时间参数都满足(tMRD, tMOD,tRFC, tZQinit, tZQoper, tZQCS等)。在SRE命令之前的最后一个时钟上升沿必须是一个DES命令,并且在SRE锁存后的一个时钟上升沿也必须是DES命令。在进入自刷新状态之后,DRAM会自动禁止ODT功能,并将所有终结电阻的状态设置成高阻。在退出自刷新状态后的tXSDLL时间内,DRAM会重新使能ODT,如果RTT_PARK使能,DRAM也会异步地设置RTT_PARK。DLL的状态也是在进入自刷新时关闭,退出自刷新时打开。 在进入自刷新状态之后,除了CKE与RESET之外的所有外部控制信号都是不关心的。为了维持自刷新时的操作,所有的供电与地(VDD, VDDQ, VSS, VSSQ, VPP, and VRefCA)都需要保持有效。根据DRAM的设计,DRAM内部的VrefDQ生成电路需要保持打开或者保持关闭。如果在进入自刷新状态时VerfDQ生成电路被关闭了,在退出自刷新状态时,需要保证在tXP内VrefDQ生成电路以及成功上电并且已经保持稳定。在退出自刷新之后的tXS时间内,不能出现任何写命令或者是写Leveling命令。DRAM在进入自刷新状态后的tCKE时间内最少会执行一次REF命令。 为了节约能耗,DRAM在进入自刷新状态之后会内部禁止时钟。所以DRAM处于自刷新状态的最小时间为tCKESR。用户可在进入自刷新状态之后的tCKESR时间后进行时钟频率的修改,或者是停止时钟。但是,时钟必须在退出自刷新命令钱的tCKSRX时间之外回到稳定状态。 退出自刷新的流程需要一系列的事件。第一,在CKE回到高电平之前,时钟必须保持稳定。当SRX命令被锁存时,需要满足如下的要求:

- 不需要DLL锁定的命令:

tXS时间内可发送ACT, PRE, PREA, REF, SRE, PDE, WR, WRS4, WRS8, WRA, WRAS4, WRAS8命令;tXSFast时间内可发送ZQCL, ZQCS, MRS命令。对于MRS命令,仅允许MR0中的CL与WR/RTP;MR2中的CWL以及MR3中的geardown mode可被更改,且DRAM不能处于单设备可寻址模式。访问其它的DRAM模式寄存器需要满足tXS命令。需要注意的是写命令中的ODT与动态ODT模式需要DLL锁定之后才能开启。 - 需要DLL锁定的命令

tXSDLL时间内可执行RD, RDS4, RDS8, RDA, RDAS4, RDAS8。根据系统环境与自刷新状态所占用的时间,ZQ校准命令需要执行,以补偿温度与电压的变化。在执行ZQ校准命令时,需要保证相关的时序参数满足要求。

CKE需要在退出自刷新时的tXSDLL时间内保持高电平,除了重新进入自刷新状态时。在退出自刷新后,在tXS时间之后且执行了一个REF命令,DRAM可重新进入自刷新状态或断电状态。在tXS时间内,每一个时钟上升沿都必须锁存一个DES命令。在tXSDLL时间内,当DLL-on已经打开,ODT必须在每个时钟上升沿都锁存为低电平。当DLL-off打开时,ODT可使用异步模式。在退出自刷新时,CKE信号会拉成高电平,此时可能使DRAM丢失一个内部的刷新事务。因此从退出自刷新到重新进入自刷新状态,DRAM至少需要执行一次REF命令。

从退出自刷新命令到第一个不需要DLL锁定的有效命令最小延时为tXS,为tRFC+10ns。此延时足矣让DRAM完成任何一次REF命令。当设备容量增大时,tRFC也会增加,同时tXS也会增加。MR4.A9是用来打开与关闭自刷新忽略模式的,此控制位为0时,DRAM退出自刷新,并且参考tXS参数。当此状态位有效时,DRAM将忽略任何正在进行的REF命令,并且不会增加刷新计数器。控制器可在tXS_abort时间后想DRAM发送一个REF命令,且不需要等待DLL锁定。在DRAM退出自刷新状态后,在重新进入自刷新状态之前至少需要执行一次REF命令。

4.27.1 低功耗自动自刷新

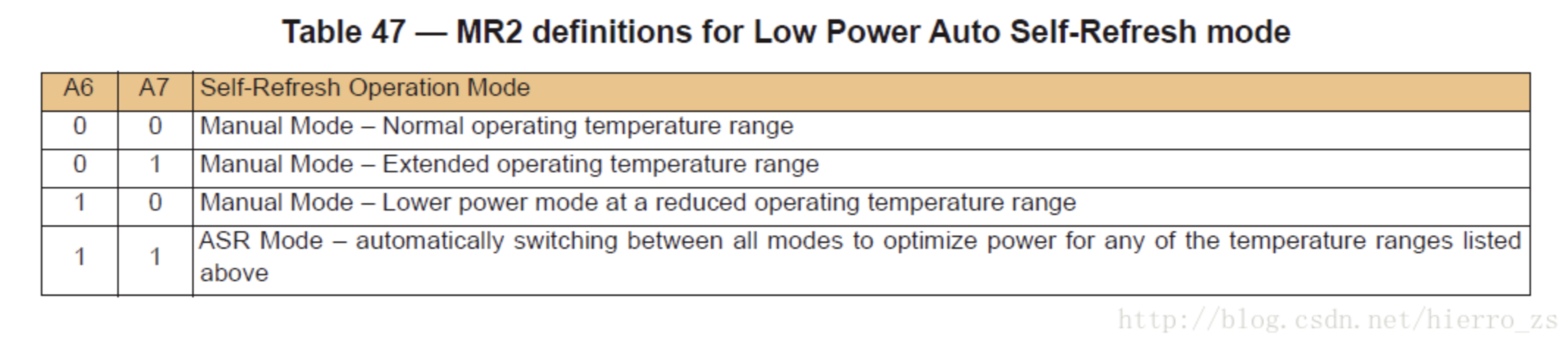

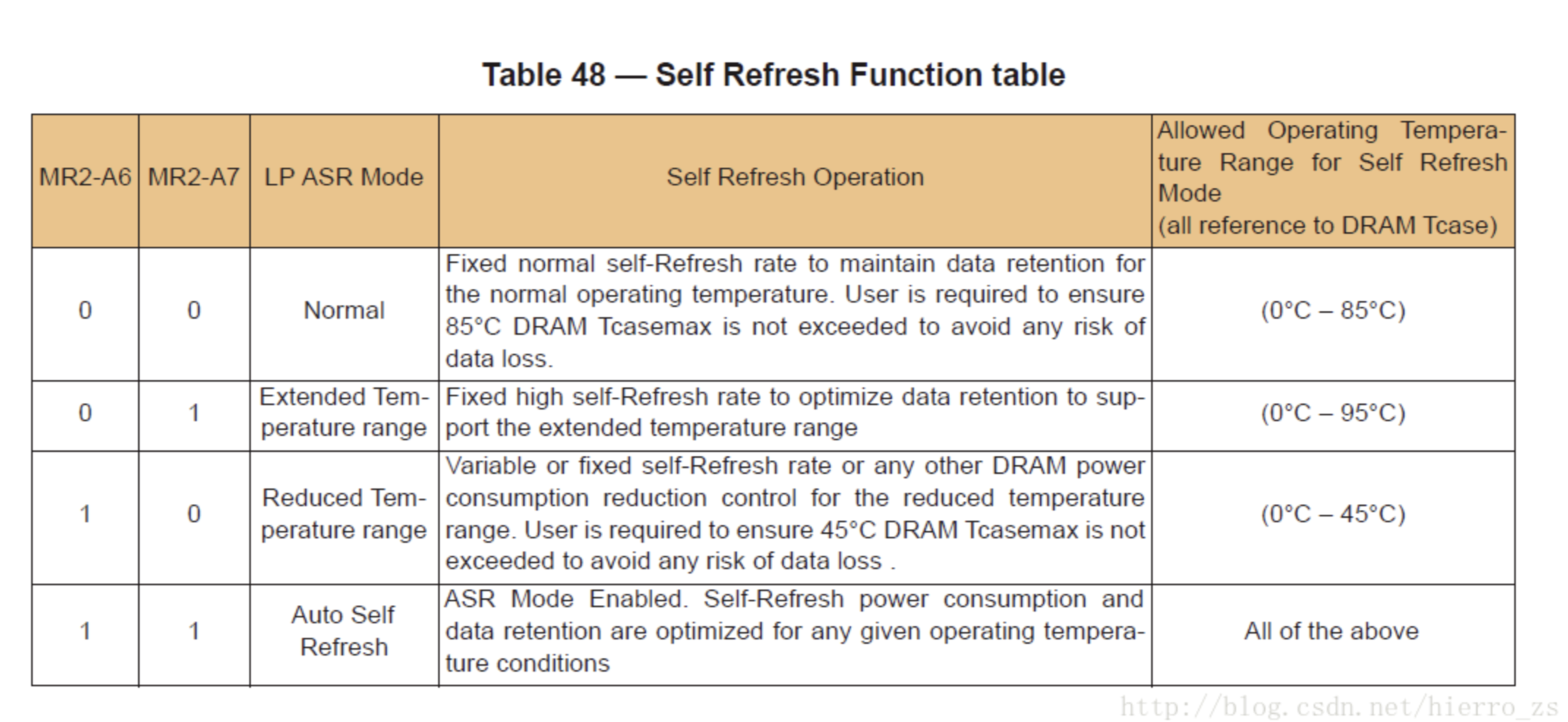

DDR4 SDRAM支持在多种温度范围内的低功耗自动自刷新操作(LP ASR)具体描述见下表中所述。

- 自动自刷新(ASR)

为了使得应用更加简便,DDR4 SDRAM提供自动自刷新模式(ASR)。ASR模式是通过MR2寄存器中的A6=1与A7=1来打开的。DRAM会根据自身的温度范围来管理进入自刷新状态的命令。在此模式下,DRAM会根据温度变化来改变刷新时间间隔。

- 手动模式

如果ASR模式没有使能,用户需要手动的将LP ASR模式寄存器配置成下面表格中的几种操作模式。根据进入自刷新状态时系统存储的温度情况,用户可在进入自刷新时选择使用哪一种固定的自刷新操作模式。用户有责任保证在ASR模式下DRAM的温度处于选择的ASR温度范围之内。并且用户需要在退出ASR到下一次ASR之前改变选择的模式。如果温度超过了选择模式的温度范围,那么有可能导致数据无法保持其正确性。

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.25)

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

- JESD79-4 第4章 SDRAM命令描述与操作(4.20-4.23)

- JESD79-4 第4章 SDRAM命令描述与操作(4.17-4.19)

- JESD79-4 第4章 SDRAM命令描述与操作(4.14-4.16)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。