本节基于 DFI 协议 4.1 节(协议 4.0 版本)讨论 MC 与 PHY 之间的 DFI 初始化行为。

1 DFI 初始化过程

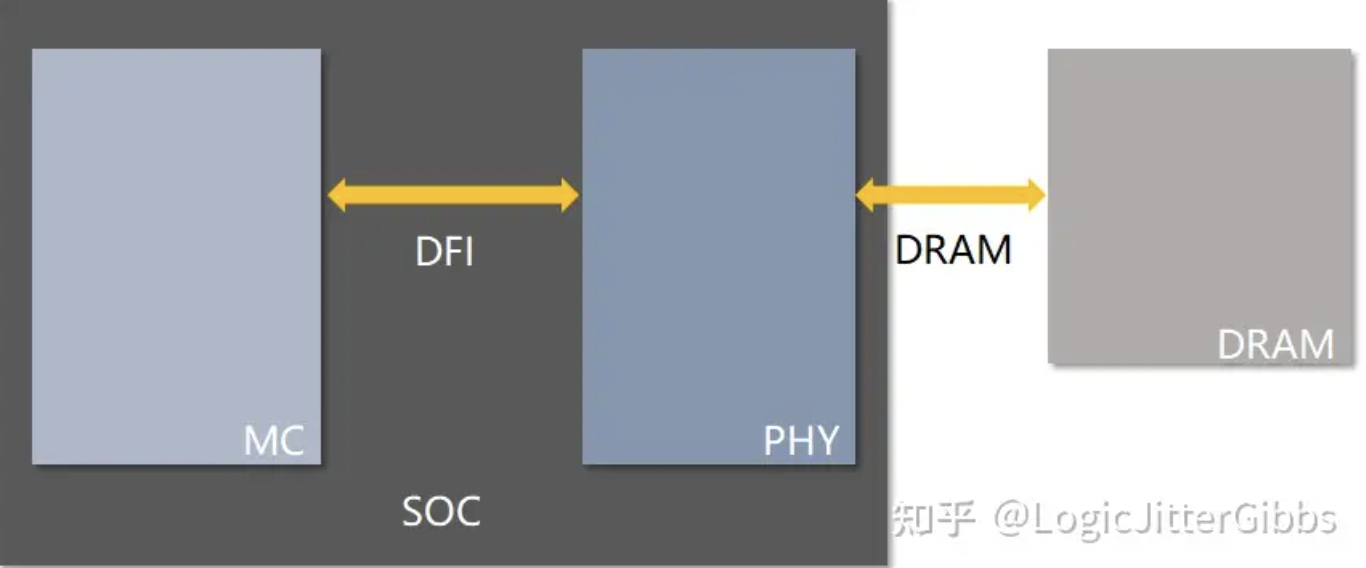

在一个典型的 DFI 架构中,MC 和 PHY 的交互是从 DFI 初始化(DFI Initialization)开始的。

1.1 基本 DFI 初始化流程

一般来说,基本的 DFI 初始化流程分为如下 3 步:

MC 在自身初始化就绪后,置起 dfi_init_start 信号,通知 PHY 其请求 DFI 初始化。

PHY 在接收到 dfi_init_start 信号,如果自身初始化也就绪,那么置高 dfi_init_complete 信号,表示此后可以接收 MC 发送的有效 DFI 信号,并将其转换到 DRAM 总线上。

MC 接收到 dfi_init_complete,初始化完成。之后 MC 可以在两者同时为高至少一个时钟周期后置低 ,或者保持 dfi_init_start 信号。

基本的 DFI 初始化流程是 dfi_init_start 信号和 dfi_init_complete 信号的握手流程。

1.2 DFI 初始化中的频率比信号

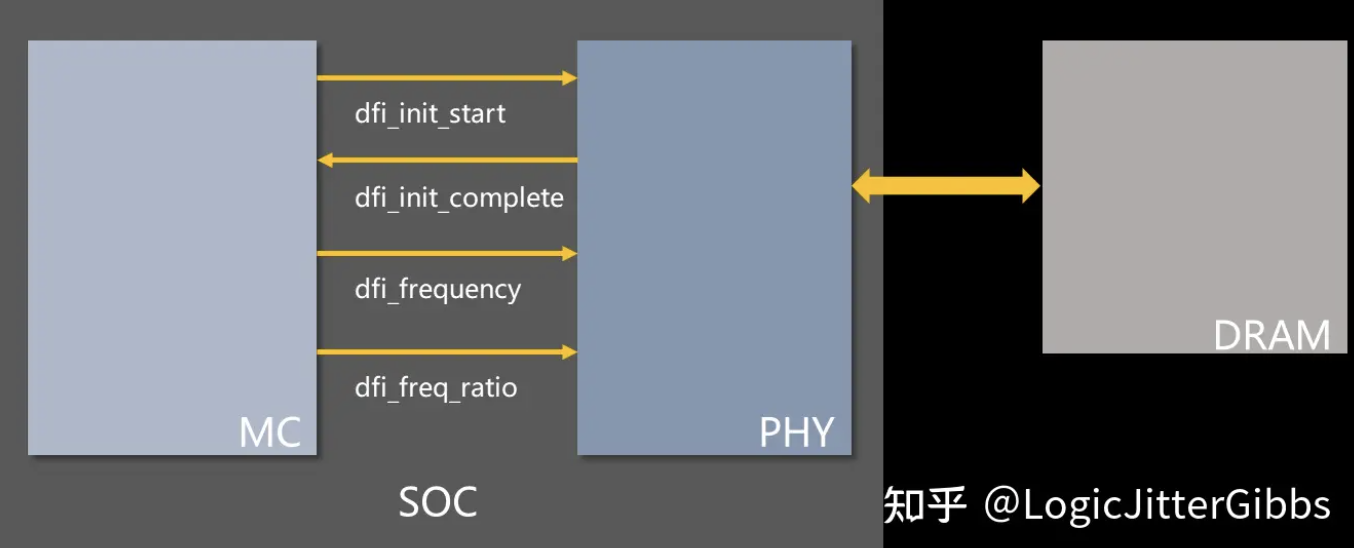

对于支持可变 DFI 与 DFI PHY 时钟频率比的系统来说,MC 置高 dfi_init_start 信号之前,还需要提供给 PHY 有效的初始频率比信号(dfi_freq_ratio)和动态频率比信号(dfi_frequency)。

dfi_freq_ratio 在 DFI 初始化时表示 DFI 系统的初始频率比,并且这个信号数值在之后都不再改变。

dfi_freq_ratio 信号可以由 MC 驱动,也可以由 SoC 提供,或者直接在硬件上将其设为一个固定值。 具体定义参见协议 3.5.8 节。

协议规定 PHY 将从 dfi_init_start 信号有效时的 dfi_freq_ratio 信号获取 DFI 频率比,并用于 PHY 自身初始化。

dfi_frequency 信号由 MC 驱动,用于在初始化和动态频率比变化时,表示 MC 请求的频率比。在初始化时,MC 必须驱动 dfi_init_start 信号为高之前,驱动 dfi_frequency 信号为有效的初始频率比。

可以看到,DFI 初始化时 PHY 需要在初始频率比信号和动态频率比信号上都接收到有效的(也就是相同的)频率比。那么如果两者不同会怎么样?

笔者个人认为这样就违背协议了,PHY 设计中可以不置高 dfi_init_complete 信号作为对 MC 这一行为的回应。

包含上述信号的 DFI 系统结构如下图所示:

1.3 可变频率比 DFI 系统初始化流程

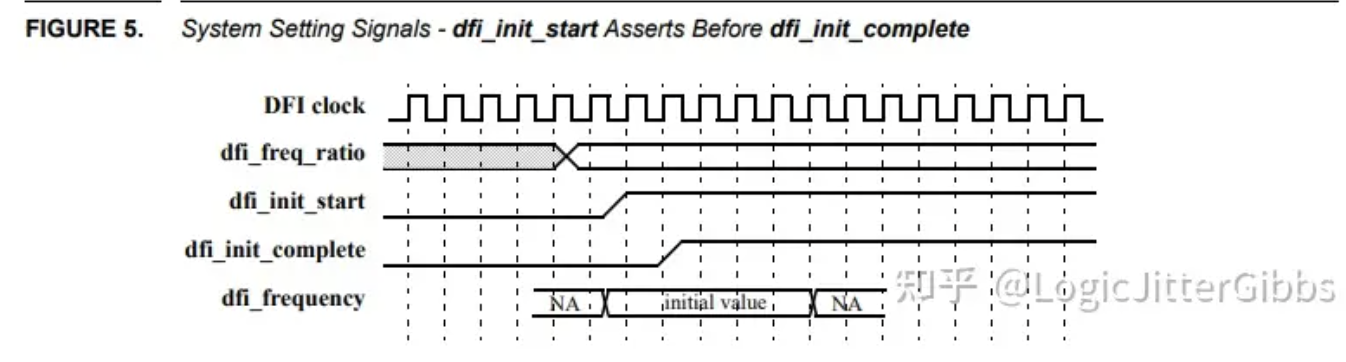

综上,可变频率比的 DFI 初始化流程中的第一步增加额外要求:

- MC 在自身初始化就绪后,置起 dfi_init_start 信号,通知 PHY 其请求 DFI 初始化。【在此之前,确保初始频率比信号(dfi_freq_ratio)和动态频率比信号(dfi_frequency)都已经是有效值。】

上述 DFI 初始化流程如下图所示:

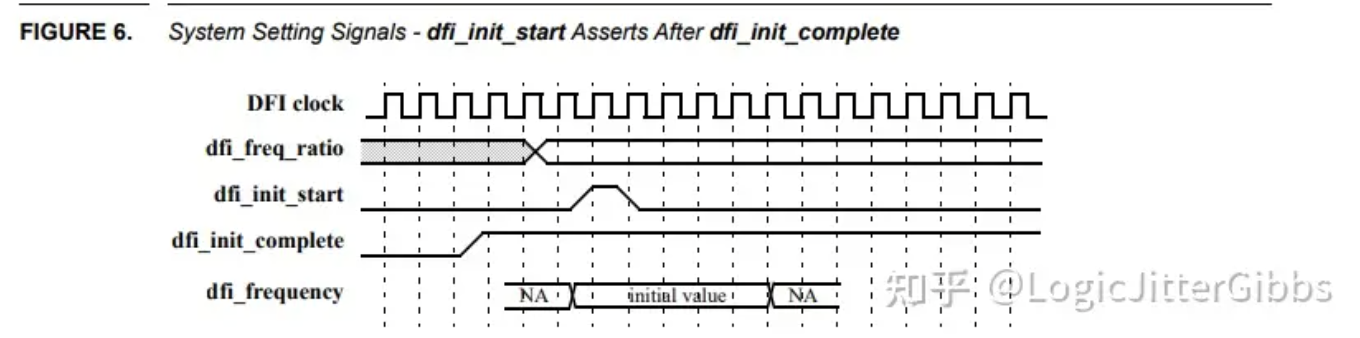

1.4 PHY 独立置高 dfi_init_complete 信号

至此,我们讨论的都是 MC 首先置高 dfi_init_start 信号的主流 DFI 初始化流程。

其实,协议中提到 PHY 也可以在 dfi_init_start 信号之前就置高 dfi_init_complete 信号。前提是 PHY 初始化不需要 MC 提供频率比信息,或者就是 PHY 压根只支持一个固定频率比。

不过,这样的做法笔者觉得在实际应用中并不常见,哪怕 PHY 或者系统中确定只用一个固定频率比。

2 初始化前的 DFI 默认状态

在 DFI 初始化完成之前,即 dfi_init_complete 置起前,DFI 信号保持它们各自的默认值,具体的默认值参见协议 4.0 表 5 控制信号,信号很多,这里节省篇幅就不放上来了,总结来说是这么几条:

- 高电平有效的信号,保持低电平,表示信号无效,反之亦然。

- 与 DFI 协议状态有关的信号,保持其默认状态值,比如 dfi_dram_clk_disable 默认为无效状态。

- 值得一提的是哪些没有定义默认值的信号,比如 dfi_address,显然协议本身没有定义也不会有一个默认地址,所以其默认值不定。但是在 LPDDR2/3/4 中 dfi_address 必须在 dfi_init_complete 信号置高之前处于发送 NOP 命令的状态。

3 结语

本期我们讨论了:

- DFI 初始化流程以及相关信号

- DFI 初始化之前的 DFI 信号初始值

在后续的文章中我们还会讨论相关的内容

- DFI CLK 与 DFI PHY CLK 频率比动态更新

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.30-4.31)

- JESD79-4 第4章 SDRAM命令描述与操作(4.28-4.29)

- JESD79-4 第4章 SDRAM命令描述与操作(4.26-4.27)

- JESD79-4 第4章 SDRAM命令描述与操作(4.25)

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。