4.30 引脚连接性测试

4.30.1 概述

DDR4 SDRAM支持一种连接性测试模式(CT),此方法可大大提高测试PCB上SoC的DDR控制器与DRAM之间连线的电气连接性测试。此模式可与边界扫描设备进行无缝连接,在x16设备上CT模式可在任何容量的设备上使用,而在x4与x8设备中仅能在容量大于或等于8Gb的设备上使用。

与其他测试模式下传统的打寄存器不一样,DDR4 SDRAM测试激励的打入与输出都是在每一个时钟周期串行输出的。DDR4允许并行的执行测试激励从输入引脚的输入与输出引脚输出测试结果,如此就大大提高了连接性测试的速度。在进入CT模式之前Reset_n必须保持高电平,且VrefCA也必须保持稳定。一旦DRAM进入了CT模式,DRAM实际上是一个与控制器异步的设备。当输入的测试激励有效之后的一个固定周期之后,连接性测试的结果将并行的从输出引脚释放。在CT模式中,任何ODT功能都是禁止的。

在退出CT模式之后,DDR4 SDRAM需要被复位。

4.30.2 引脚映射

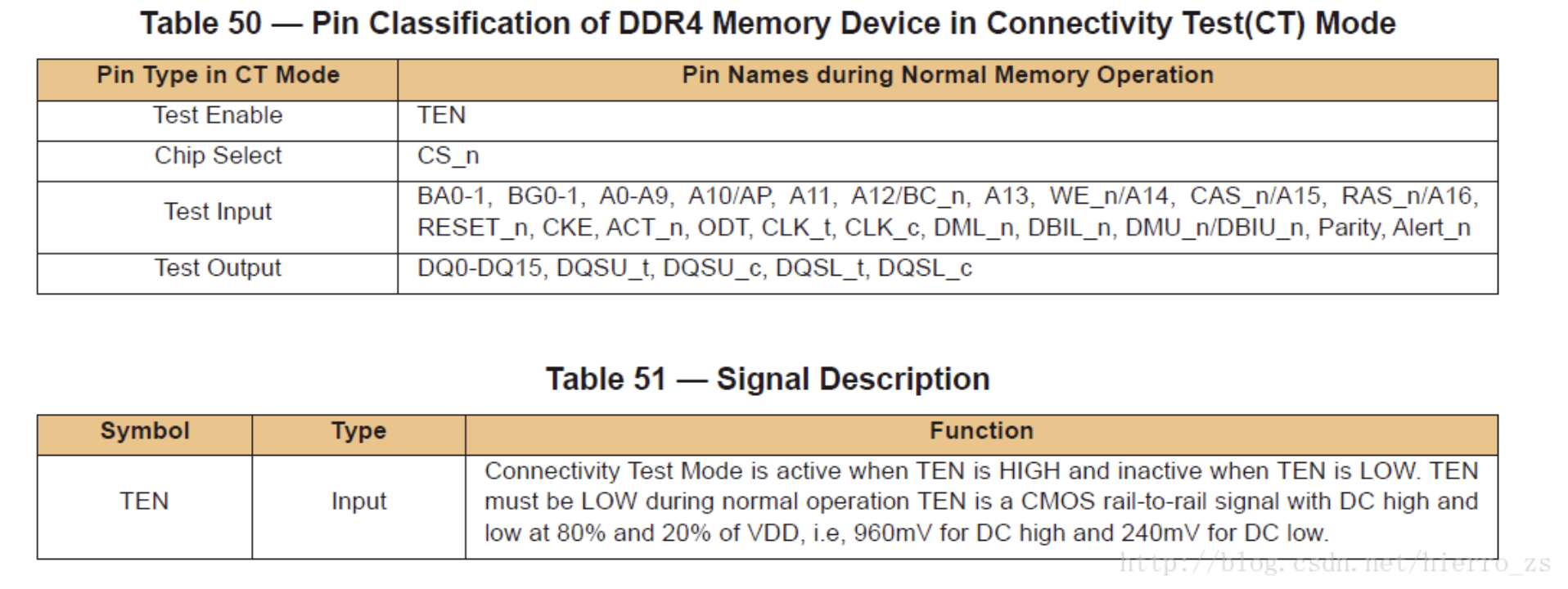

CT模式下仅能测试数字引脚。为了连接性测试的目的,以下几种的DDR4 SDRAM设备的引脚都是用于数字逻辑的。

- 测试使能(TE)引脚,高电平有效。此引脚有效将使DRAM进入CT模式。在此模式下,DDR4 SDRAM内部所有的功能都将被旁路,并且在外部可控制逻辑看起来所有的输入输出引脚都将成为测试相关的引脚。TE引脚是连接性测试功能专用的引脚,且在普通操作中此引脚是不使用的。

- 片选(CS_n)引脚,低电平有效。此引脚有效时,将使能DDR4 SDRAM的测试输出引脚。当此引脚无效时,DDR4 SDRAM的测试输出引脚将处于三态。DDR4 SDRAM中的CS_n引脚在CT模式上也是作为CS_n来使用的。

- 测试输入引脚,在DDR4 SDRAM普通操作中的一组输入引脚将作为测试输入引脚使用。此组引脚在CT模式下用于接收测试激励输入。

- 测试输出引脚,在DDR4 SDRAM普通操作中的一组输出引脚将作为测试输出引脚使用,此组引脚在CT模式下用于释放连接性的测试结果。

- Reset_n,与普通模式下相同,在整个CT模式下此引脚都要保持高电平。

下表为CT模式下各个引脚的详细说明。

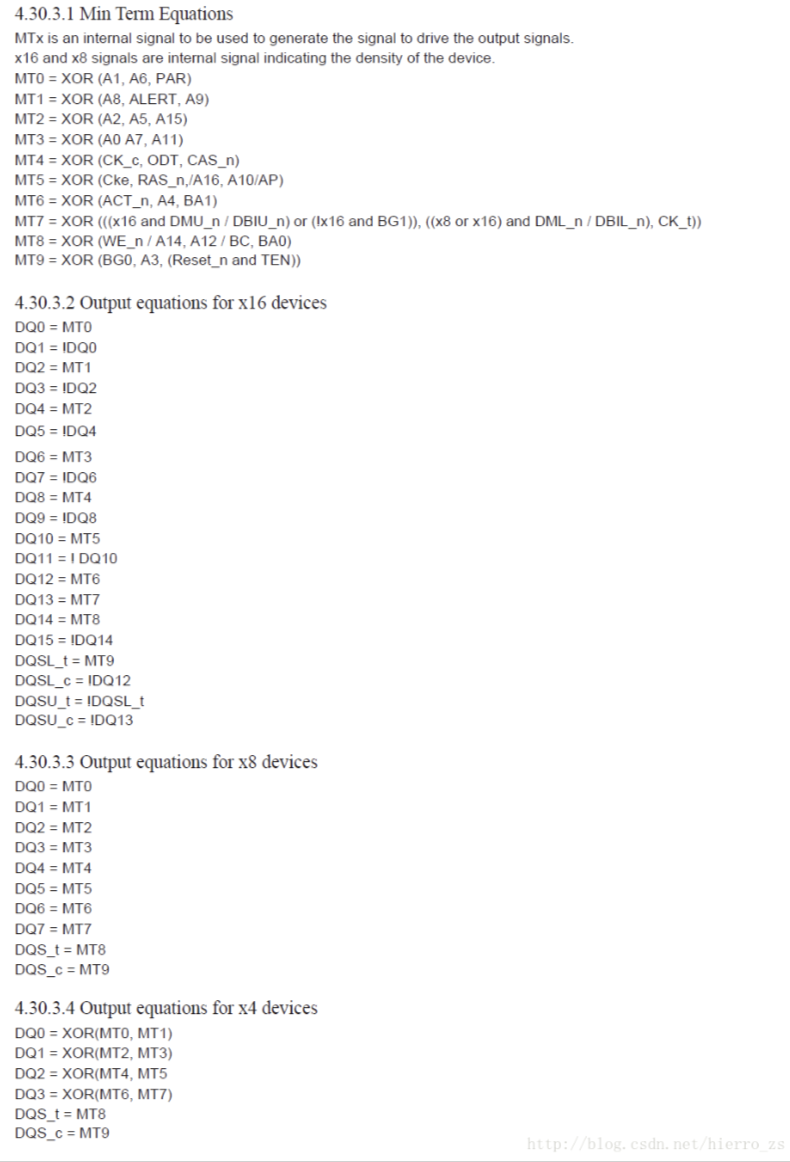

4.30.3 等效逻辑

4.30.4 时序要求

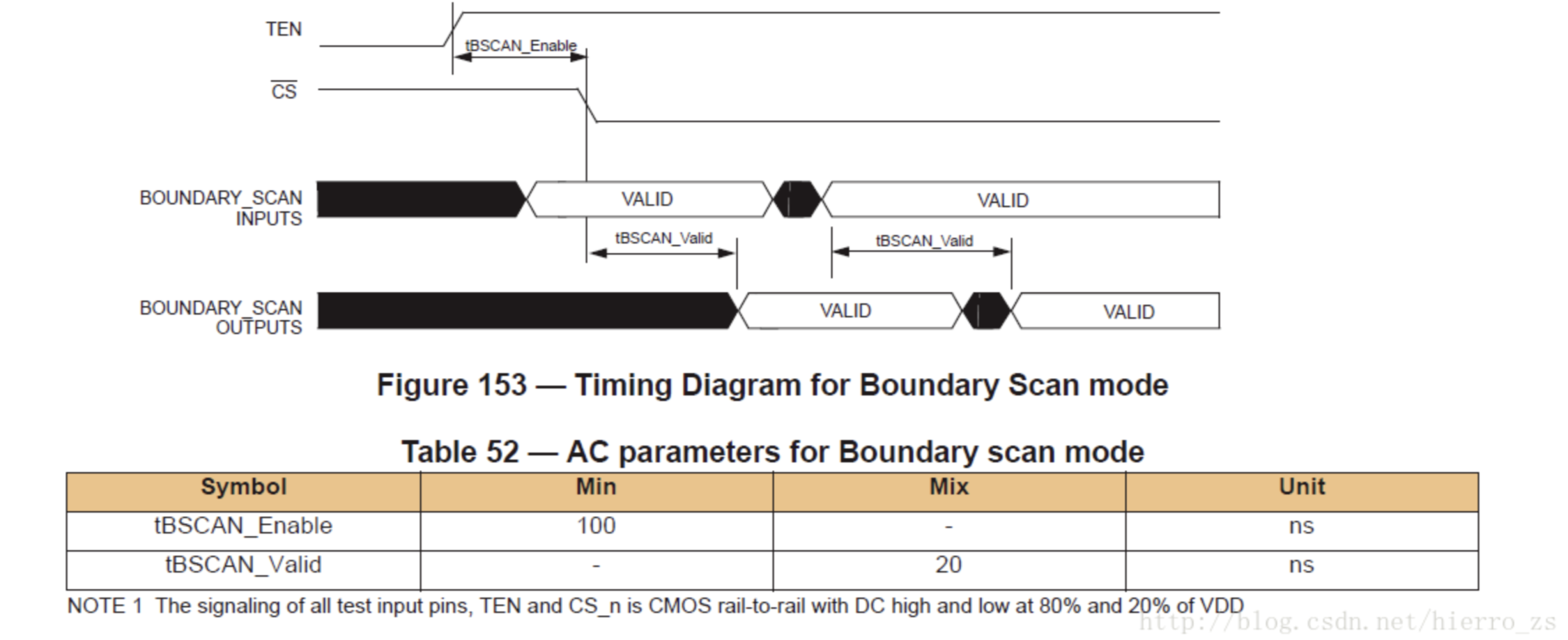

在使能TEN之前,所有的电源都必须保持有效与稳定。

一旦TEN有效即可进入CT模式,在时间tBSCAN_Enable之后,CK_c与CK_t都将被DRAM忽略。在CT模式中,存储阵列中将不会执行刷新操作,所有内部(自刷新)或外部(自动刷新)触发的刷新命令都将被推迟。

TEN可在任何状态下使能DRAM的CT模式,包括自刷新与断电。在CT模式中,测试输入引脚类型是CMOS,轨到轨DC的高低电压分别是VDD的80%与20%。

TEN也能在CT模式的任何时间无效,使DRAM退出CT模式。一旦DRAM退出CT模式后,内部状态将处于未知状态,且存储阵列中的数据也是处于未知状态。因此,在退出CT模式后DRAM需要重新进行复位与初始化序列。

在TEN为高电平,CS_n处于低电平时,从测试引脚输入测试激励开始,需要经过tBSCAN_valid时间后,测试输出引脚才会稳定输出。如下图所示。

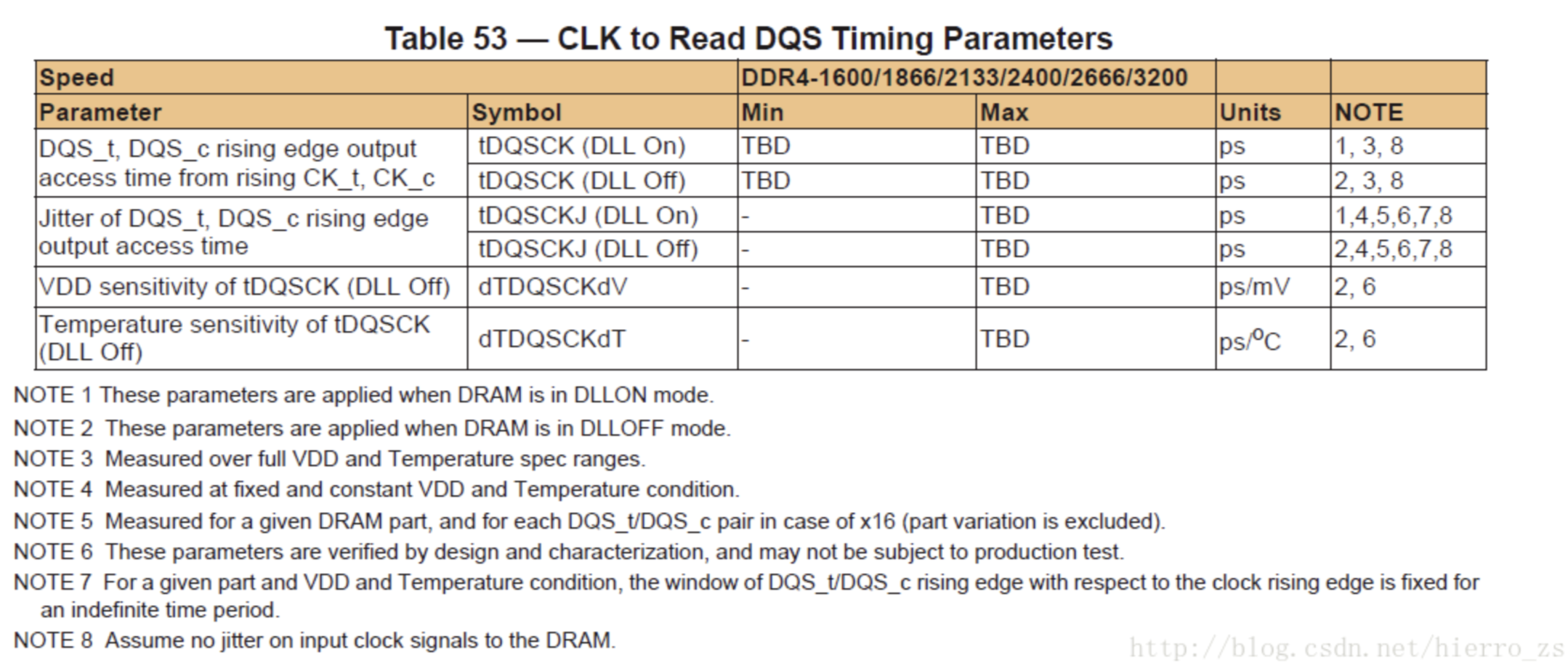

4.31CLK与读DQS的时序关系

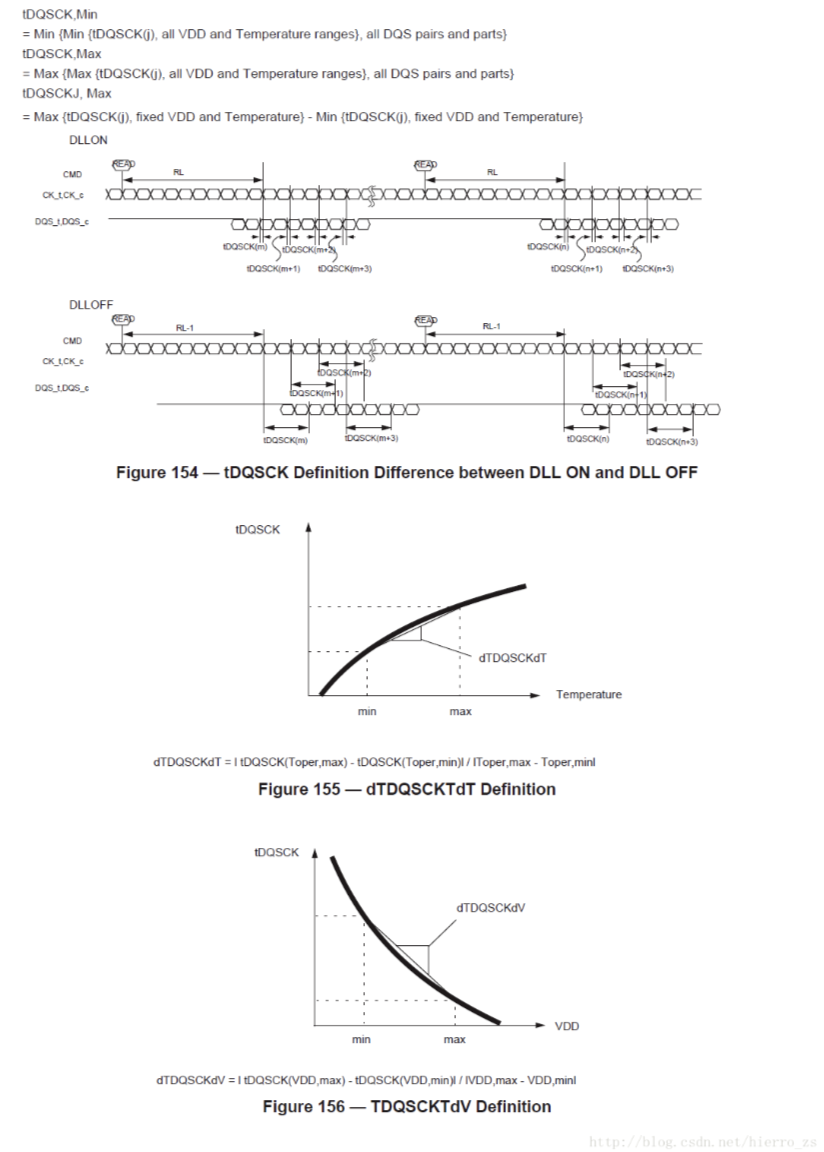

DDR4 SDRAM支持DLL-off模式,以下列表中的时序参数可用来描述CLK与读DQS之间的时序关系。

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.28-4.29)

- JESD79-4 第4章 SDRAM命令描述与操作(4.26-4.27)

- JESD79-4 第4章 SDRAM命令描述与操作(4.25)

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

- JESD79-4 第4章 SDRAM命令描述与操作(4.20-4.23)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。