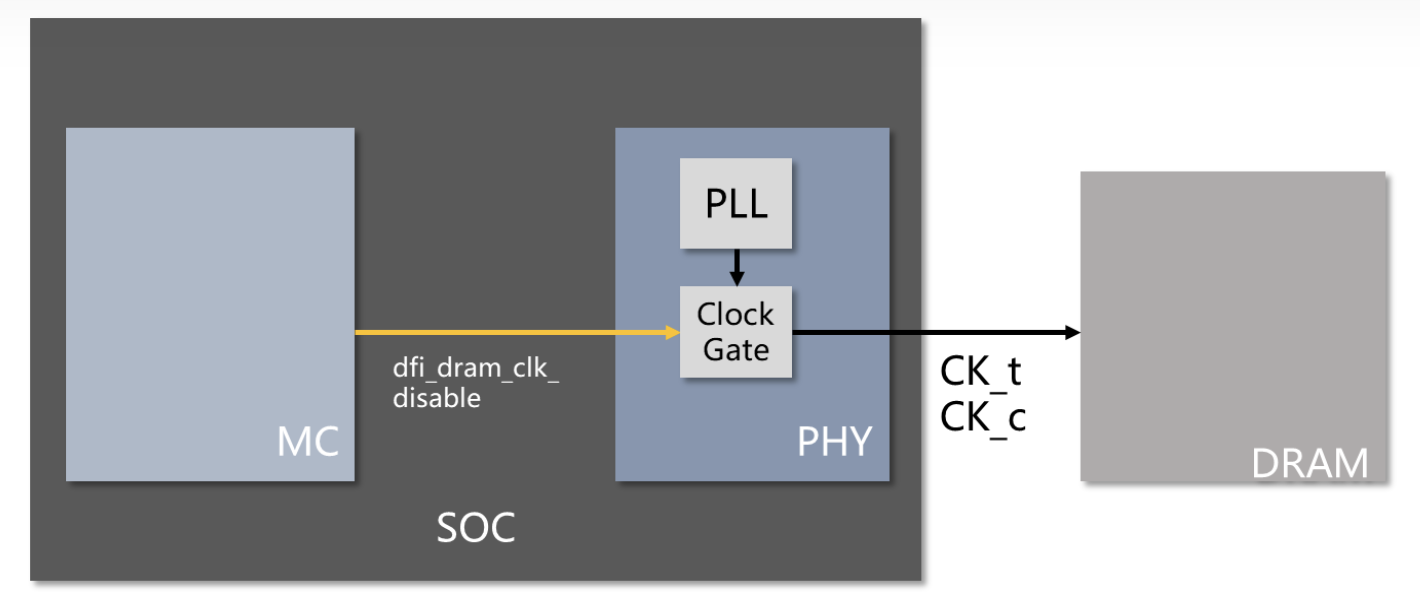

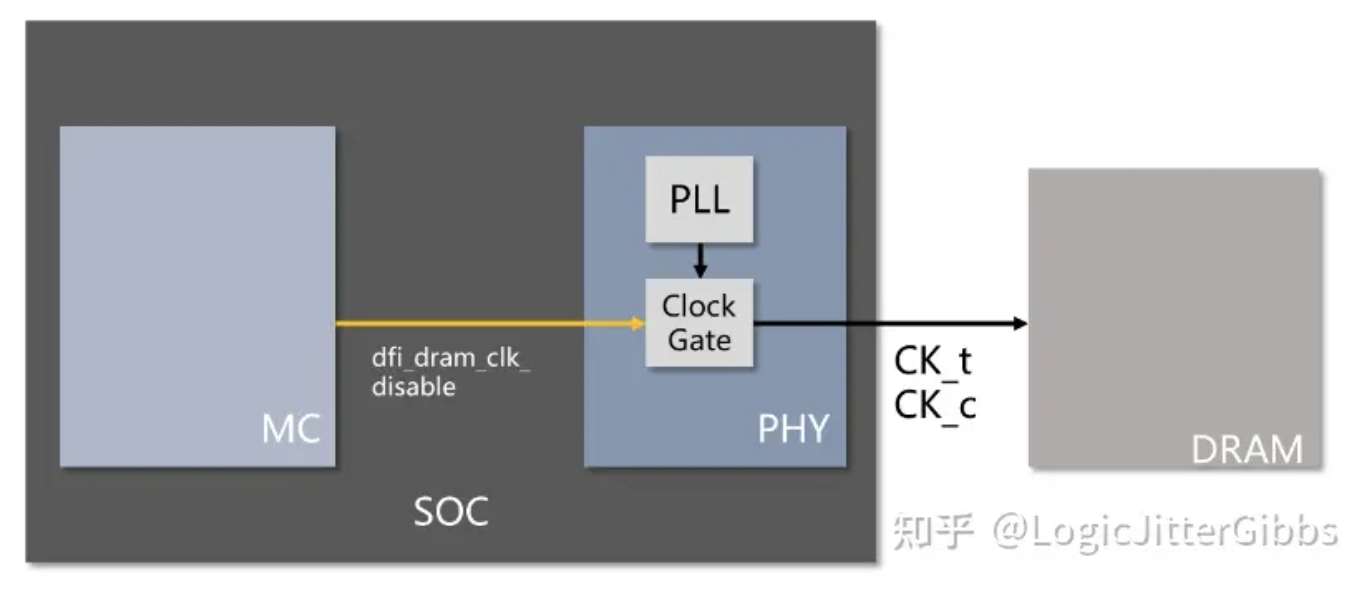

本期介绍 DFI 协议一项功能,MC 通过 DFI 信号停止 PHY 给 DRAM 的时钟输出。

本节基于 DFI 协议 4.8 节的内容(协议 4.0 版本)。

应用场景

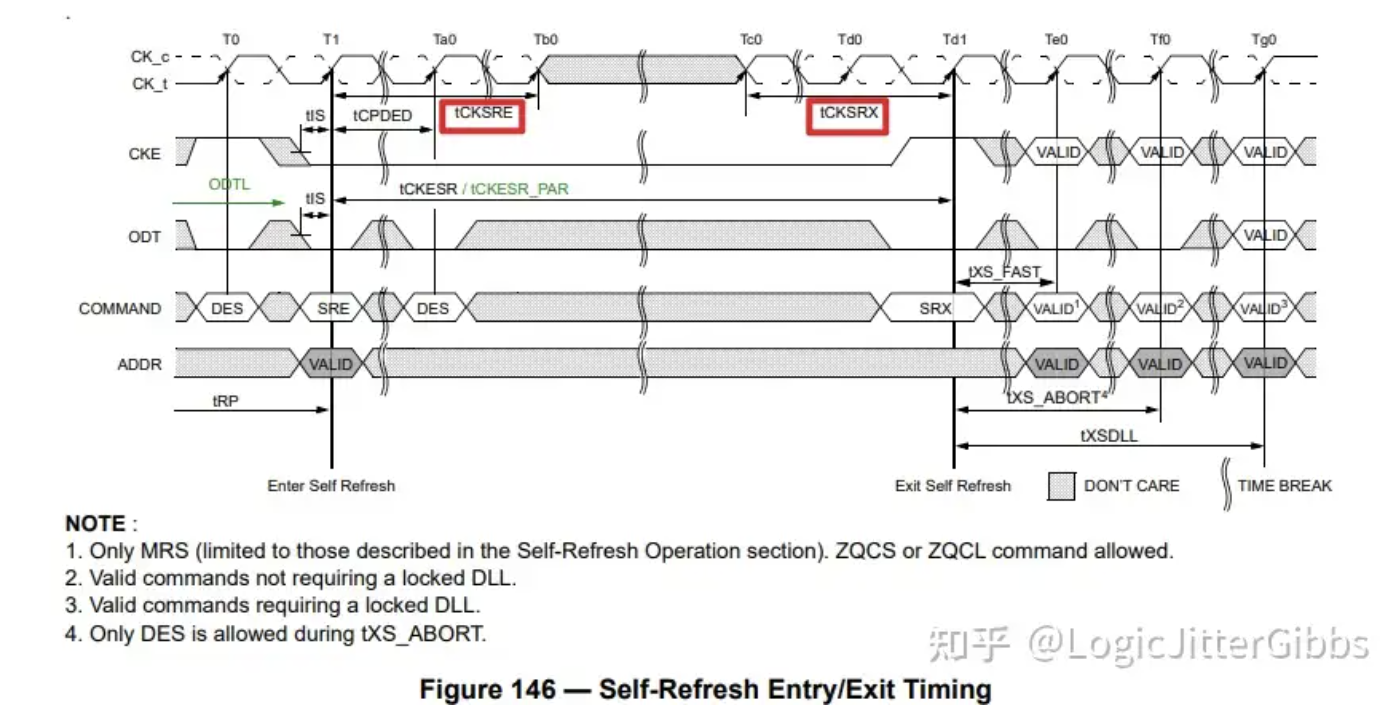

当 DRAM 处于自刷新状态时,系统可以保持提供给 DRAM 的 CK 时钟,或者关闭时钟供给。一般来说,停止 CK 时钟能够进一步降低 DRAM 和系统的功耗,毕竟 CK 时钟是一组高频的差分时钟对(DDR4-3200 为 1.6GHz )。

读者可以通过这篇文章了解更多关于 DRAM 自刷新的内容,其中写道:

DRAM 在自刷新期间, 只在乎 CKE 信号(什么时候退出自刷新)和 RESET_n 信号 (什么时候复位),其他信号一概不在乎,包括外部输入的时钟信号 CK。

DFI 的 DRAM 时钟停止功能就可以用于,MC 指示 PHY 是否需要在自刷新期间关闭 DRAM 时钟。

系统在通过 MC 使 DRAM 进入自刷新状态的流程中,如果希望关闭输出给 DRAM 的 CK 时钟,那么置起 dfi_dram_clk_disable 信号。MC 在退出自刷新状态时,再在合适的时候置低这一信号。

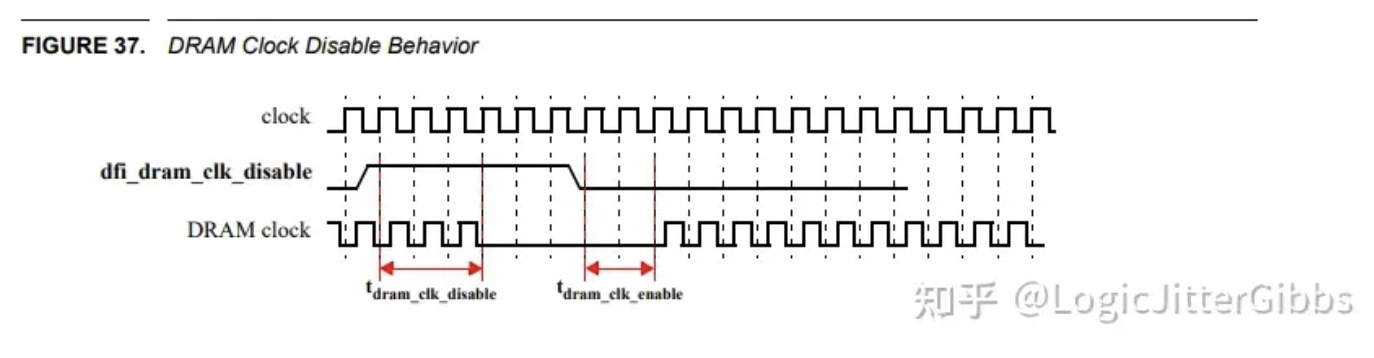

时序与时序参数

dfi_dram_clk_disable 信号关闭/恢复 DRAM 时钟的时序很简单,当 MC 置高 dfi_dram_clk_disable 信号后,PHY 在 t_dram_clk_disable 个时钟周期后关闭 DRAM 时钟。MC 置低 dfi_dram_clk_disable 信号后,PHY 在 t_dram_clk_enable 个时钟周期后恢复 DRAM 时钟。

- t_dram_clk_disable

- t_dram_clk_enable

结语

本期我们讨论了:

- DFI DRAM 时钟停止功能和应用场景

- DFI DRAM 时钟停止功能的时序参数

作者:LogicJitterGibbs

原文:知乎

相关文章推荐

- DDR 学习时间 (Part S - 1):运行 Micron DDR3 仿真模型

- DDR 学习时间: DDR 开源实现 高云 GW2A FPGA 的 DDR3 低延迟控制器

- DDR 学习时间 (Part I - OS1):DDR IP 开源实现 DDR5 PHY 数据通路

- IC 工程师视角:恒玄科技 2023 年报

- DDR 学习时间 (Part C - 5):DFI 架构

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。