从时序时间窗到人生机会窗

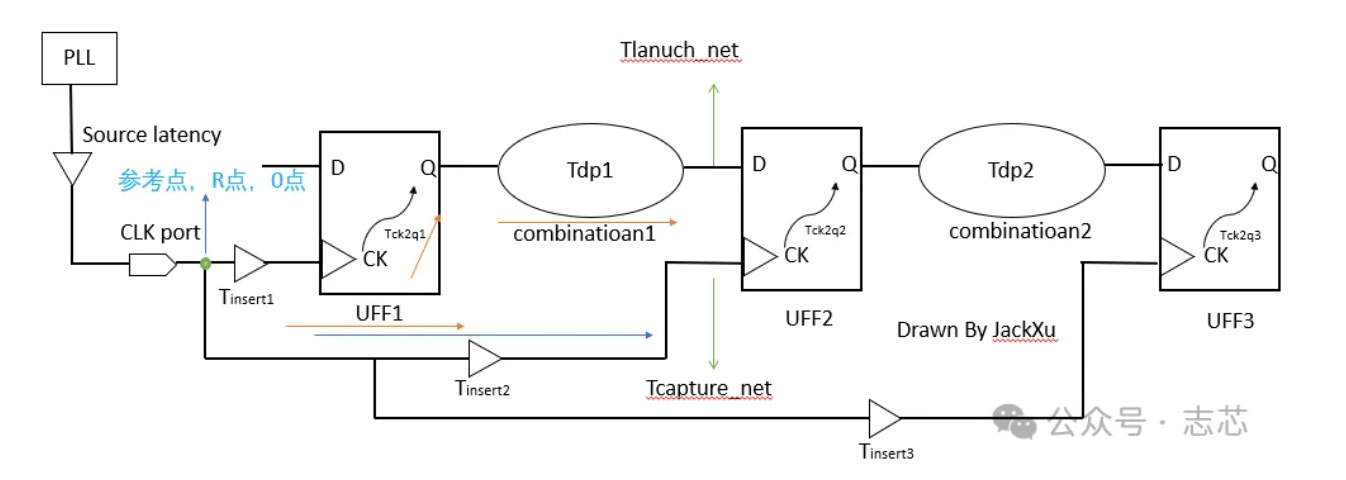

时序分析归根揭底就是时间窗分析,时序修复归根结底就是时间窗修复。如下图所示,是时序路径示意图,以UFF1→UFF2的路径为例;如果该路径既满足建立时间要求又满足保持时间要求,则等价于该路径需满足如下时间窗公式:Thold+ Tsetup < Tck2q1 + Tdp1+Tsetup + (Tlaunch_net - Tcapture_net )- Tclk_skew < Tcycle;其中Thold是UFF2的时序库中的保持时间要求,Tsetup是UFF2的时序库中的建立时间要求,Tck2q1是UFF1的时钟端口到数据端口的延迟,Tdp1是UFF1和UFF2之间的组合逻辑延迟,Tlaunch_nets是launch path的net delay,Tcapture_net 是capture path的net delay,Tclk_skew 是UFF2和UFF1的时钟长度的差值(就是clock skew)。

作为一个芯片工程师,觉得时序分析中的时间窗和人生的机会窗有许多共通之处,且听我娓娓道来。

三级流水如家族三代,需要彼此给对方留足时序余量

常见的三级流水是“取指”“译码”“执行”。

三级流水对应三级时序路径,为了满足整个芯片的频率要求,每一级的时序必须都收敛。

芯片中三级流水之间的时序并不是孤立的,从前端和后端的角度,分别可以用re-timing和useful skew的方法从前一级借用时间窗余量;三级流水也如人生的家族三代,上一辈人取得的成就和家资撑起了后辈的起点,他们的人生容错率也更高;如果上一辈的“时间窗“没有留足,我们之一代人起点自然是hard模式,必须在有限的资源范围内,竭力修复我们自己的时间窗。

如果是cell density太大引起时序违例,那说明该挪位置了

如果布局cell density太大引起route congestion和detour route,自然时间窗会非常恶化,此时再保持原来的module分布格局就不合适了,需要调整floorplan的总体规划,把timing path从拥挤和闭塞中解救出来;或者采用特殊的物理约束(partial blocage,keep-out margin等)方法释放出违例路径周围的空间。这跟我们打工人一样,人才放错了位置可能无法发挥,调整规划,找到合适的位置才能发挥最大价值,这个位置包括不同的城市等物理位置和不同的岗位等职业位置。

没有时间窗可以借用,也没有位置可以腾挪,那可能需要换low VT

所谓VT,就是MOS管栅极阈值电压,阈值电压越低的相同类型的标准单元,其速度越快,这样就可以修复出时间窗出来。但是这种“快”是有代价的,这种low VT的单元,其泄露功耗更大,对自身的能量消耗很大,也容易发热,引起潜在风险。这也跟人生一样,当我们选择不多,手牌不好时,想要修复人生的时间窗,燃烧自己,吃更多苦,留更多汗,成为了一种选择。

当用了low VT依然不行的时候,此时可能需要换赛道了

当low VT也用了,违例路径的时间窗还没有修复,怎么办呢?当苦也吃了,汗也流了,人生状态还没有改观,怎么办呢?

此时可能说明normal track(普通路径)已经不行了,可能需要non-default路径了,使用non-default rule对该违例路径单独绕线,节省出更多的net delay来修复时间窗,也是一种方法。Non-default rule就是非默认规则,就如人生选择的打破常规,尝试标新立异的新赛道。

END

作者:Jack Xu

文章来源:志芯

推荐阅读

更多IC设计干货请关注IC设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。