很多朋友可能都曾惊叹于此前的一段Cortex-M0+处理器在25MHz系统频率下“仅凭一己之力”拖着宛如细狗一般带宽的SPI屏幕狂飙直方图的视频:

Memcpy/memmove 的改进使用新的加载/存储传递的另一个好处是,在生成代码时,我们不再需要明确生成加载/存储对指令,因为我们可以依靠优...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

在 GCC 14 版本中,与所有其他版本一样,Arm 与社区紧密合作,推出了改进很多的编译器。然而,这次发布与以往有些不同,我们退后一步,...

GCC 13 编译器现已发布,并为大家带来了一些好东西。Arm 工程师和 GCC 社区为发布这一版本付出了艰辛的努力,本博客将介绍 GCC 13 中值...

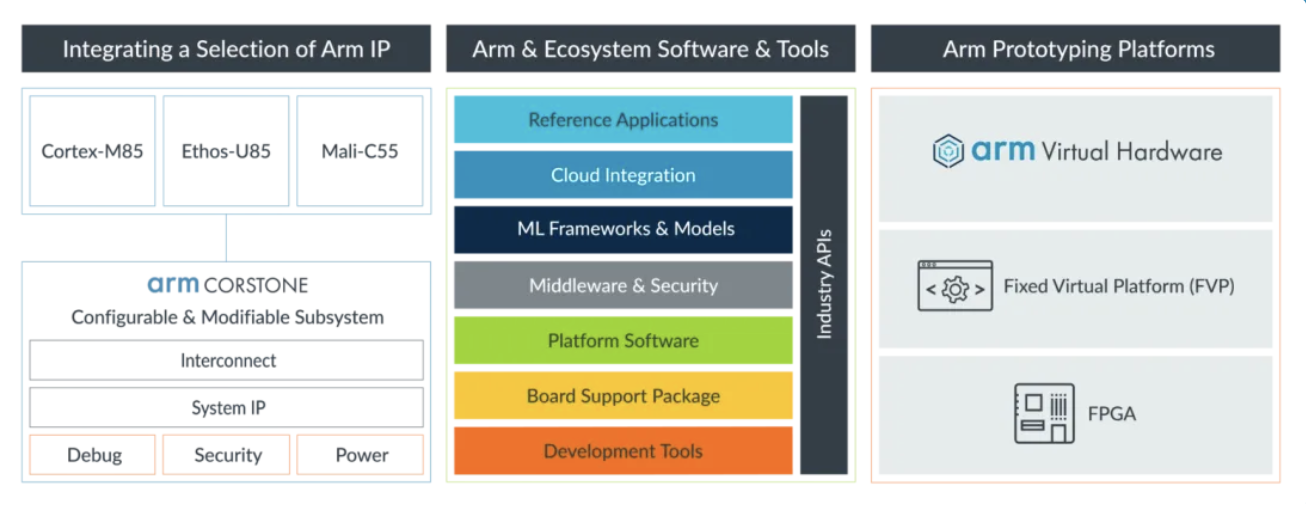

如今,嵌入式、物联网 (IoT) 和边缘机器学习 (ML) 应用广泛基于 Arm 平台运行。目前有超过 45 家芯片供应商提供 10,000 多种基于 Arm Co...

在不断发展的 IT 基础设施领域,从广阔的云网络到资源有限的边缘环境,企业在各种基础设施部署中部署应用程序时会遇到无数挑战。每种部...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

内存分区和监控(MPAM)Arm 架构补充允许使用 PARTID 标识符对内存资源(MPAM MSC)进行分区。这允许操作系统和管理程序等特权软件在硬...

如今的编译器在自行生成高度优化的代码方面已相当出色。不过,在某些情况下,作为程序员的你可以帮助编译器生成更好的代码。本博文将介...

在2024年的Marvell AI投资者日上,Marvell,这家在AI加速器领域迅速崛起的公司,不仅展示了其在高增长领域的投资案例,还宣布了在美国赢...

从全球角度来看,动物和植物基因组学是保护我们多样化环境的关键,也是在干旱和疾病时期养活我们不断增长的人口的关键。

随着语音、音频和视觉功能融合到物联网 (IoT) 中,联网设备与其周围环境交互、解读和感知的方式发生了彻底的变化。未来的物联网市场蕴含...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

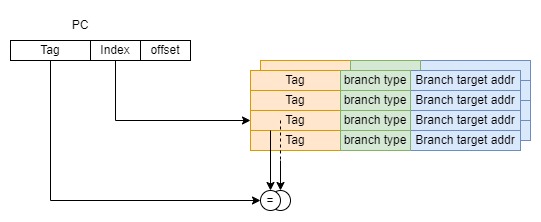

现代CPU须在指令预取pipeline stage具备性能良好的分支预测器,以给pipeline后端供应充足有效的指令。大多数CPU会使用 BTB(Branch Targ...

Defacto SoC Compiler 是用于片上系统集成的领先工具,允许用户根据相关约束条件将各种 IP 块(如 CPU 内核和互连结构)组合在一起,并...

Arm 每年发布两次最新版本的 Arm Compiler for Linux。 这包括一个完整的用户空间编译工具链,适用于基于 Linux 环境的 C、C++ 和 Fortr...

一位客户要求澄清 Eigen gemm 基准的执行情况。特别是当 L1D_CACHE_WR 的 PMU 值低于 L2D_CACHE_WR 时。在这种情况下,L1 数据高速缓存...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

LLVM 18.1.0 于 2024 年 3 月 6 日发布 。 在多项新功能和改进中,Arm 提供了对最新 Armv9.5-A 架构的支持,以及大量性能和安全增强功能...