异步复位时序收敛技术

前一篇文章讨论了具有大latency 复位分配网络的高速设计复位释放的复杂性。在这里,我们讨论两种缓解此时序问题的技术。这两种技术都适用于ASIC和FPGA设计。

异步复位流水线

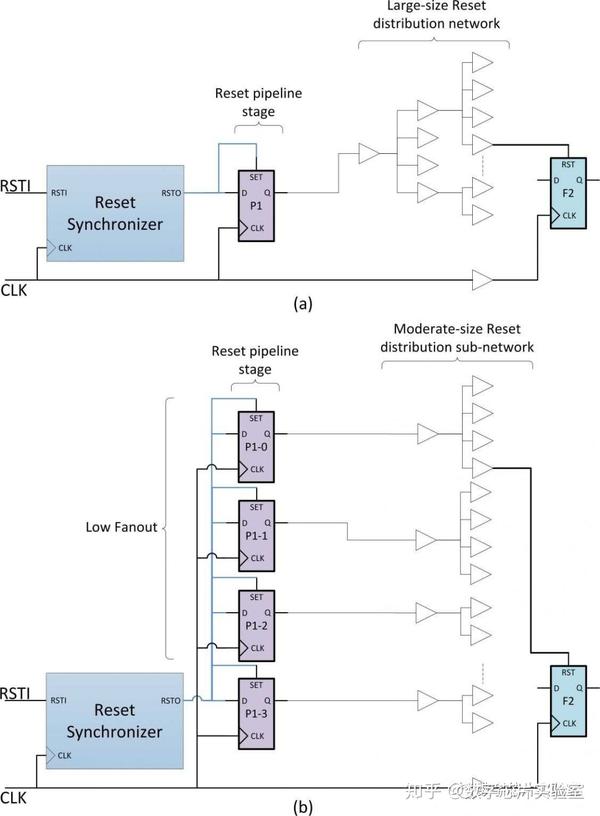

处理异步复位释放时序问题的一种方法是对复位树进行流水线操作。在每个同步器之后增加一个额外的异步置位触发器级P1(图a)。触发器的SET和D输入都连接到来自复位同步器的高电平有效复位信号RSTO。

该方案在复位释放路径上增加了额外的单周期延迟。对于大多数应用来说,这种技术引起的复位延迟通常是可以接受的,因为每次上电只会复位一次。

必须限制同步器被复制以防止如上一篇文章提到的在不同周期复位问题,但是流水线触发器P1可以被复制,其受到MAX\_FANOUT约束。最大扇出约束的示例如图b所示。

P1触发器由综合工具自动复制,为复位分配网络创建四个子网络。每个子网络的延迟都低于原始的复位分配网络。

这种异步复位流水线技术可针对任何设计大小进行扩展,并且无需更改设计,因为综合工具会自动复制P1触发器。当单级流水线时序不收敛时,可以增加更多的流水线级P2-PN并且用不同的MAX\_FANOUT来约束。

异步复位时钟门控

解决高扇出复位网络时序问题的另一种技术采用时钟门控。该技术使用更大的复位latency来折衷获得更好的复位时序。

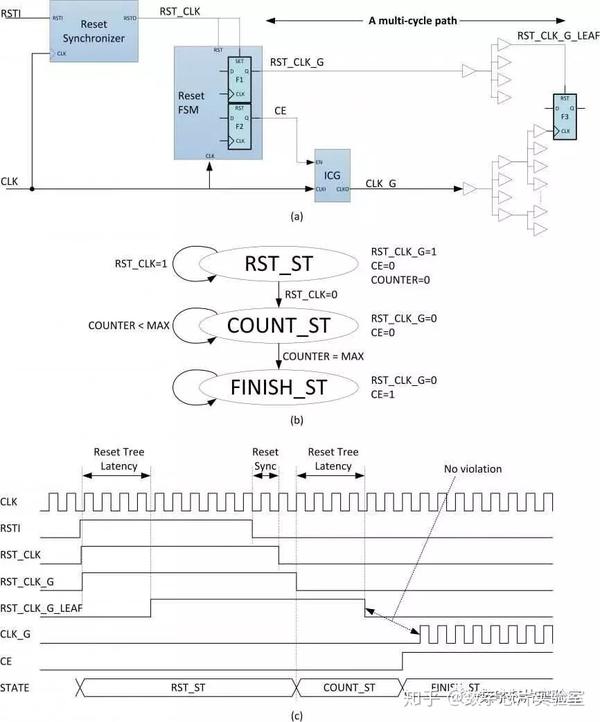

异步复位时钟门控如上图所示。异步复位RSTI首先由标准复位同步器同步,产生一个复位释放被同步的复位信号RST\_CLK。RST\_CLK异步复位连接到一个小的“ Reset FSM”,它负责将时钟选通到整个设计(FSM本身除外)。时钟门控通过ICG单元( integrated clock gating cell)来实现,产生门控时钟CLK\_G。由于FSM包含很少的触发器,扇出很小,不会产生之前复位网络的大latency。

图b中所示的状态机和图c中的波形图描述了异步复位时钟门控操作。一开始RSTI被置位,整个芯片异步复位,包括Reset FSM。在该阶段,时钟CLK可以是无效的。由于复位网络延迟较长,复位可能需要一段时间才能复位整个芯片,但最终所有触发器都会复位。复位FSM复位为RST\_ST状态。

RSTI释放后,复位同步器将RST\_CLK的复位释放同步到CLK上升沿,防止Reset FSM的时序违规。在下一个周期,FSM进入COUNT\_ST状态,同步释放RST\_CLK\_G去复位设计。由于CLK\_G时钟在此状态下被门控,因此在此时不会有时序违例。

计数器阈值被设置为复位分配网络上最坏情况下的复位延迟。一旦计数器达到其阈值,FSM就会移动到下一个状态FINISH\_ST,将CE设置为高电平,将时钟释放到设计的其余部分,这个时候复位RST\_CLK\_G\_LEAF已经稳定,因此不会发生时序违例。

该技术最小化了复位分配网络所需的资源。在工程实践中设置RST\_CLK\_G端口到所有触发器复位端为多周期约束,以匹配FSM的计数器阈值。由于阈值可以是任意的,因此容易满足该约束。

除了减轻时序问题之外,该技术还可以减少在复位网络切换期间的功耗。

本文译自:

Asynchronous reset synchronization and distribution – ASICs and FPGAs

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/rl15y1COCcKNKgxxCJ-aFQ

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏