源自微信公众号 “数字芯片实验室”

SDC(Synopsys Design Constraints)是一种基于Tcl的格式。 SDC文件中的所有命令都符合Tcl语法规则。

SDC文件用来传达EDA工具设计意图,包括时序、面积和功耗等。 SDC文件包含以下信息:

•版本(可选)

•单位(可选)

•约束值

•约束对象

•注释(可选)

在SDC文件中不包含加载或链接设计的命令。所以,在加载SDC文件之前必须先加载你的设计。

1、指定SDC版本

如果未指定SDC版本,则版本取决于读取SDC文件的EDA工具。 指定SDC文件中的版本变量,可确保SDC文件在不同工具之间的兼容性。

要在SDC文件中指定SDC版本,在文件的开始使用以下命令:

set sdc\_version value

2、指定SDC单位

set\_units命令指定SDC文件中电容,电阻,时间,电压,电流和功耗等单位。

3、指定设计约束

使用约束命令来指定设计约束。如果命令太长,可以通过反斜杠字符(\)将命令分为多行。

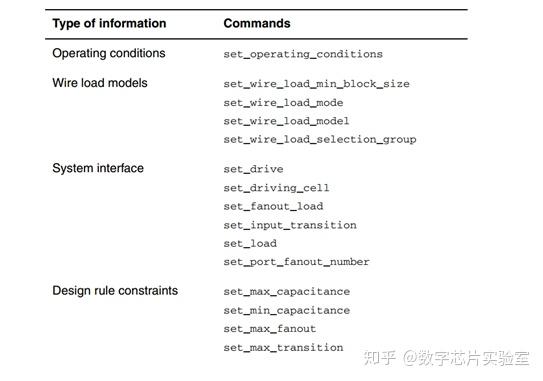

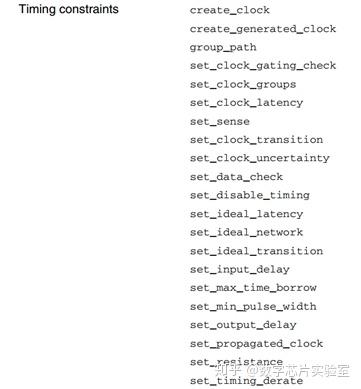

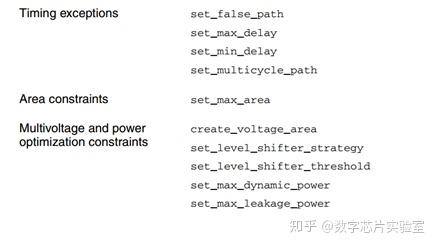

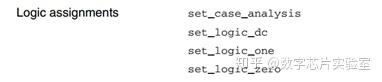

SDC约束命令由下表组成。

需要注意的是:SDC格式只是各个工具支持命令的一个子集。

4、指定约束对象

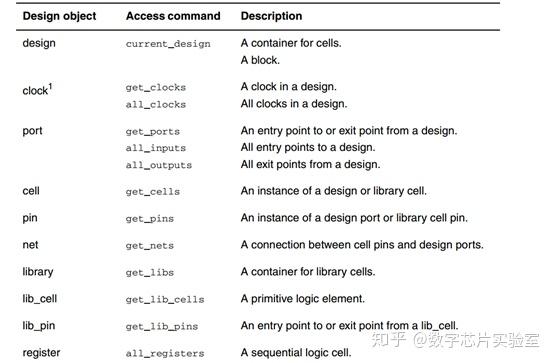

大多数约束命令都需要设计对象作为命令参数。

如果当前设计中有一个名为U1的单元,可以通过命令

[get\_cells U1]

找到。

下表SDC格式中寻找设计对象的命令。

同时,可以使用Tcl列表或**通配符(?、*)**指定多个对象。

默认情况下,当前设计约束的参考点是顶级设计。我们可以使用**分隔符(/)**来约束层次结构化设计。

5、添加注释

我们可以请使用#将注释添加到SDC文件中。

例如,

\# This is an SDC comment line.

create\_clock -period 10 [get\_ports CLK] ; #comment fragment

6、管理大型项目SDC文件

当设计非常大时,SDC文件可能会得很大。减少SDC文件大小的一种方法是压缩文件

read\_sdc命令自动检测gzip压缩文件并解压缩,然后读取它们的文件。 例如,

read\_sdc design.sdc.gz

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/-rjAXdwK5vO6i58C3kR\_aw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏