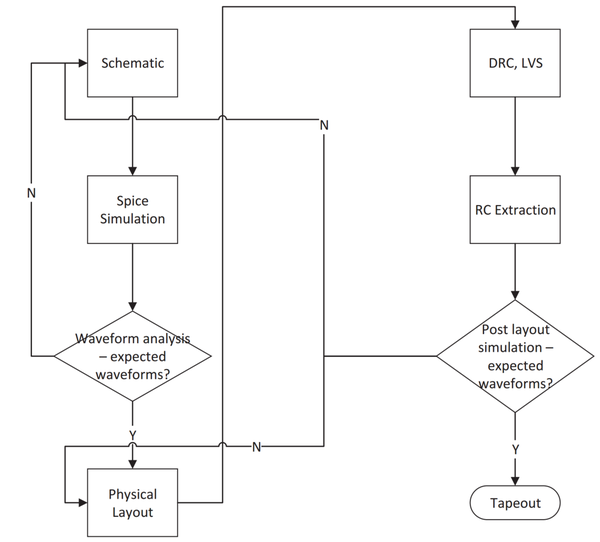

顾名思义,模拟/全定制设计流程用于设计模拟或者全定制电路。 全定制电路是指使用晶体管,电阻和电容设计的电路,但是全定制电路不一定是模拟电路。

1.原理图

(a)模拟/全定制电路设计者使用计算机辅助设计(CAD)软件,例如Cadence Composer等工具绘制模拟或全定制设计的原理图电路。

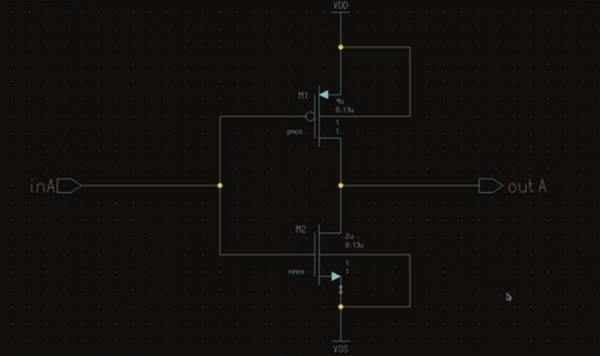

(b)原理图可以由晶体管,逻辑门,电阻,电容和电感组成,下图是反相器的示意图

2. Spice仿真

(a)这个过程是指对电路施加激励,分析电路的行为以确定电路是否符合预期。

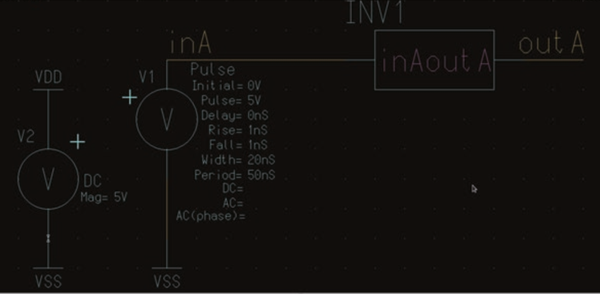

(b)为了能够仿真电路,需要一个测试平台。 下图中反相器的输入为5V,宽度为20 ns

3.波形分析

(a)分析在仿真中观察到的电路行为,以确定电路是否按预期运行。

(b)如果DUT的行为不符合预期,那么设计人员需要修复原理图或者Testbench。这是一个迭代的过程,直到设计者满意为止。

4.物理版图

(a)该过程是从原理图到版图的转换,从而可以制造芯片

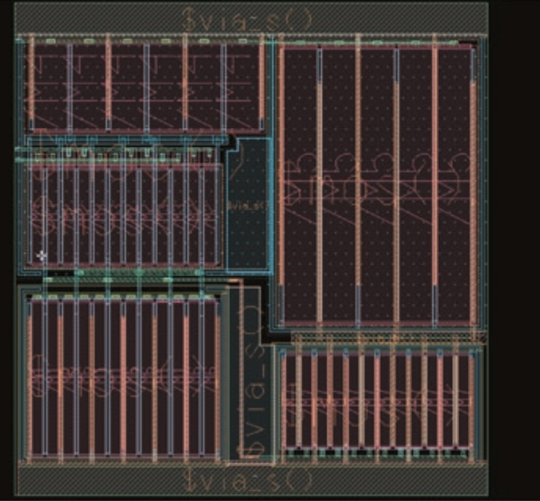

(b)不同的物理层,如金属,多晶硅,有源层等共同形成设计版图,如下图

5. DRC,LVS

(a)设计规则检查(DRC)检查物理布局中不同图层的设计规则,例如最小金属宽度。制造工艺技术越先进,需要检查的设计规则越多。

(b)通常,使用Mentor的Calibre进行DRC检查。当存在DRC错误时,设计人员根据突出显示的错误位置来更改布局。重复迭代,直到所有的DRC错误都被修复。

(c)在DRC问题clean后,需要进行layout versus schematic检查(LVS)。在此过程中,验证物理布局是否与原理图匹配。如果在LVS期间发现任何不匹配,则必须在物理布局中修复问题。重复迭代,直到LVS没有错误。

6. RC参数提取

这是物理布局完成后的一个重要流程。 在这个过程中,提取物理布局中晶体管和互连线的电阻和电容参数(RC)。 然后,生成一个包含电路元件和RC参数值的post layout

网表。

7. post layout仿真

(a)这是流片前最后的流程。

(b)使用相同的测试向量重新仿真post layout网表,并观察和分析波形以确定电路行为是否符合预期。

(c)有时候,由于RC寄生参数,post layout网表仿真行为不符合预期。设计师必须在版图级别或原理图级别上修改,并重复之前的步骤,直到post layout网表仿真通过。

(d)当post layout网表仿真通过时,生成GDSII文件并传递给工艺厂进行制造

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/TrMMHUiEMCalc8nvvkuSsA

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏