我们都知道在数字IC设计流程中cell(std,IO,IP)的时序(timing)、面积(area)、功能(functionality)和功耗(power)信息都包含在lib库里面,其中时序信息最为关键。

以最简单的反相器为例,所谓cell的时序信息,即图中的传播延时Tr和Tf。

• Tr : Output rise delay

• Tf : Output fall delay反相器cell的延时取决于两个因素:

输出负载(output load),即输出引脚的电容负载

输入信号的过渡时间(input transition time)延迟值与负载电容直接相关。负载电容越大,延迟越大。

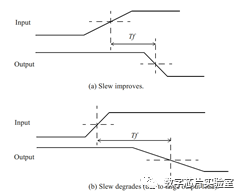

在大多数情况下,延迟随着输入transition time的增加而增加,但是延迟和输入transitiontime并不总是单调关系,尤其是在输出负载较小的情况下。

输出的transition time主要取决于输出电容,随输出负载而增加。因此,较大的输入transition time可以根据cell的类型及其输出负载不同得到改善。

早期的延时建模采用简单的线性延迟模型(linear delay model),其中延迟是input transition time和output load capacitance两者的线性函数,其一般形式如下所示:

D = D0 +D1 * S + D2 * C其中D0,D1,D2是常数,S是inputtransition time,C是output load capacitance。

线性延迟模型在亚微米工艺下不太准确,因此目前大多数lib库使用更复杂的模型,例如非线性延迟模型(non-lineardelay model)。

Non-LinearDelay Model

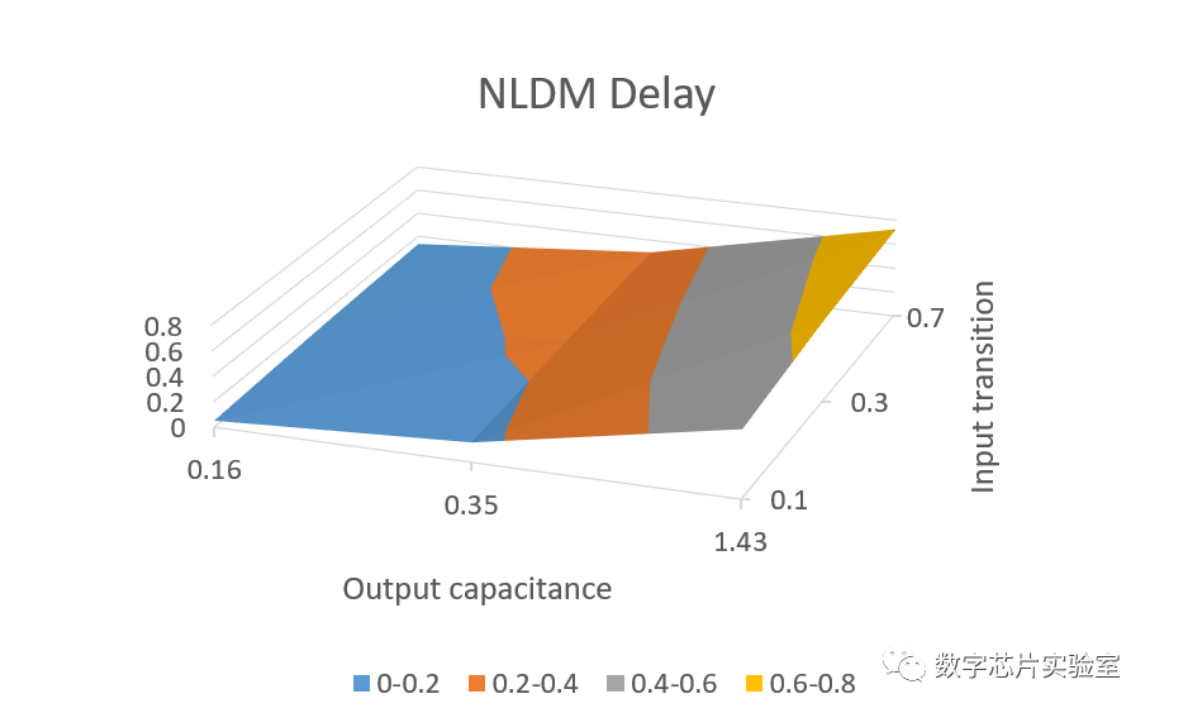

大多数lib库都包括查找表模型(table models),例如NLDM(非线性延迟模型),为cell的各种时序弧(timing arcs)指定延迟,output transition和其他时序检查等信息。

• Risedelay

• Fall delay

• Rise transition

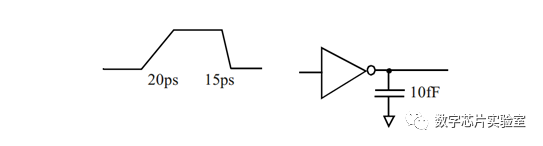

• Fall transitionNLDM根据input transition time和output capacitance获得cell的不同timing arcs的延迟。也就是说,NLDM模型是一个二维的查找表,其中两个输入变量是inputtransition time和output capacitance,表中的内容是该timing arcs的延迟。

lu_table_template(delay_template_3x3) {

variable_1 : input_net_transition;

variable_2 :total_output_net_capacitance;

index_1 ("1000, 1001,1002");

index_2 ("1000, 1001,1002");

}

/* The input transition and the output capacitance can be

in either order, that is, variable_1 can be the output

capacitance. However, these designations are usually

consistent across all templates in a library. */上面的查找表模板指定表中的第一个行索引变量是input transition time,第二个列索引变量是output capacitance。索引值(1000, 1001, 1002)只是模板,会被实际索引值覆盖。

下面是实际的NLDM

pin(OUT) {

max_transition : 1.0;

timing() {

related_pin : "INP1";

timing_sense : negative_unate;

cell_rise(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */ \

/* 0.1 */ "0.0513, 0.1537, 0.5280", \

/* 0.3 */ "0.1018, 0.2327, 0.6476", \

/* 0.7 */ "0.1334, 0.2973, 0.7252");

}

cell_fall(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */ \

/* 0.1 */ "0.0617, 0.1537, 0.5280", \

/* 0.3 */ "0.0918, 0.2027, 0.5676", \

/* 0.7 */ "0.1034, 0.2273, 0.6452");

}在上面的例子中,描述了输出引脚OUT分别在上升(cell\_rise)和下降(cell\_fall)的从引脚INP1到引脚OUT的延迟。还指定了输出引脚OUT的max\_transition。查找表模板已经在delay\_template\_3x3中描述。

表中的timing\_sense : negative\_unate表示输入的翻转和输出翻转是相反的关系,即

input rise -> output fall

input fall -> output rise根据延迟表,对于反相器的cell\_rise延迟,input transition(fall) time为0.3ns,output load为0.16pf 时,对应延迟为0.1018ns。

NLDM模型不仅用于延迟,而且还用于指定output transition time,该值也是以input transition time和output load为索引变量的查找表。

pin(OUT) {

max_transition : 1.0;

timing() {

related_pin : "INP";

timing_sense : negative_unate;

rise_transition(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */ \

/* 0.1 */ "0.0417, 0.1337, 0.4680", \

/* 0.3 */ "0.0718, 0.1827, 0.5676", \

/* 0.7 */ "0.1034, 0.2173, 0.6452");

}

fall_transition(delay_template_3x3) {

index_1 ("0.1, 0.3, 0.7");/* Input transition */

index_2 ("0.16, 0.35,1.43"); /* Output capacitance */

values ( /* 0.16 0.35 1.43 */ \

/* 0.1 */ "0.0817, 0.1937, 0.7280", \

/* 0.3 */ "0.1018, 0.2327, 0.7676", \

/* 0.7 */ "0.1334, 0.2973, 0.8452");

}. . .

}

. . .

}本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/d\_wcQw5o35QqK0o-\_p1A7Q

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。