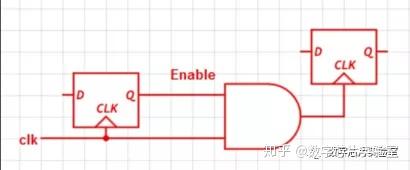

下面是门控时钟(clock gating)的最简单实现方法(使用与门):

从理论上讲,这是可行的:当使能信号Enable为高电平时,时钟将被传递到被门控的触发器FF2。

问题在于时序(timing)。在时钟的上升沿,触发器FF1的D输入传播到Q输出,但是时钟的同一上升沿也到达了与门,这会导致门控时钟出现毛刺现象。

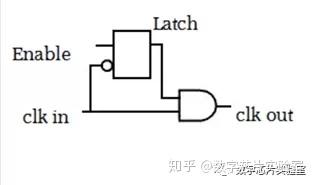

因此,我们使用集成时钟门控(ICG)单元,该单元包含一个低电平敏感的锁存器

当时钟为低电平时,允许输入直接传播到与门的输入。此时时钟为低电平,所以与门的输出将为低电平,与使能输入无关。

但是,当时钟为高电平时,锁存器将关闭,并阻止Enable值的任何更改传播到AND门。这就不会产生毛刺。

当时钟再次变为低电平时,锁存器重新打开,新的使能值通过锁存器。

可以使用单独的门(锁存器和与门)构建这种类型的电路,但这需要在综合/后端/STA中进行一些额外的时序检查。

大多数ASIC库都提供一个标准的ICG单元,其中的时序已经在内部进行了描述。类似于触发器和锁存器,ICG单元的使能输入同样具有建立和保持时间要求,很容易进行时序分析。

那么为什么使用Latch-based ICG 而不使用Flip-Flop-based ICG呢?

如果使用的是上升沿触发的触发器,就会发生和一开始的clock gating设计一样的问题

如果使用的是下降沿触发的触发器代替低电平敏感的锁存器,在时钟的下降沿捕获使能输入。这样与门的使能输入会保持稳定,直到时钟的下一个下降沿。因此,解决了毛刺问题。

但是,这会带来三个问题:

1、触发器通常由两个锁存器组成。因此,Flip-Flop-basedICG相比Latch-based ICG面积增加了一倍。

2、Flip-Flop-based ICG相比Latch-based ICG增加了功耗

3、最重要的是,Flip-Flop-based ICG在时钟下降沿捕获使能输入,必须在半个时钟周期内完成。而使用锁存器,能够占用整个时钟周期(time borrow),因为Latch在有效电平是一直能够传播数据的,触发器只能在边沿传播数据。

因此,Latch-based ICG相比Flip-Flop-based ICG具有更好的功耗、面积和时序。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/vsTjLv\_rCJZoMxWsuxfseA

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。