Synopsys Design Compiler是行业领先的设计综合工具。大多数的ASIC设计公司都使用Synopsys DC用于综合,使用Synopsys PT用于时序分析。

Introduction to Design Constraints

设计约束被分类为设计规则约束(design rule constraints)和优化约束(optimization constraints)。

设计综合流程:

1.读取设计对象:设计对象是仿真功能正确的Verilog RTL代码。 此步骤使用的命令是

1.analyze,elaborate/read2.指定工艺要求:在这些步骤中需要指定设计规则和库。此步骤中使用的命令是

1.Library Objects:link_library ,target_library,symbol_library

2.DesignRules : set_max_transition,set_max_fanout,set_max_capacitance3.设计环境定义:设计环境包括process,temperature, voltage条件,驱动强度和负载。 使用的命令是

1.set_operating_conditions set_wire_load set_drive set_driving_cell set_load set_fanout_load4.选择综合策略:top-down 和bottom-up。

5.设置设计约束:用于设计的优化和时序分析。 此步骤中使用的命令是

1.create_clock,set_clock_uncertainty set_clock_latency, set_input_delay,set_output_delay, set_max_area6.优化设计:综合设计以生成特定于工艺的门级网表。 使用的命令是

1.compile7.分析和debug设计:通过生成各种报告来debug设计中存在问题非常重要。使用的命令是

1.check_design

2.report_area

3.report_constraint

4.report_timingTiming Optimization and Performance Improvement

在优化期间,与power和area相比,timing具有最高优先级。

Design Compilation with ‘map\_effort high’

大多数时候,设计工程师使用map\_effort medium选项进行综合。建议在综合过程中第一阶段使用选项map\_effort medium,可以减少综合的run time。 如果设计不满足约束,那么设计人员可以使用map\_effort high选项进行增量综合。 这可以改善设计时序至少5-10%。sdc命令如下:

1.compile -map_effort high -incremental mappingLogical Flattening

设计层次可以展平,使设计的所有逻辑处于同一层级。这允许DC对模块边界进行优化,以获得更好的性能和更好的面积。

使用以下命令实现设计的逻辑展平

1.ungroup -flattern -allUse of group\_path Command

使用map\_effort high选项可以将设计性能提升到10%。但是如果在进行增量综合后还不能满足时序要求,必须对关键时序路径进行分组并增加关键路径的优化权重。

该命令如下所示:

1.group_path-name critical1 -from <input_name> -to <output_name> -weight <weight_factor>Submodule Characterizing

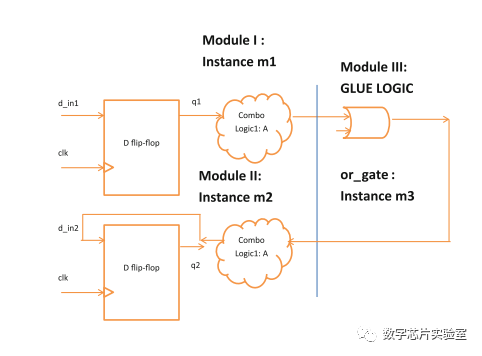

在实际的ASIC设计中,设计可以具有多个层次结构。TOP级设计由子模块X,Y,Z组成。如果这些子模块根据各自的约束单独综合优化,并满足了时序要求。当这些子模块在更高层次(TOP)中例化时,它们可能不会满足时序。其原因可能是模块之间存在胶合逻辑,也可能顶层约束太严格。

在这种情况下,为了满足设计约束,建议使用characterize命令。此命令可以基于TOP级层次结构环境获取子模块边界的环境。每子模块可以单独综合和characterize。

以下是可以实现characterize的脚本。将子模块X,Y,Z的实例名称分别为

I1,I2和I3。

1.

2.current_design

3.TOPcharacterize I1

4.compile -map_effort high -incremental mapping

5.current_design TOP

6.characterize I2

7.compile -map_effort high -incremental mapping

8.current_design TOP

9.characterize I3

10.compile -map_effort high -incremental mappingRegister Balancing

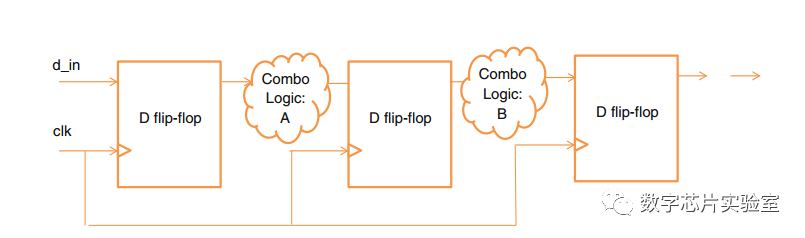

Register balancing是将组合逻辑从一个流水线级移动到另一个流水线级来提高设计性能。考虑下图的流水线设计

假设相比第一个流水线阶段,第二个流水线阶段具有更大的延迟。设计的性能被最大的延迟限制了。

在这种情况下,Register balancing可用于将组合逻辑从一个流水线级移到另一个流水线级,而不影响设计的功能。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/a2BXfKfXXfabDx5-mm1Kyw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。