即便是功能仿真相同的RTL代码,不同的代码风格也会得出不同的综合结果。我们不能仅仅依赖于综合工具来fix代码风格糟糕的设计!

了解综合工具如何综合RTL对于前端工程师至关重要。

1

下面针对Design Compiler逻辑综合工具谈谈代码风格:

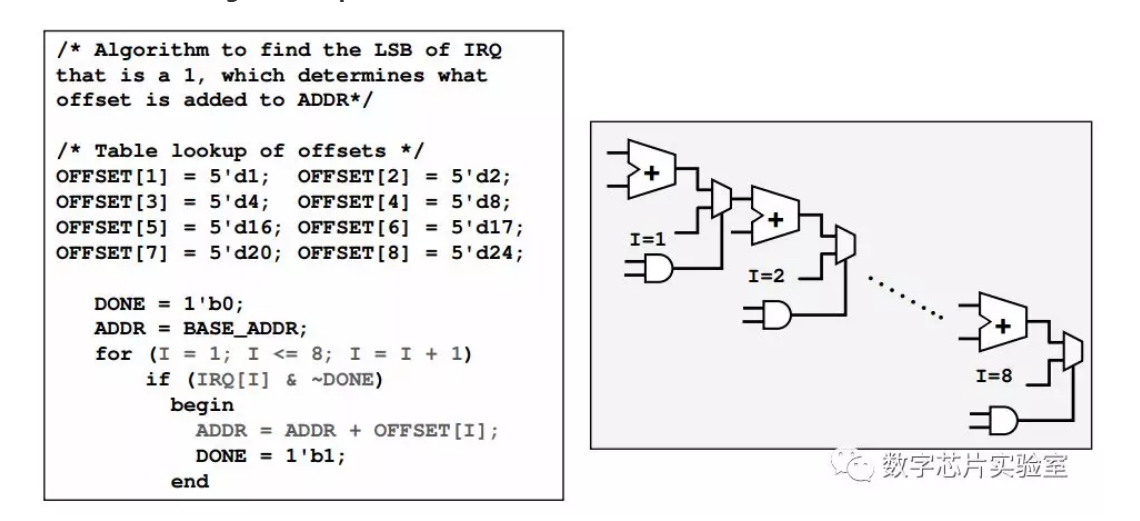

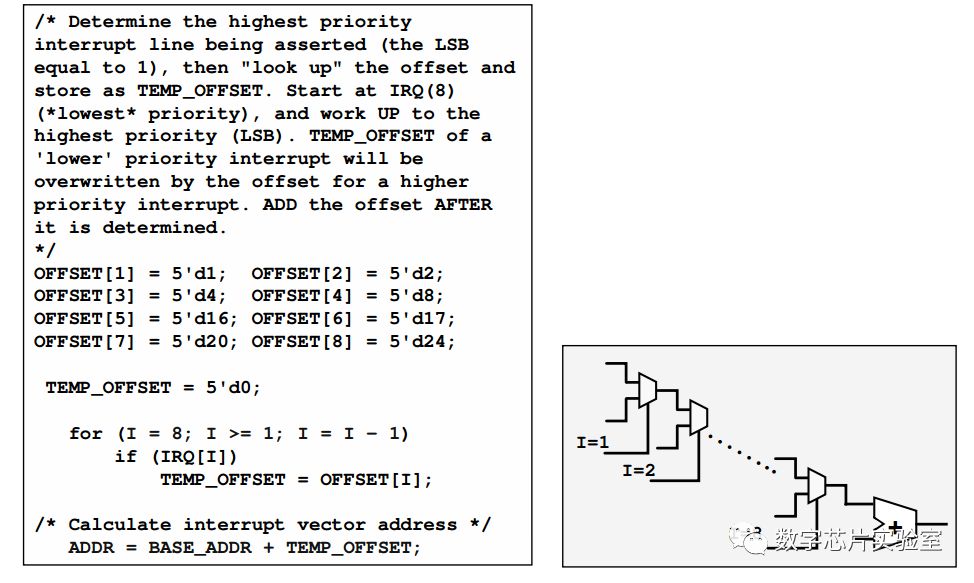

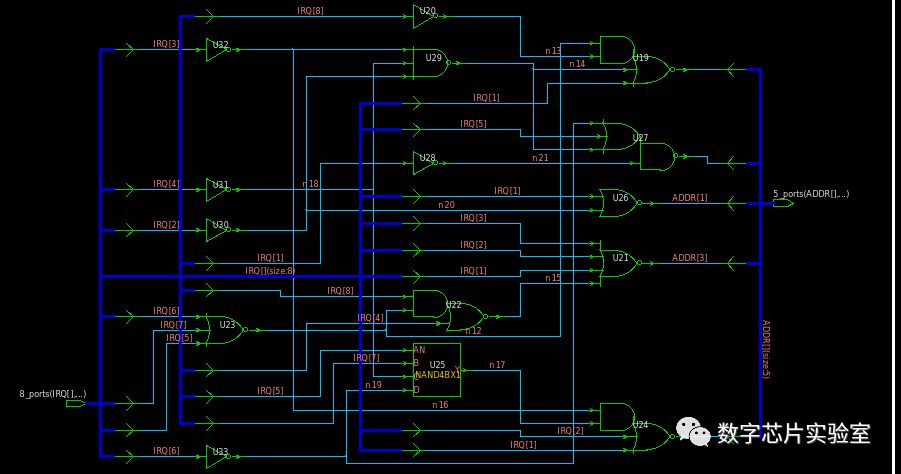

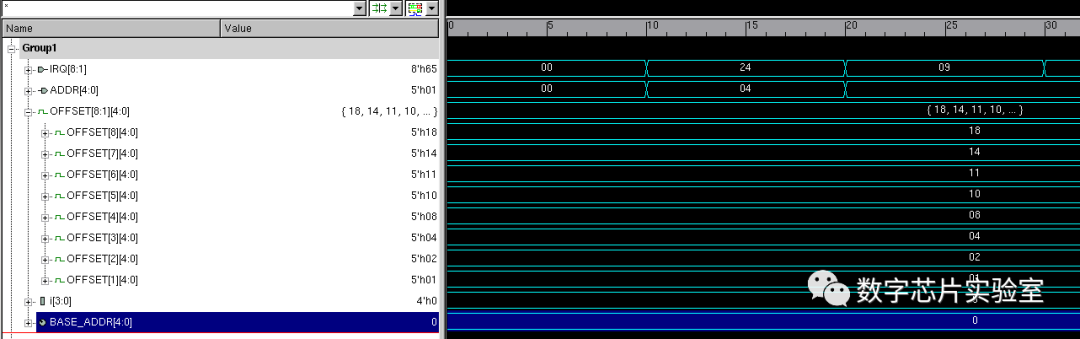

在上面的算法中,在for循环中执行“ADDR = ADDR+ OFFSET[I]”,因此是加法器逻辑重复8次! 此外,由于for循环以IRQ的LSB开始,需要标志附加逻辑。由于IRQ输入事2不知道,所以必须使用8个加法器构建的硬件才能处理任何情况的输入。

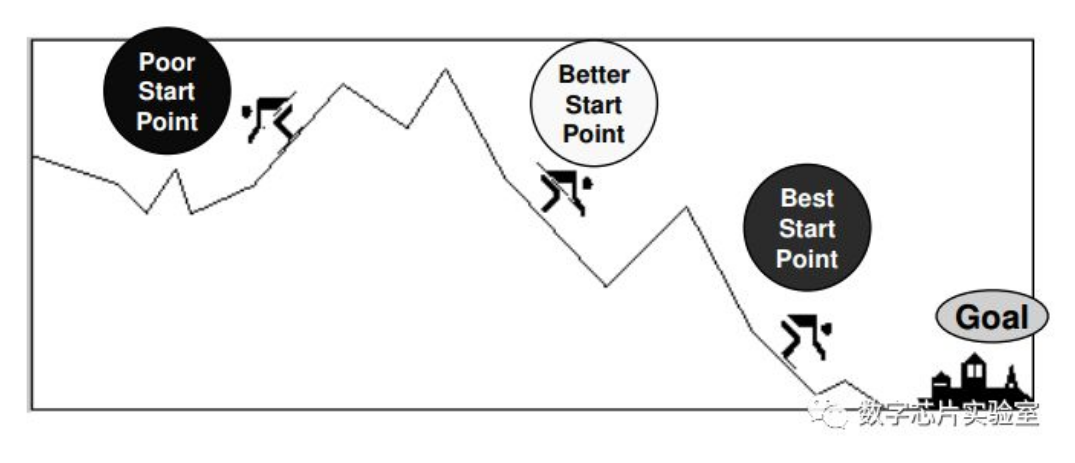

Design Compiler只能使加法器尽可能快,但关键路径仍然包含8个加法器。

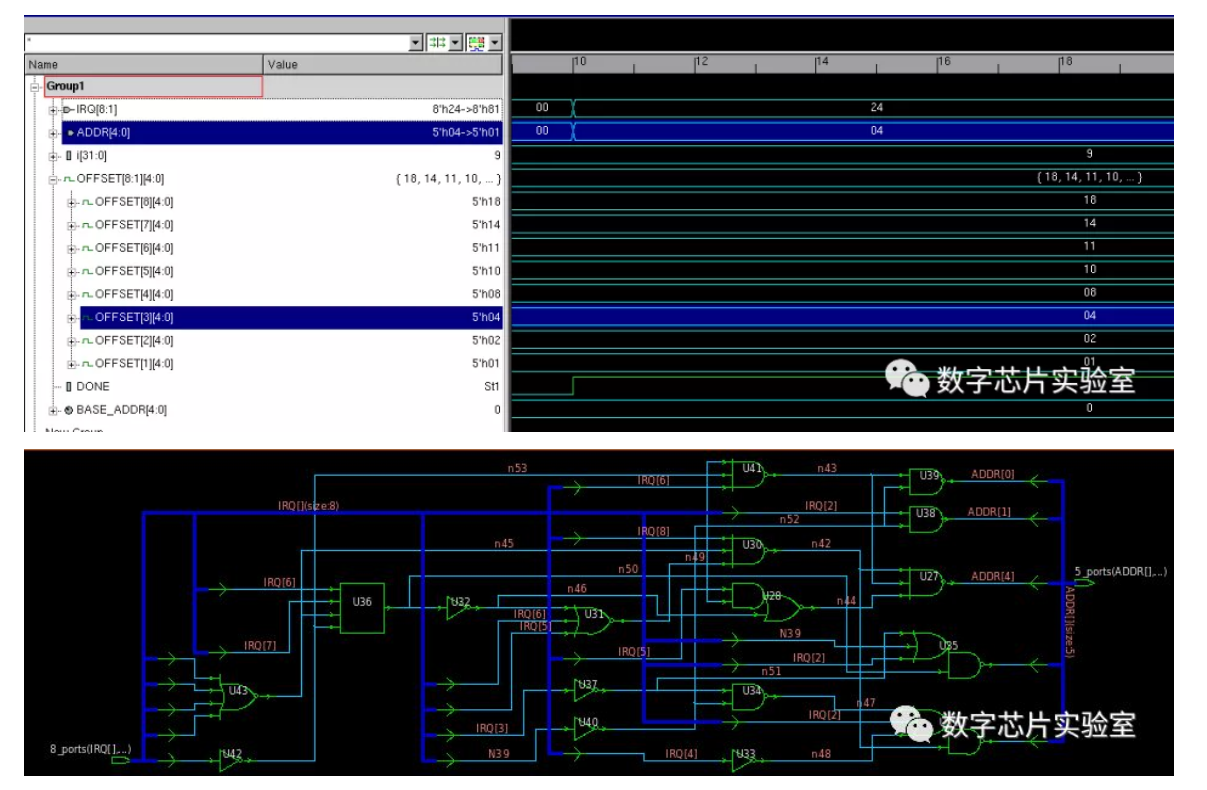

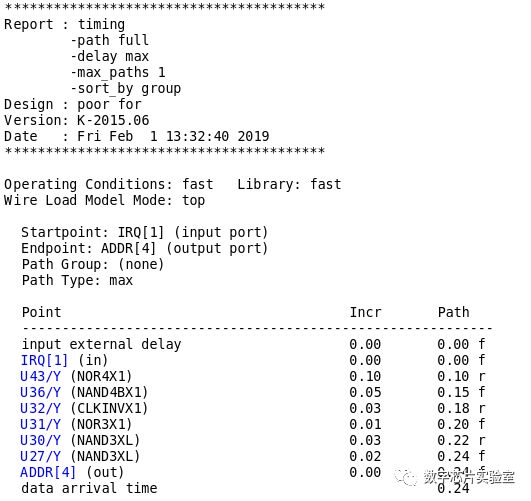

下面是部分verilog代码和仿真综合结果。可见,从input到output路径,延时0.24ns,面积消耗55.74um2。

2

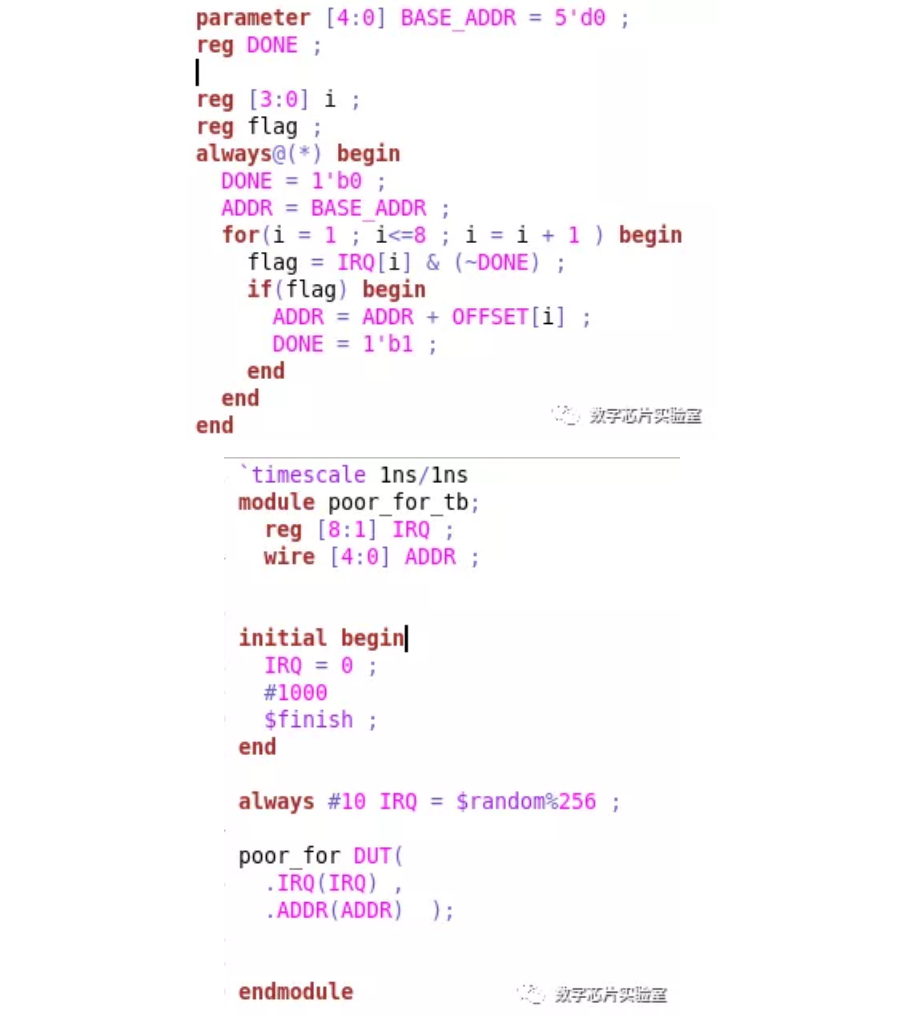

我们对算法进行优化:

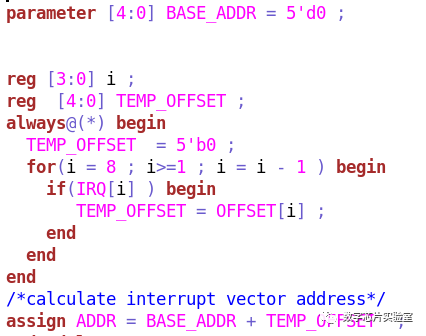

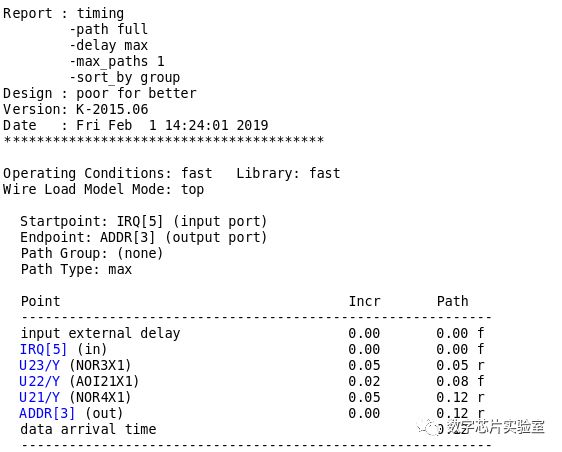

在for循环之外执行“ADDR = BASE\_ADDR + TEMP\_OFFSET ”可以节省7个加法器的面积和延迟! 从MSB而不是LSB开始循环,利用了IF语句的优先级特性,进一步消除DONE标志相关的附加逻辑。

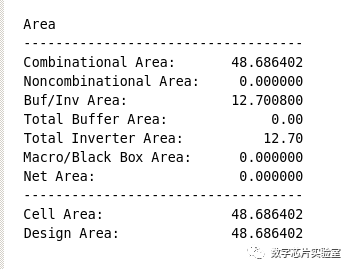

下面是部分verilog代码,仿真综合结果。可见,从input到output路径延时0.12ns,面积消耗48.68um2。

也就是说,假设这个模块的输入和输出都被寄存器锁存。性能会提高100%,硬件开销降低12.68%

3

伴随着数字芯片设计工具逐渐智能化和自动化的趋势,作为一个IC Designer,又该如何适应技术发展,而不被工具代替?

1、 硬件算法优化。类比于软件算法时间和空间复杂度,在硬件算法建模时考虑硬件PPA(performance、power、area)

2、 verilog代码风格。在编码的时候,清楚自己的代码会大致清楚综合后的电路。否则“Garbage in, garbage out”

3、 EDA工具。工具只是工具,不是 “./run”就能设计一款高性能低功耗低开销的SOC芯片。要选择合适的工具流程和参数设置。

4、 解决问题。要想让自己的工作有价值,一切跑脚本,抄代码的行为对于提高技术水平都没有意义,我们需要的是分析工具report出来的问题,然后解决它。

最后,祝愿大家都不会被 不刷知乎抖音,不玩农药吃鸡,高效率低成本的智能化EDA工具替代!

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/pvd-IWnWj3fhSXtKMKSIVw

未经作者同意,请勿转载!

推荐阅读

- 为什么ICG Cell中使用锁存器(Latch),而不使用触发器(Flip Flop)?

- Cell延时从哪里来?非线性延时模型(NLDM)把一切都告诉你

- 基于QuestaSIM的SystemVerilog DPI使用流程(step by step)

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。