上篇文章谈到EDA工具在做时钟树综合的时候,在设计者正确定义create\_clock、create\_generated\_clock,正确插入ICG cell的条件下能够自动识别出设计对时钟树的需求,即定义Implicit stop/nonstop/exclude pin。

事实上,EDA工具只是帮助完成了时钟树定义中非常简单的工作。

决定时钟树质量非常重要的工作还有user define的Clock Tree Exceptions,即需要人为显式定义的explicit stop/nonstop/exclude/float pin。

我们知道数字后端Flow中存在大量需要人为定义的exception(timing exception、clock tree exception、、、)。这种exception存在两种原因:

1、EDA工具或者Flow不完善,需要人为定义的exception太多,需要向更加智能化改进。最好是

1.一键执行define clock tree,

2.等待一杯咖啡的时间

3.“ding”提示时钟树clock tree define succeed

4.点击“OK”

2、提供用户接口,定制化设计需求

好了,进入正题Specifying Clock Tree Exceptions

可以使用set\_clock\_tree\_exceptions命令设置Clock Tree Exceptions。

在不指定-clocks选项的情况下,应用于当前scenario所有clock。

1.icc_shell> set_clock_tree_exceptions -stop_pins \

2.clocks CLK1 [get_pins pins_on_the_clock_path]该设置可以通过remove\_clock\_tree\_exceptions命令删除。上述exceptions主要包括

Nonstop pins

Exclude pins

Float pins

Stop pins

Specifying Nonstop Pins

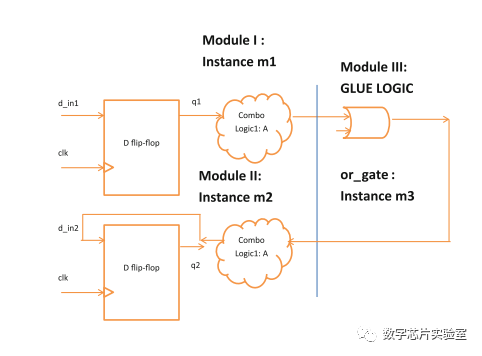

工具可以通过Nonstop Pins trace到时钟树的端点。例如之前可以隐式定义的generated clock和ICG cell

Specifying Exclude Pins

Exclude Pins是时钟树时序优化中排除的时钟树端点,只进行DRC优化。

1 icc_shell> set_clock_tree_exceptions -exclude_pins [get_pins U2/A]

2Specifying Float Pins

Float Pins 具有特殊insertion delay要求的时钟引脚。设置Float Pins 时,工具在优化时钟树时会考虑这个延迟。

Float Pins的一个应用场景就是设计中存在没有时序库的hard mocro,但是该hard macro的clock pin对时序有要求。这是就可以使用Float Pins指定hard macro内部的insertion delay。

Specifying Stop Pins

Stop Pins是时钟树的端点,在进行时钟树综合时需要进行skew、insertion delay和DRC的优化。在有需要的时候,同样可以显式指定StopPins。

本文转载自公众号:芯片数字实验室

原文链接:https://mp.weixin.qq.com/s/5iFxRiB\_PUKiIag\_2S79Kw

未经作者同意,请勿转载!

推荐阅读

想了解更多内容,欢迎关注芯片数字实验室专栏,由于工具,你可以专注在更重要的事情上。