PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

Version 4.3

©2007 - 2014 Intel Corporation—All rights reserved.

7.20 Link Equalization Evaluation

处于 P0 状态时,PHY 能够被 MAC 指示开始评估链路伙伴的当前发送均衡设置。

均衡设置评估中的基本流程是 MAC 通过置高 RxEqEval 信号,要求 PHY 开始均衡设置评估。在 PHY 完成一次均衡设置评估后,置高 PhyStatus 一个周期,并将 LinkEvaluationFeedback 信号的值更新评估反馈结果。

在一次均衡设置评估结束,即 PHY 置高 PhyStatus 一个周期后,MAC 需要首先置低 RxEqEval ,才能开始下一次均衡设置评估。

一旦 MAC 发出均衡设置评估的请求后(通过置高 RxEqEval 信号),MAC 必须保持 RxEqEval 信号为高,直到 PHY 完成本次均衡设置评估,置高 PhyStatus 信号为止,除非 MAC 因为超时或者其他一些错误情况,需要终止此次评估。

如果 MAC 需要提前终止评估,那么 MAC 可以在 PHY 完成评估前,就置低 RxEqEval 信号。在 MAC 提前终止评估之后,PHY 需要立刻响应,MAC 会因为提前终止而忽视此次评估的结果。

注意:有一种意外的情况,MAC 在置低 RxEqEval 信号,提前终止评估时,在同一个时钟边沿,PHY 完成评估并置起 PhyStatus 信号,那么这种情况下,PHY 不需要进一步的操作。

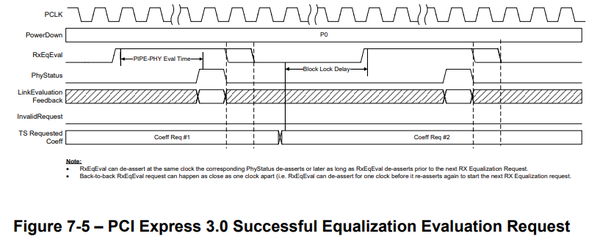

图 7-5 一次成功的链路均衡评估请求时序图

注意:

- RxEqEval 可以和 PhyStatus 同时置低,也可以在其后置低,只要满足在下一次均衡开始前置低即可

- 支持背靠背的 RxEqEval 请求,可以置低 RxEqEval ,并在一个时钟之后置高,开始下一次均衡评估

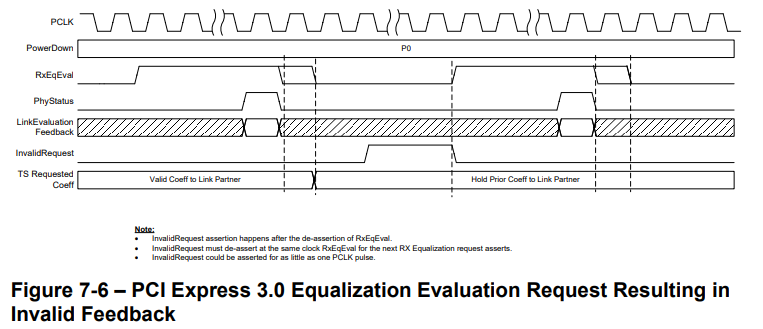

图 7-6 一次结果为 invalid requeset 的链路均衡评估请求时序图

注意:

- InvalidRequest 信号在 RxEqEval 信号置低后才会置高

- InvalidRequest 信号需要在下一次均衡的 RxEqEval 置起的时钟周期置低

- InvalidRequest 信号可以只持续一个周期

7.21 Implementation specific timing and selectable parameter support

翻译暂略

7.22 Control Signal Decode table – PCI Express Mode

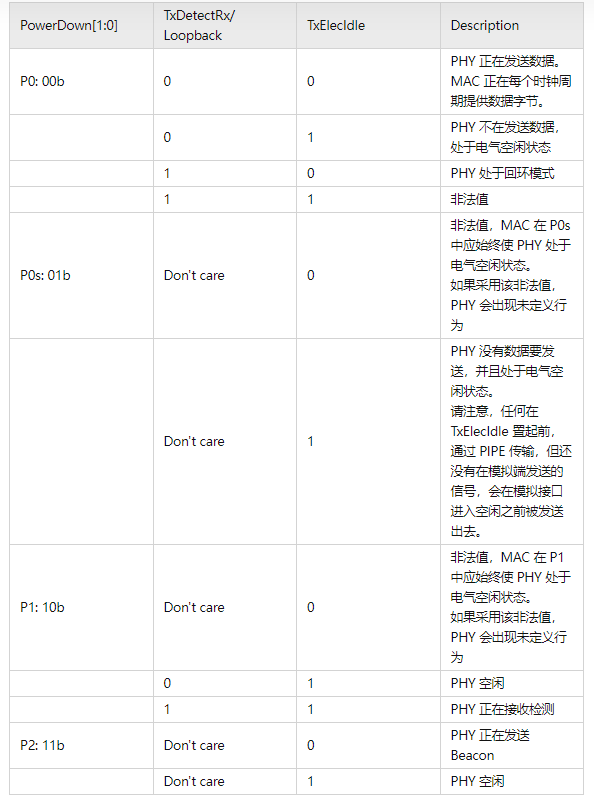

下述表格总结了 7 项控制信号中的 4 项,在各个电源模式下不同的行为。(译注:表中似乎只有 3 项控制信号)

至于另外三项控制信号

Reset# 信号会改写一切 PHY 行为,进入复位状态。

TxCompliance ,RxPolarity 只会在 PHY 处于 P0 模式,正常流量传输时,会被用到,且只会单独使用,所以没有列在表格中。

注意:上述规则只适用于 Lane 没有被关闭("turned of")的情况,见第 9 节(Multi-lane PIPE)所述。

7.23 Control Signal Decode table – USB Mode

翻译暂略

7.24 Control Signal Decode table – SATA Mode

翻译暂略

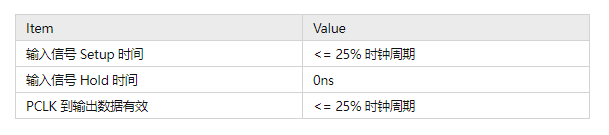

7.25 Required synchronous signal timings

为了提高不同厂商 MAC 和 PHY 之间的互操作性,同步 PIPE 总线时序需要满足下表的要求:

7.26 128b/130b Encoding and Block Synchronization (PCI Express 8 GT/s)

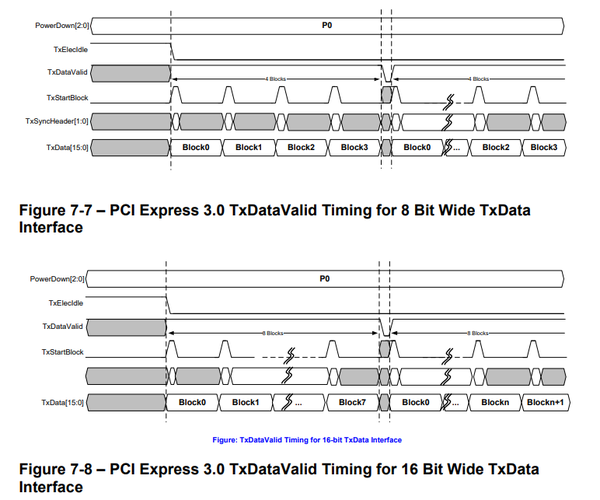

对于每个数据块,(通常来说是 128 比特,但有时候 Retimer 会发送一些稍短或者稍长的 SKP 块),以 8 GT/s 的速率从 PIPE 接口传输给 PHY,而 PHY 经过编码后还需要发送两个新增的比特。

因为 PHY 发送的 130 比特与 PIPE 数据传输位宽不匹配,所以 MAC 需要通过 TxDataValid 来周期性地停止数据传输,以留出一个时钟周期给 PHY 发送其为组帧而额外产生的比特。

举例而言,如果 TxData 位宽为 16 比特,PCLK 频率为 500MHz,那么每传输 8 个块数据之后,MAC 需要置低 TxDataValid 信号一个周期,使 PHY 能够传输额外的 16 比特。

PHY 使用缓存空间来暂存发送数据,以克服 128/130b 编码方式导致的速率不匹配问题。PHY 的缓存必须在 PHY 从复位状态释放后清空,并且必须在 PHY 退出电气空闲状态时为空(所以在重新进入空闲状态时,缓存会被冲刷清空)。同样地,在接收方向 PHY 也需要以同样的方式控制 RxDataValid。

TxDataValid 和 RxDataValid 必须周期性地置低,每 N 个周期置低一个时钟周期。速率 8 GT/s 时,位宽 8 比特时,N 为 4;位宽 16 比特时,N 为 8;位宽 32 比特时,N 为 16;

在退出复位状态,或者电气状态后,MAC 必须在第 N 个数据宽传输结束后立刻首次置低 TxDataValid 信号。

图 7-7 描述了 8 比特位宽时 TxDataValid 信号时序图。图 7-8 描述了 16 比特位宽的情况

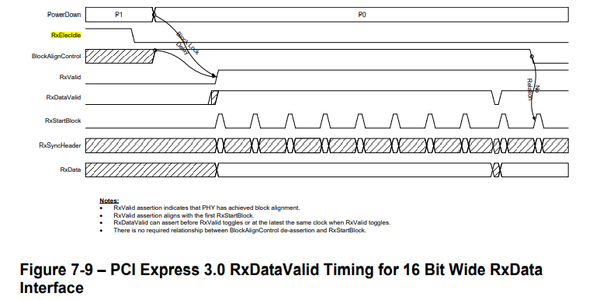

在接收端,从 PHY 复位或者从电气空闲状态退出始,PHY 在接收并通过 PIPE 接口传输给 MAC N 个数据块后,必须立刻第一次置起 RxDataValid 信号。

图 7-9 描述了 16 比特总线 RxDataValid 和其他接收信号时序图

图 7-9 16 比特总线 RxDataValid 时序图

在一些场景中,比如 upconfigure 中,当 MAC 开始准备在一条空闲的通道上开始传输数据的时候,此时其他通道处于活动状态。MAC 必须等到 TxDataValid 置低再于空闲的通道上开始新的数据传输,因为要等待 PHY 将剩余的 128b/130b 在当前活跃的通道上发送完毕。

7.27 128b/132b Encoding and Block Synchronization (USB 10 GT/s)

翻译暂略

原文: Mindshare

译者: Michael ZZY

校对: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/511752677

《PCI Express Technology 3.0》翻译系列

- PHY Interface 协议翻译:7.6 - 7.12

- PHY Interface :7 PIPE Operational Behavior 7.1-7.5

- PHY Interface :3 PHY/MAC interface & 4

- PHY Interface 协议翻译: 2 Introduction

- PCI Express Technology 3.0 Chapter 6 流量控制 5-7 节

- PCI Express Technology 3.0:Chapter 6 流量控制 1-4 节

- 《PCI Express Technology 3.0 》Chapter 5 第3 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

- PCI Express Technology 3.0:PCIe体系结构概述 2.1 节

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。