我们在前文中多次提及一些和链路初始化和训练相关的配置寄存器(Configuration Register),在这一节我们将对它们做一番总结。

14.16.1 Link Capabilities Register // 链路能力寄存器

链路能力寄存器各比特含义如原文 639 页图 14-68 所示,本节详细描述了和链路初始化和训练相关比特的含义。

图 14-68 链路能力寄存器各比特含义示意图

Max Link Speed [3:0]

此处描述的是链路的最高速率,其值是一个指向链路能力 2 (Link Capabilities 2)寄存器的链路支持速率向量(Supported Link Speeds Vector)域的指针。指针指向的比特所代表的速率为链路最高速率,具体定义如下: • 0001b ‐ Supported Link Speeds Vector field bit 0 • 0010b ‐ Supported Link Speeds Vector field bit 1 • 0011b ‐ Supported Link Speeds Vector field bit 2 • 0100b ‐ Supported Link Speeds Vector field bit 3 • 0101b ‐ Supported Link Speeds Vector field bit 4 • 0110b ‐ Supported Link Speeds Vector field bit 5 • 0111b ‐ Supported Link Speeds Vector field bit 6

除此以外所有的值为 reserved,无含义。同一个 USP 中的多个 function 必须使用同一个数值。该寄存器是一个只读寄存器。

Maximum Link Width[9:4]

此处描述的是 PCIe 链路的最大宽度,具体定义如下:

• 00 0000b: Reserved • 00 0001b: x1 • 00 0010b: x2 • 00 0100b: x4 • 00 1000b: x8 • 00 1100b: x12 • 01 0000b: x16 • 10 0000b: x32

除此以外所有的值为 reserved,无含义。同一个 USP 中的多个 function 必须使用同一个数值。该寄存器是一个只读寄存器。

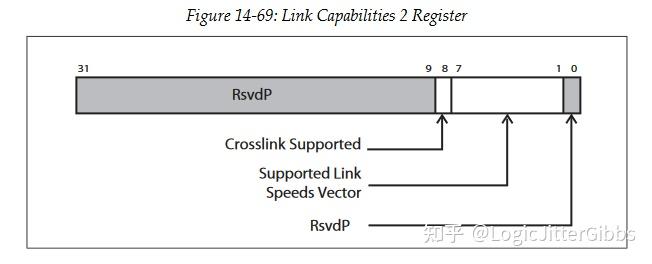

14.16.2 Link Capabilities 2 Register // 链路能力 2 寄存器

在上一幅图片图 14-68 的链路寄存器中的最高链路速率域,是一个指向本寄存器链路支持速率向量域的指针,该域在寄存器的位置如图 14-69 所示,具体定义如下:

• Bit 0 = 2.5 GT/s • Bit 1 = 5.0 GT/s • Bit 2 = 8.0 GT/s • Bits 6:3 RsvdP (reserved 并 preserved)

图 14-69 链路能力 2 寄存器

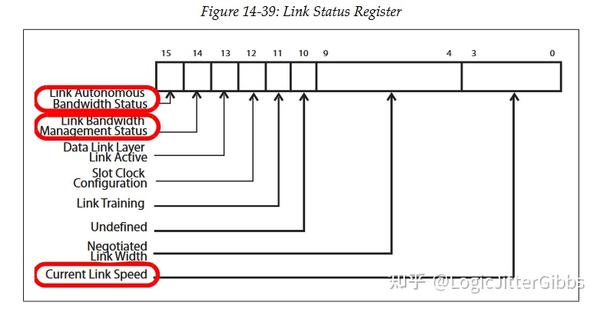

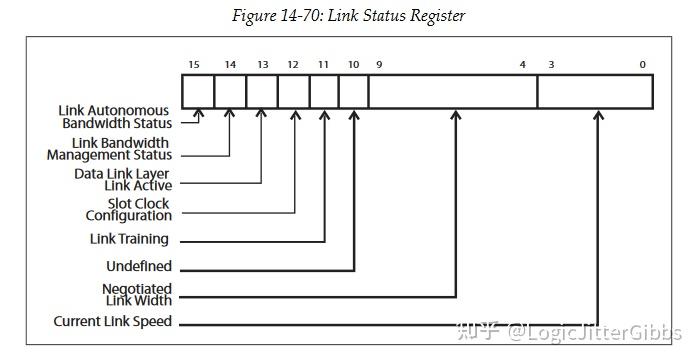

14.16.3 Link Status Register // 链路状态寄存器

链路状态寄存器如原文 597 页的图 14-39 所示:

图 14-39 链路状态寄存器

Current Link Speed[3:0]

该只读寄存器表示当前的链路速度。在链路首次进入 L0 状态时,链路速度始终为 2.5GT/s。在此之后,如果链路双方共同支持更高的速率,则链路通过进入 Recovery 状态,尝试改变到更高的速度。该寄存器域的编码方式和最大链路速度域相同,为一个指向链路支持速率向量域的指针:

• 0001b ‐ Supported Link Speeds Vector field bit 0 • 0010b ‐ Supported Link Speeds Vector field bit 1 • 0011b ‐ Supported Link Speeds Vector field bit 2 • 0100b ‐ Supported Link Speeds Vector field bit 3 • 0101b ‐ Supported Link Speeds Vector field bit 4 • 0110b ‐ Supported Link Speeds Vector field bit 5 • 0111b ‐ Supported Link Speeds Vector field bit 6

除此以外所有的值为 reserved,无含义。

注意:如果链路还没有 link up,则该域为未定义状态(LinkUp = 0b)。

Negotiated Link Width[9:4]

该寄存器表示的是链路宽度协商的结果。有七种可能的宽度,其他为无含义值。具体含义如下:

• 00 0001b: for x1. • 00 0010b for x2. • 00 0100b for x4. • 00 1000b for x8. • 00 1100b for x12. • 01 0000b for x16. • 10 0000b for x32.

除此以外所有的值为 reserved,无含义。

注意:如果链路还没有 link up,则该域为未定义状态(LinkUp = 0b)。

Undefined[10]

目前的协议版本中,该域无定义。在早前的协议版本中,如果链路训练发生错误,那么硬件会将该位写 1,并在 LTSSM 进入 L0 状态后清除。目前协议规定软件可以向该寄存器域中写入任何值,但必须忽略从该寄存器中读取的任何值。

Link Training[11]

该只读寄存器为 1 时表示 LTSSM 正处于训练过程中。技术上来讲,该比特为 1 时,表示 LTSSM 正处于 Configuration 或者 Recovery 状态中,或者此时链路重训练(Retrain Link)比特被写 1,但实际的链路训练还没开始。该比特在 LTSSM 退出 Configuration 或者 Recovery 状态后被清除。因为 LTSSM 处于训练过程中必须对软件可见,所以该比特只对 DSP 有意义,所以在 EP,桥设备和交换机的 USP 中没有作用,该比特必须硬连线固定为 0b。

图 14-70 链路状态寄存器

14.16.4 Link Control Register // 链路控制寄存器

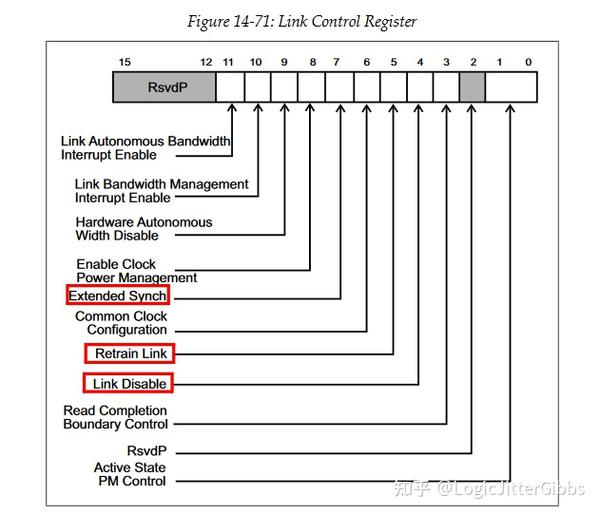

链路状态寄存器各域如原文 644 页图 14-71 所示,其中有三个我们感兴趣的寄存器域。

Link Disable

该比特被设置为 1 时,链路被置为未使能(Disable)状态。直观上来说,该比特不可被 EP,桥设备和交换机的 USP 使用,因为即使在链路未使能状态下,该比特也必须能被软件访问。无论在何种链路状态下,写该寄存器后,立刻进行的读操作都会读出写入的值。 在清除该比特后,软件必须小心地处理传统方式复位后,第一个 Configuration 读请求在时序上的要求。

Retrain Link

该比特可被软件用于在任何软件认为有必要地时候,发起链路重训练请求,比如想要恢复错误时。该比特不可被 EP,桥设备和交换机的 USP 使用。当该比特被设置为 1 时,其会将 LTSSM 强制设为 Recovery 状态,不会等待 Configuration 写请求的 completion 包返回(如有)。

Extended Synch

该比特和训练有关是因为该比特用于大幅增加两个 LTSSM 状态下的用时,用于帮助较慢的外部测试或者分析设备,在正常通信恢复时,能够与设备建立同步。其中一个场景是在退出 L0s 时,此时置起该比特会在退出 L0s 时,强制发送 4096 个 FTS。另一个场景是在 Recovery 状态中,在进入 Recovery.RcvrCfg 之前,置起该比特会强制发送 1024 个 TS1 序列。

图 14-71 链路控制寄存器

原文: Mindshare

译者: LJGibbs

校对:

欢迎参与 《Mindshare PCI Express Technology 3.0 一书的中文翻译计划》

Gitee:

https://gitee.com/ljgibbs/chinese-translation-of-pci-express-technology

Github:

https://github.com/ljgibbslf/Chinese-Translation-of-PCI-Express-Technology-

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- PCI Express Technology 3.0 链路初始化与训练 节15 动态带宽改变

- 【译文】 On-chip Clock Controller // 片上时钟控制器

- 【译文】PCI Express Technology 3.0 Chapter 8 事务排序

- 【译文】 DFT, Scan and ATPG

- 【译文】 Example showing JTAG Operation // JTAG 运行示例

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。