目录

本期我们基于DDR 测试方案提供商:Teledyne Lecroy 关于 DDR 调试与兼容性验证的系列讲座来学习 DDR 测试与调试相关的知识。

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

DDR 学习时间 - OpenIC SIG 开源数字IC技术分享

关于讲座

本系列基于 TL 提供的:《如何成为 DDR 物理层测试大师》系列讲座,讨论有关 DDR 调试、兼容性验证和测试等相关内容。本系列文章基于 TL 的 PPT做了一些翻译,并增加了一些笔者自己的见解。

本文所使用的文字和图片版权归 TL 所有,如有侵权,十分抱歉,还请联系我删减.

使用公司邮箱登记后既可观看视频和下载 PPT。

讲座分为四讲,分别是:

Part One: Fundamentals of DDR Memory Physical Layer Testing

Part Two: Beyond DDR Compliance Testing — Using Advanced Debug Tools

Part Three: Top Tips and Techniques for Better DDR Probing and Testing

Part Four: DDR Debug Scenarios and Virtual Probing

书接上文,本期的内容是第一讲的下半部分,包括:

- 一些测量的准备工作

- DDR 兼容性测试

- 以及一个实际 DDR 信号质量分析 debug 的例子

DDR 物理层测试准备知识

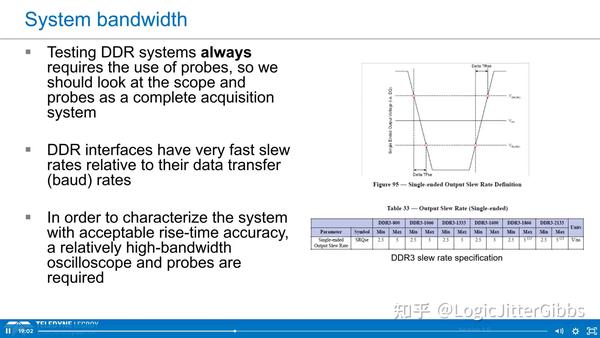

DRAM 物理层测试系统中,探头(Probe)和示波器(oscilloscope)是重要的一部分。

需要根据 DDR 信号的特点,在测量前制定测量系统的带宽指标。

- 由于 DDR 接口的速率很高,因此 DDR 信号的摇摆率(Slew rate)非常高

- 这样一来,想要完整地测量 DDR 系统,获得较高的信号变化捕捉精度,需要带宽比较大的示波器和探头

- 右图的 DDR3 摇摆率图表中可以看到,DDR3 的最大摇摆率可以达到 5V/ns

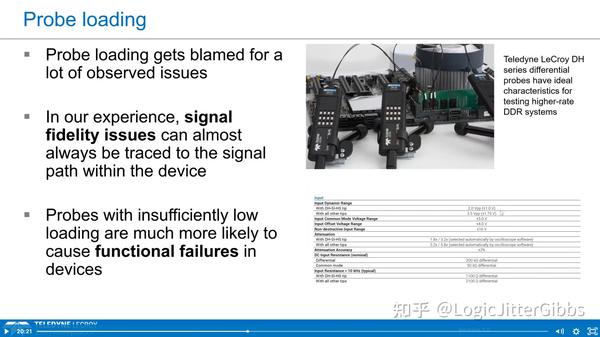

测量探头的负载不够轻是造成很多测量问题的原因

在实验中发现,大量的信号质量问题是在系统的信号测量通路中产生的,这其中包括但也不仅仅是探头。

不过,探头的负载不够轻很可能会在测量中导致功能性的失败——系统没有办法正常工作。

从右图中可以看到,他们家的探头输入阻抗在差分模式下可以得到 200K 欧姆,用于保证测量时能够通过探头得到良好的信号质量。

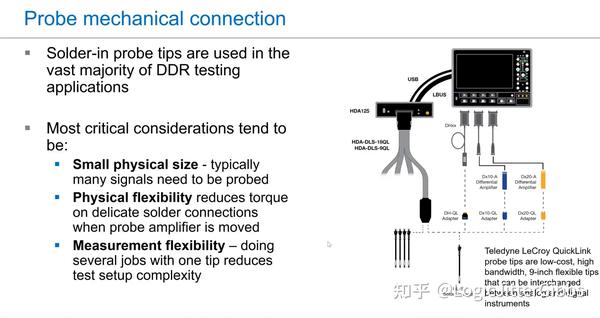

探头的机械连接在实际的 DDR 测量中也是一个重要的关注点。

在大部分的测试应用中,一般采用焊接式的探头,将探头的前端金属部分焊接到测量点上。

探头的机械连接一般有以下几点考量:

- 体积小巧,可以把探头焊接到布局紧密的器件之间

- 物理连接灵活,通过分离探头上的放大器,探头的物理连接变得更加灵活

- (编者觉得:放大器和探头分离之后,探头前端的体积变小,在焊接时对于测量点的压力、扭矩就更小了)

- 测量灵活,可以方便地统一测量数字或者模拟信号

T 家的探头从右边的图可以看出来,放大器分离的设计,让探头前端更小更灵活,同时可以兼具测量模拟或者数字信号的能力。

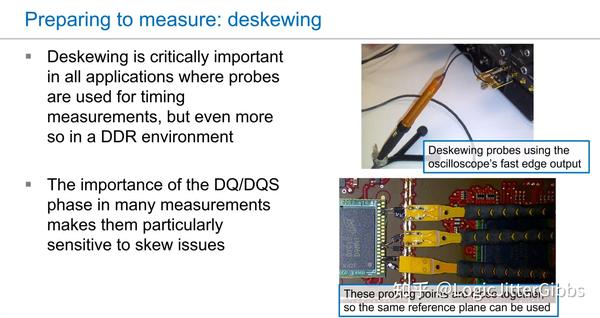

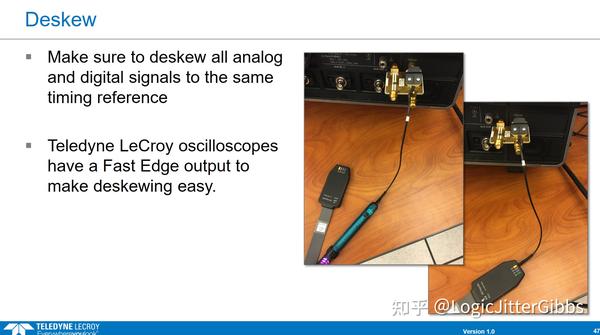

去除探头的抖动(Deskewing)对于所有时序测量的应用来说都是很重要的,对于 DDR 的测量更是如此。

因为 DDR 的 DQ/DQS 信号之间的相位关系十分精密,比如:

- 写操作中,DQS 的边沿对齐 DQ 的 1/2 周期处,以 DDR4-3200 为例,1/2 周期只有约 300ps

- 读操作中,DQS 的边沿与 DQ 的边沿对齐

按照协议,DQS 和 DQ 的相位误差在 100-200ps 级别,因此 DDR 测量中,探头需要将抖动降低到 100ps这个级别。

并且在 DDR 测量中,我们通常会使用多个探头连接 DQ 或者 DQS 信号,这些探头需要一起进行校正,以共享同一个参照水平。

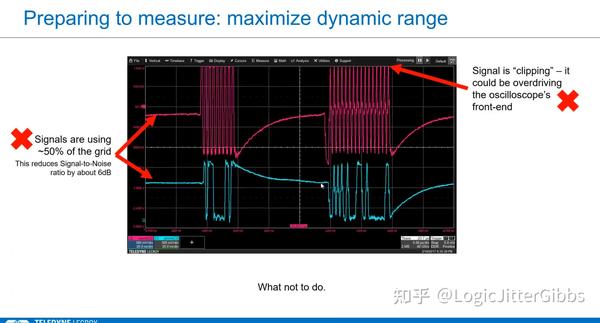

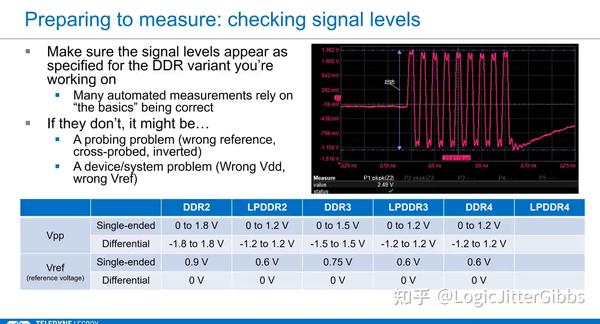

在测量中,需要根据不同 DDR 标准中的 VDD 电平设置合适的信号电压幅值范围,防止信号如上图中那样被削尖。

同时,也不能将信号的幅度范围调节的太小,如图中那样,信号幅度只占据了大约 50% 的动态范围,这样会减少信号的信噪比。

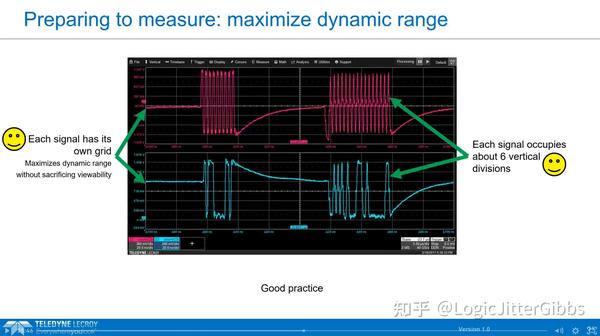

而这张 PPT 则给出了一个合适的信号动态范围的例子。在信号范围的调节中,我们还是需要以各代 DDR 标准的电平值做为参照。

掌握几个常用协议的工作电压是一个测量中的小常识。

目前比较常用的几个标准是 PCDDR3/4,PCDDR3L,LPDDR3/4,其中 DDR3 的工作电压是 1.5V,DDR4 是 1.2V,介于他们之间的是 DDR3L,电压是 1.35V。

DDR 兼容性测试

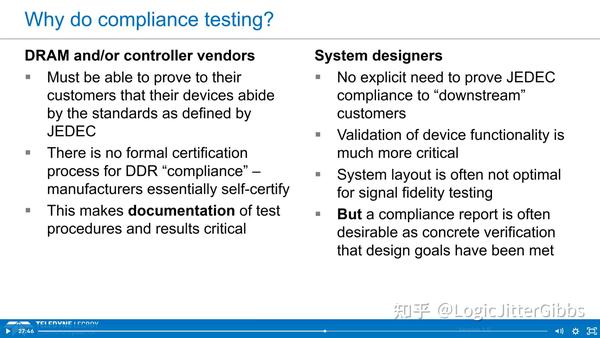

首先是我们为什么进行兼容性测试?

作者谈到了几点原因,对于 DRAM 以及 DRAM 控制器的厂商来说:

- 首先,他们要保证他们的产品符合 JEDEC 标准(因为下游客户会使用不同的颗粒,这些颗粒之间会有所不同,但他们会保证自己符合 JEDEC 标准)

- 第二,由于并没有一个第三方的 DRAM 兼容测试标准,所以厂商自身要尽可能地做更多兼容性测试,和扩大兼容性测试范围,以覆盖客户处可能出现的兼容性问题。

- 第三,需要记录测试过程,留下测试文档和记录测试数据

对于系统设计者来说:

- 他们更下游的客户是终端消费者,他们不太关心产品是否符合 JEDEC 标准,他们关心的是产品的功能

- 但产品的 PCB 设计需要 DRAM 兼容性测试的数据作为参考和交付标准

此处涉及的具有代表性的厂商有,

- MC/PHY IP 厂商: Cadance /SNPS/芯动 等等

- DRAM 厂商:三星/海力士/美光 等等

- 系统厂商(很多,这里只是举个例子):小米(手机)/华为(通信和终端设备)/联想(PC /服务器主机)等等

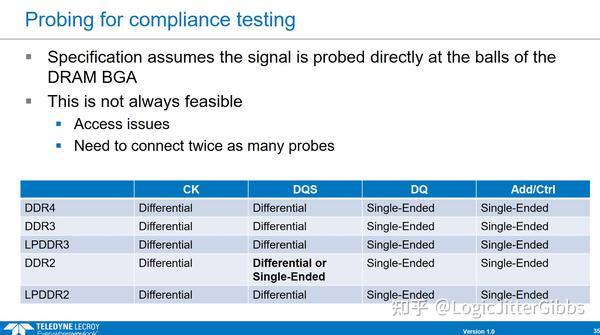

这里提到了兼容性测试所需的测量信号,协议假设信号是从 DRAM BGA 封装的 ball 上直接测量得到的。

一般来说,DRAM 的时钟和 DQS 信号是差分的,DQ 和 CA 信号是单端的。

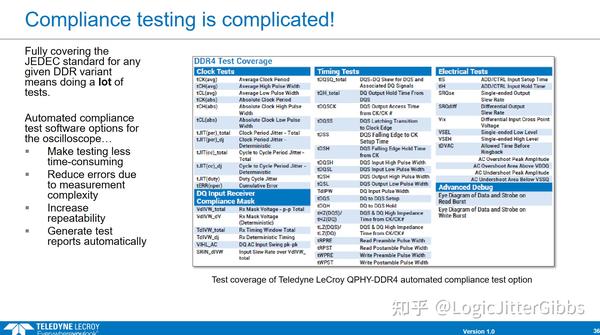

因为需要将 JEDEC 的标准转换为很多个测试变量,所以 DRAM 的兼容性测试是很复杂和繁杂的!

所以我们最好需要一些能在示波器上自动测试的软件,能省不少事,并且能在测试的最后,产生一个相对规整的测试报告。

接下来是一个 DRAM 兼容性测试的例子:

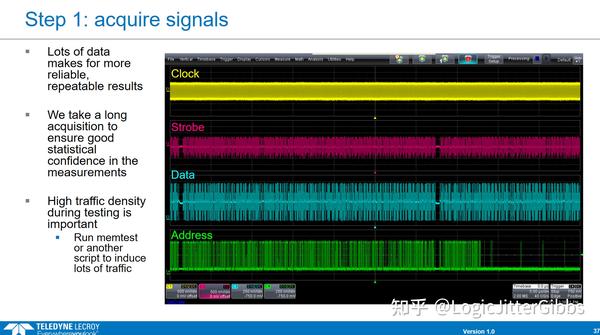

第一步,采集信号,采集尽可能多并且稳定的信号,以获得更高的统计置信度。

在采集信号时,需要在采集时钟内产生尽可能多的 DRAM 访问流量,以获得更多的有效信号。

可以在系统上跑一些 memcopy 之类的脚本。

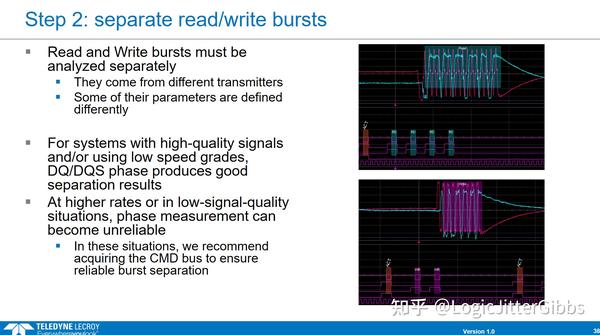

第二步,分别分析读写 burst 数据,读写数据需要分开分析是因为它们来自不同的发送端,并且有些 timing 参数的定义和合理值并不相同。

如果信号质量还不错,或者信号的频率比较低,那么还是可以比较方便地分辨出读写 burst 的。(通过观察 DQS 边沿和 DQ 边沿的关系)

但如果频率高或者信号质量不好时就比较难了,所以这时候推荐同时读取命令总线的信号,用于辅助判断当前是读还是写命令。

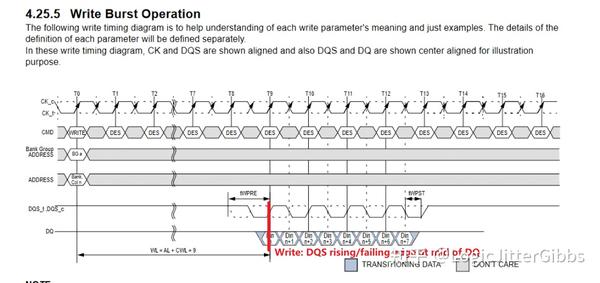

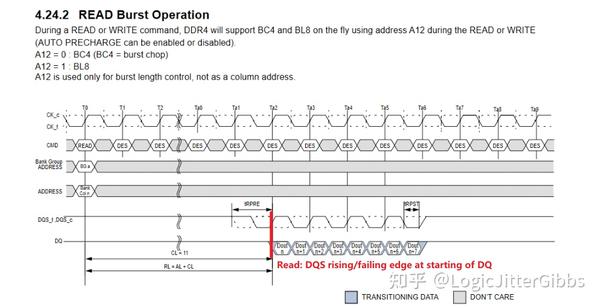

通过以下协议截图可以看到:

- 写数据 DQS 边沿和 DQ 电平中点对齐

- 读数据 DQS 边沿和 DQ 边沿对齐

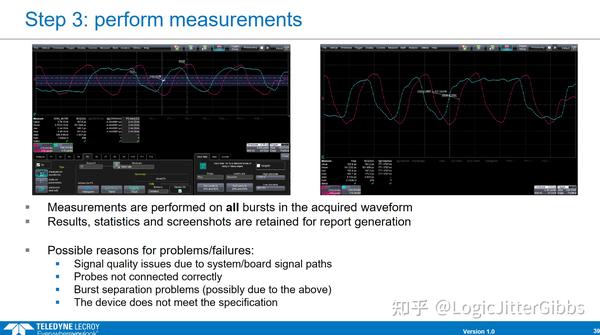

第三步,测量信号,对采集到的 所有 burst 数据进行测量。

在测量中可能会遇到一些问题,比如:

- 因为系统或者 PCB 的信号完整性问题,采集到的信号质量很差

- 探头没有正确地连接

- Burst 数据出现中断的现象(可能是上述的问题导致的)

- 测试结果没能达到协议的要求

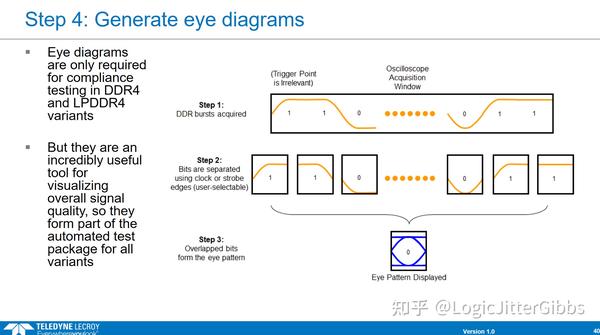

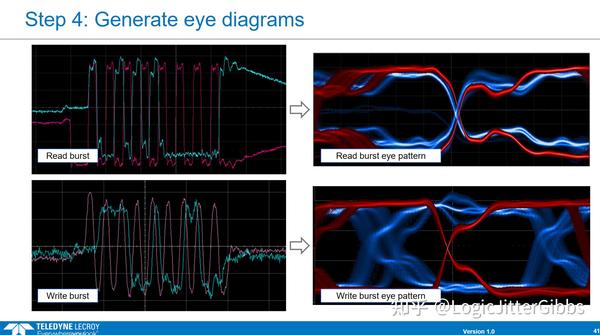

第四步,产生眼图,眼图对 DDR4/LPDDR4 的测试是必须的。但是眼图也是其他 DDR 协议测试中可选的一项,因为眼图是可视化信号质量的重要工具。

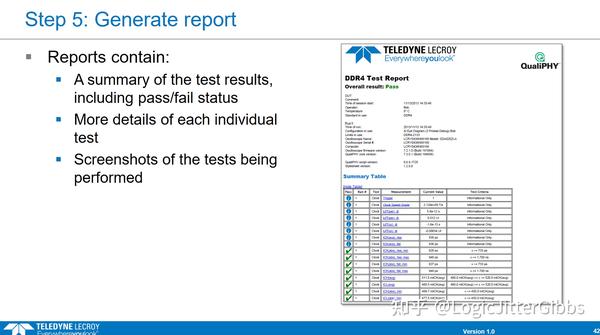

第五步,也是最后一步,是生成测试报告。报告中包括了测试的结果,数据以及相关信号的截图。

DDR 验证和调试的实际例子

接下来举一个实际的 DDR 调试的例子,当然,用的是 LeCroy 的 DDR 调试套件。

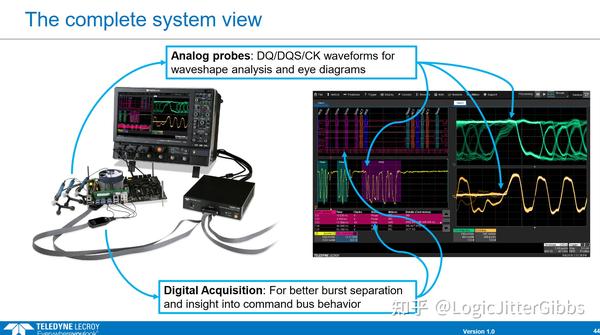

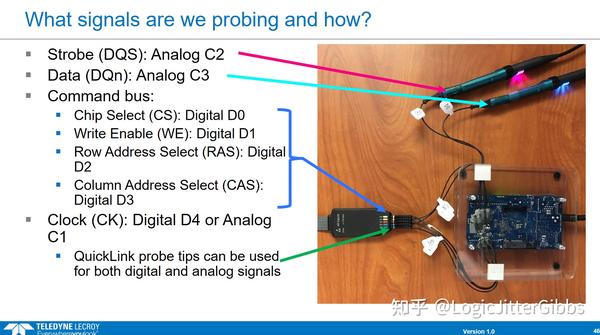

示例系统的组成如下,使用了 L 家的模拟信号采集器和示波器,以及还是 L 家的数据信号采集和分析器,可以显示 DQ、DQS、CK 信号波形和眼图,并同时对照显示 DRAM 命令总线上的数字电平。

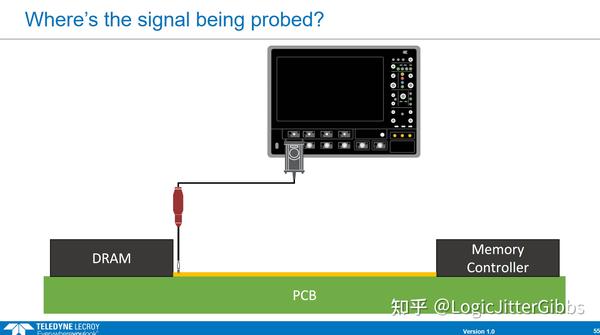

如图是采集的具体信号和连接方式,采集 CK 的探头可以提供数字和模拟两路输出。

多路的采集信号之间需要进行去偏移工作,(以下又是广告时间:)L 家的示波器的 Fast Edge 输出可以帮助你快速做到这点哦。

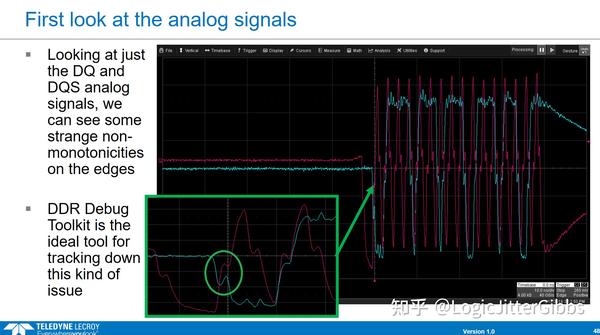

在首先观察模拟信号之后,我们发现 DQS 和 DQ 信号都不太对劲,信号呈现一种非单调变化现象。(以下还是广告时间:)L 家的 DDR debug 套件是帮助你解决这类信号异常现象的好帮手!

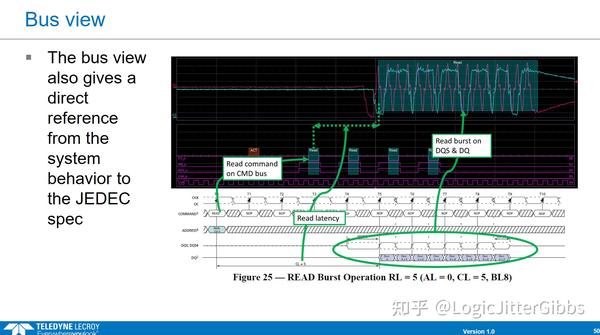

观测的数字总线信号能够标识出当前 DQ/DQS 信号所对应的命令和状态,有助于系统的分析。可以看到图中标识出了当前 Burst 为 4 个连续的读数据,从下方的菜单栏可以看到,Debug 套件还提供特定命令的搜索功能。

总线信号的显示方式可以方便调试者直观地把波形和 JEDEC 标准对照观察。可以从图中清晰直观地看到 CL 的范围。

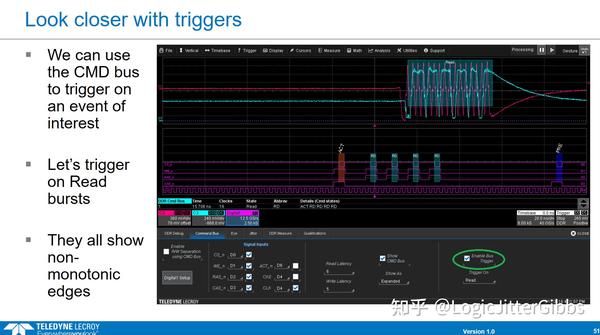

可以将某个命令设为触发事件,如图中所示,将一个 RD CMD 设为了 trigger,设备即捕获了对应的 DQS/DQ 波形,我们观察到 DQS/DQ 信号的不单调现象是普遍存在的。

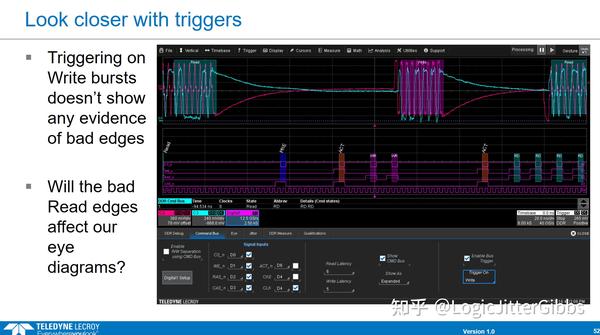

接下来,捕获观察写 Burst 信号,发现并不存在不单调的现象,那么这种现象反映到眼图会怎么样呢。、

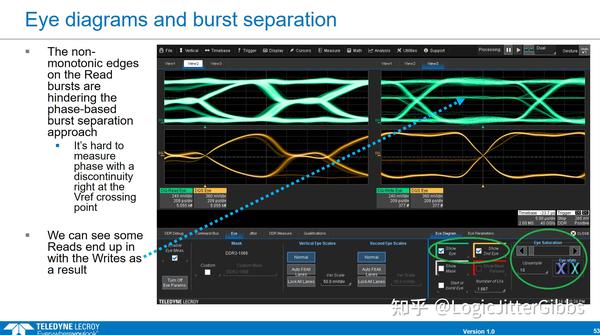

从左侧的读信号眼图可以看到,非单调信号会模糊 DQS 和 DQ 信号的边沿,导致以相位为基准的信号发送和接收模式受到影响,从而容易导致误码。

不过右侧的写信号眼图似乎也有点问题,如图中箭头所示,眼图中间怎么还出了零电平信号,原来这是读信号混入到写信号眼图中导致的。

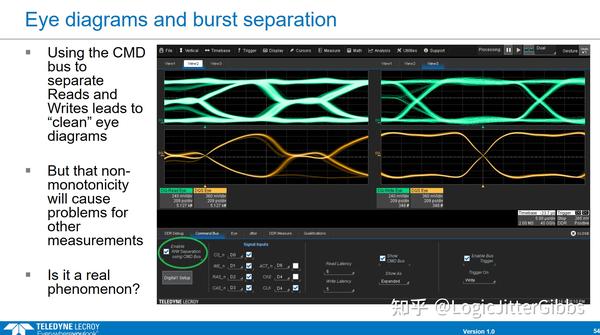

在调整眼图模式,只采集写信号之后,写信号的眼图就完美了。不过该功能需要采集 CMD 总线。

那么上述读信号的问题到底出在哪里呢?

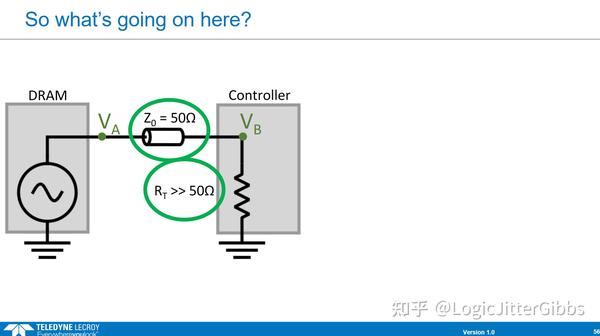

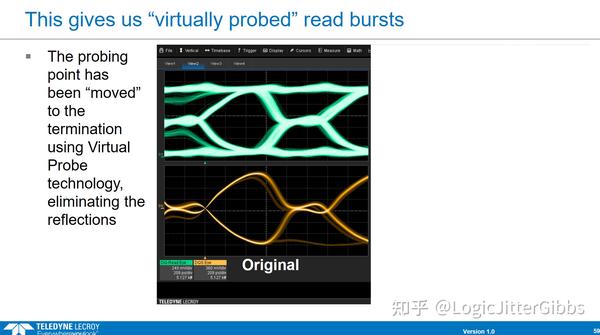

如图是读信号从 DRAM 传输到 Controller 的电路结构,这个问题是由于信号反射叠加到真正的信号上导致的。

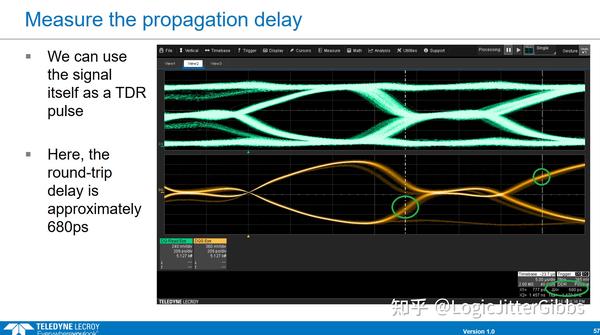

通过波形我们可以测出读信号在这段导线上的往返时间为 680ps

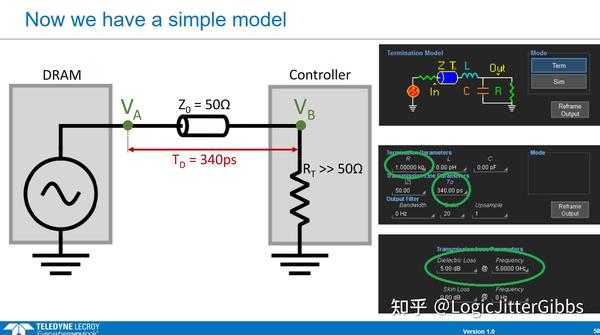

这样一来我们得到一个简单的模型,将相应参数填入调试系统,系统将基于这些参数对反射信号进行抑制。

抑制读信号反射的过程可以认为是我们使用了一个虚拟的探头在 Controller 这一侧测量读信号。

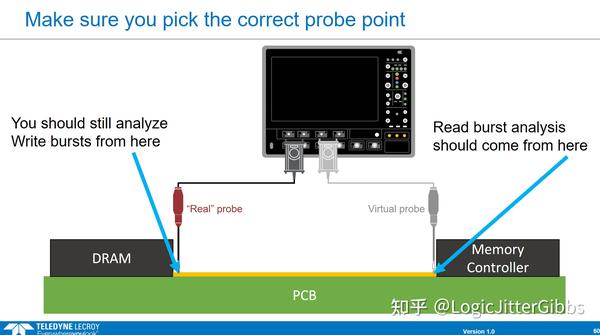

反射问题的本质是,由于探头位于 DRAM 一侧(这样探头比较容易通过我们前文所述的方式附着),所以测量 DRAM 发出的读信号时,会同时接收到从 Controller 一侧反射回来的信号,解决方法是在 Controller 一侧测量读信号,在 DRAM 一侧测量写信号,设备的虚拟探头功能可以帮我们实现这一点。

虚拟探头的本质是设备根据所设参数过滤了反射信号,在此之后,读信号眼图就变得好多了。

L 家的最后一次广告时间,可以访问上述网址获得更多更详细的信息。

结语

本期我们讨论了几个简单的知识点,

- DRAM 测试准备项

- DRAM 兼容性测试

- Case study : DDR 验证与调试

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- PCI Express Technology 3.0 链路初始化与训练 节16 相关配置寄存器

- PCI Express Technology 3.0 链路初始化与训练 节15 动态带宽改变

- 【译文】 On-chip Clock Controller // 片上时钟控制器

- 【译文】PCI Express Technology 3.0 Chapter 8 事务排序

- 【译文】 DFT, Scan and ATPG

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。