4.17 命令、地址总线奇偶校验(C/A Parity)

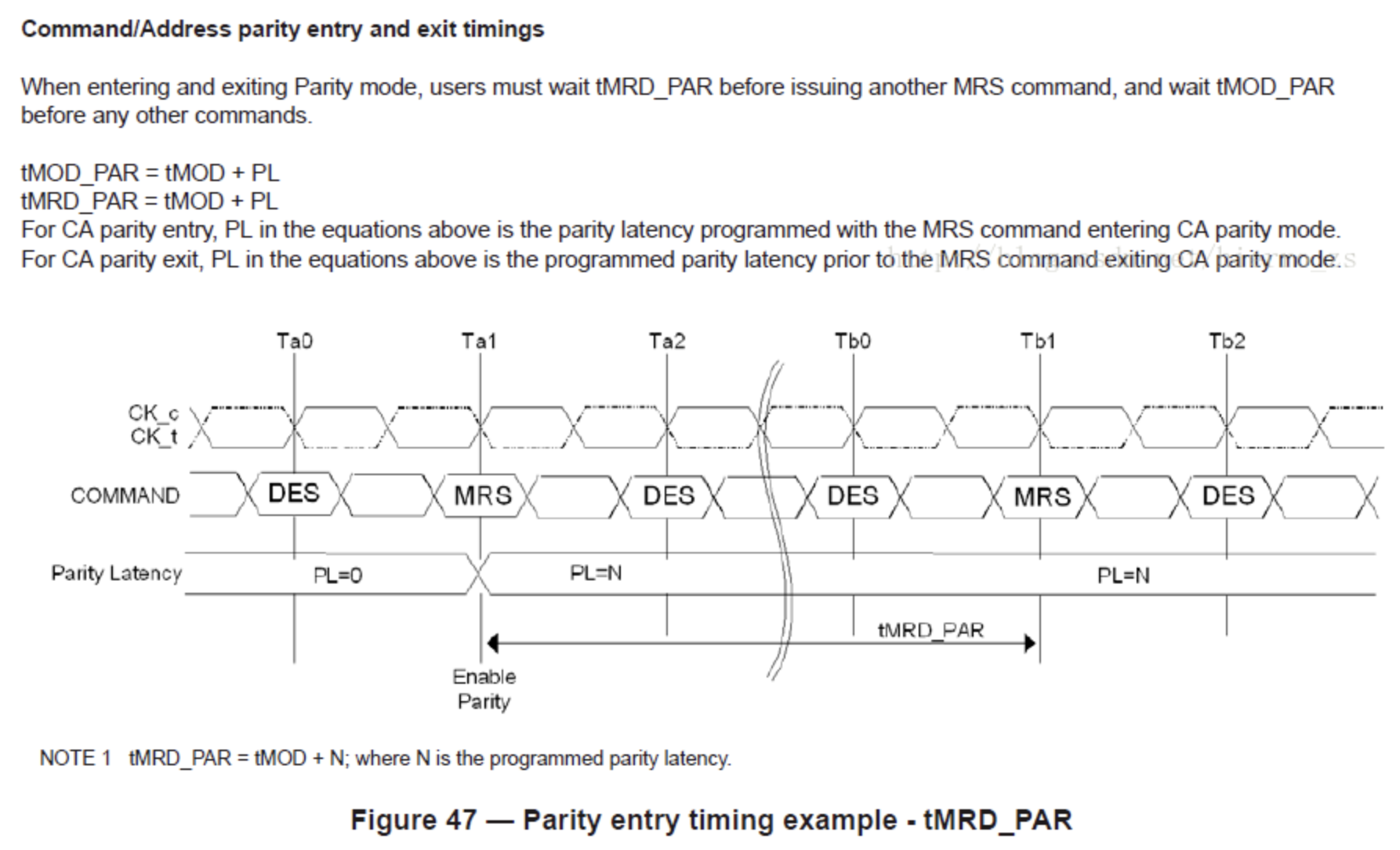

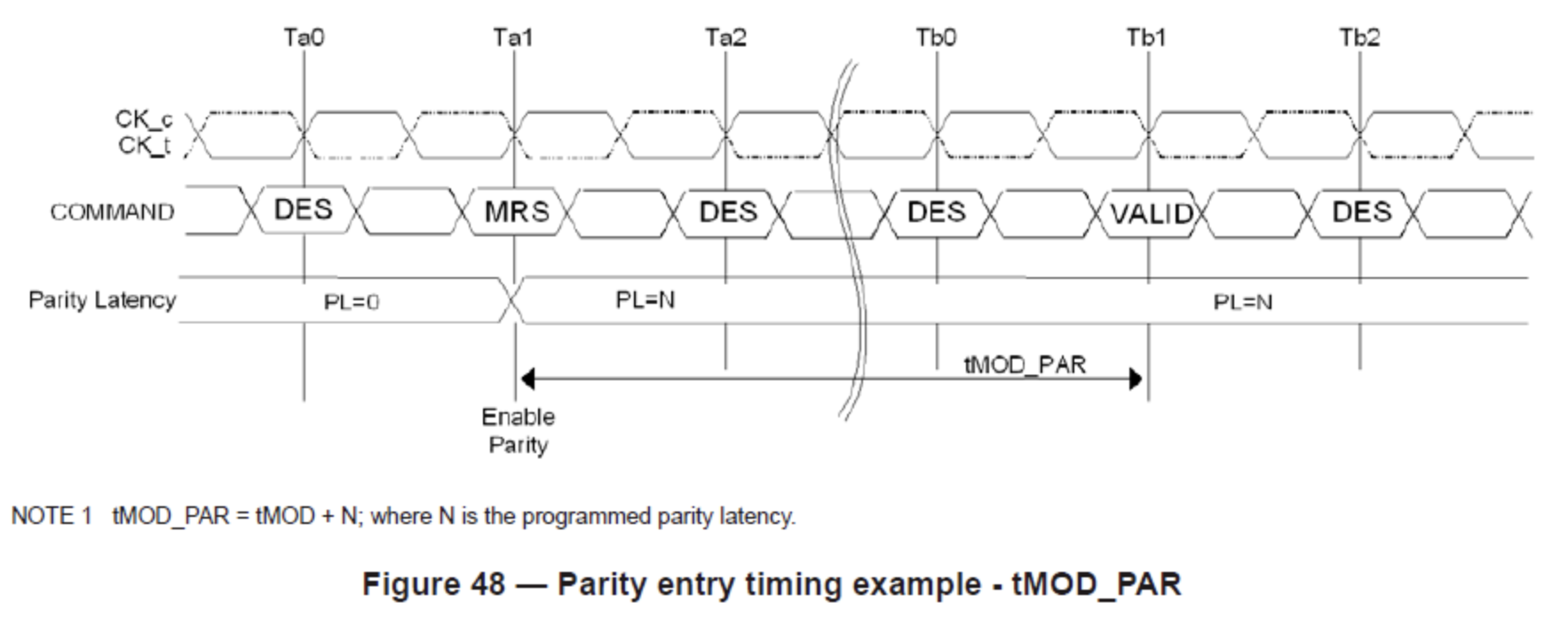

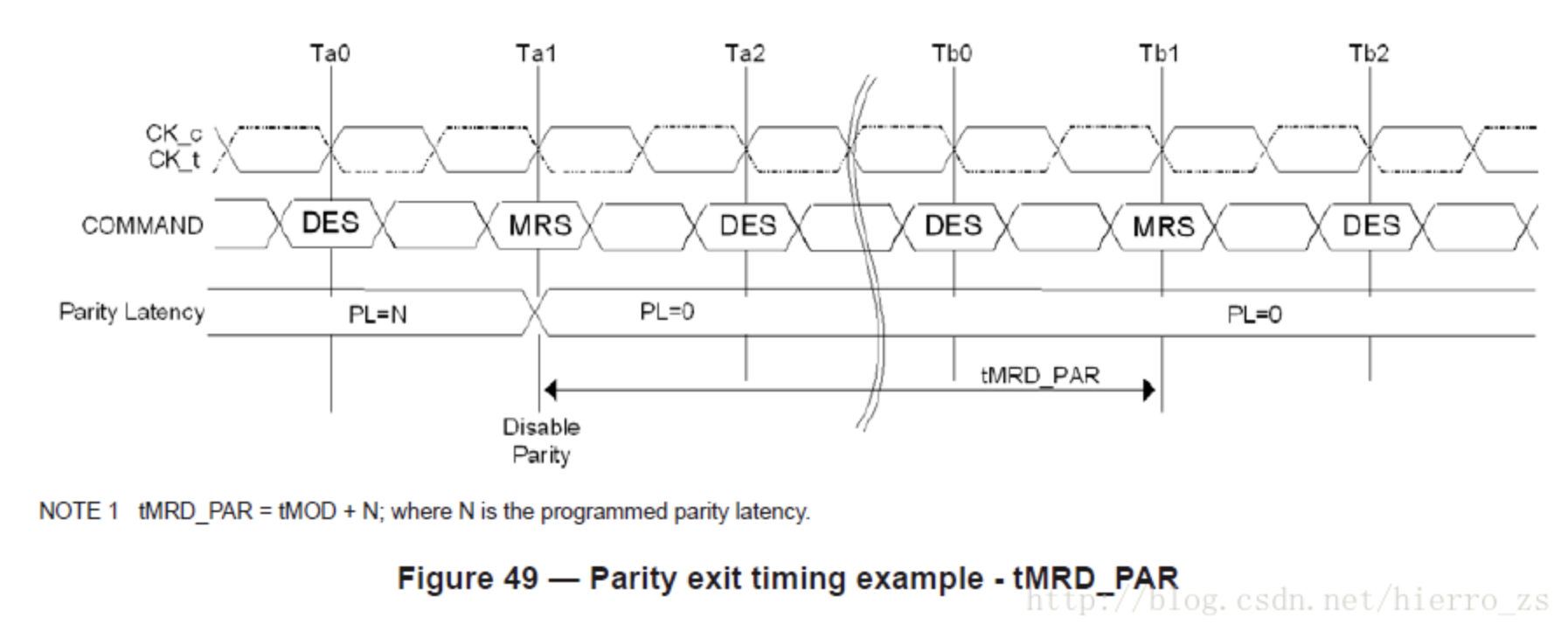

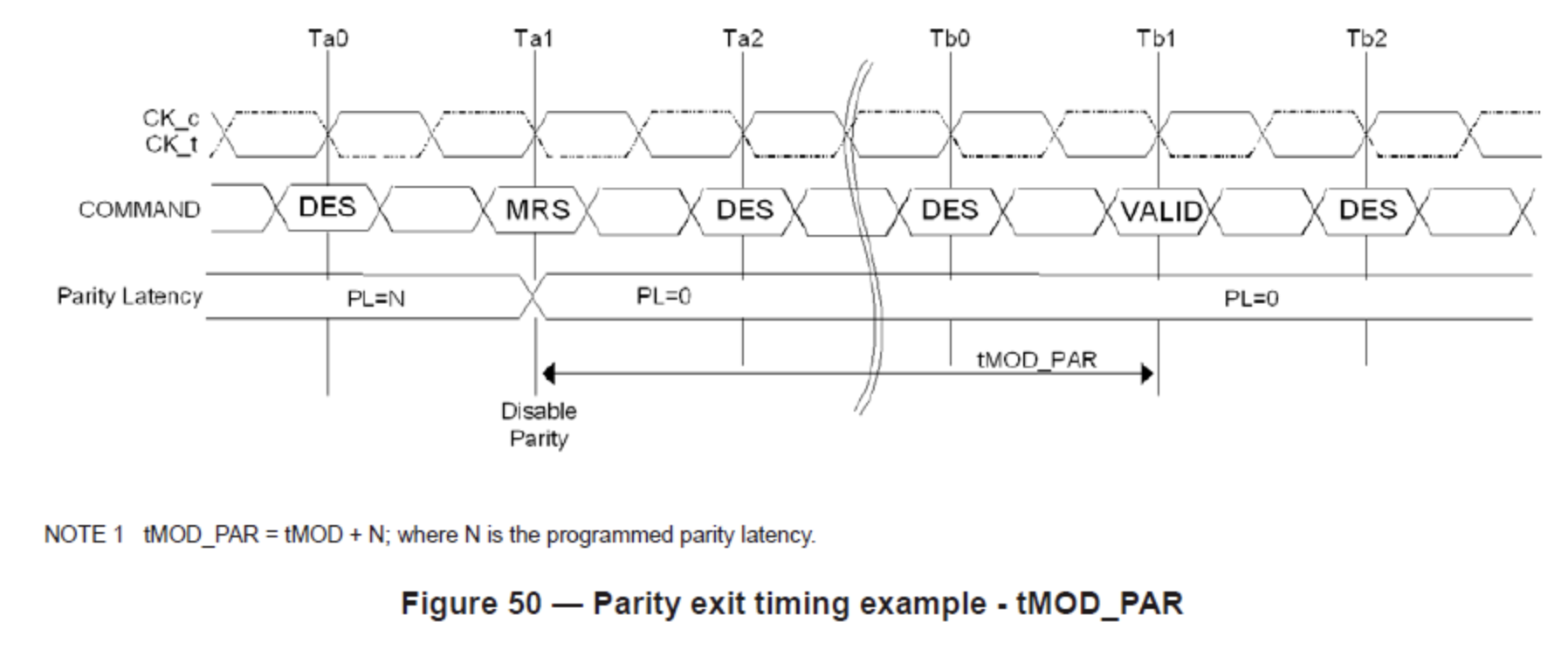

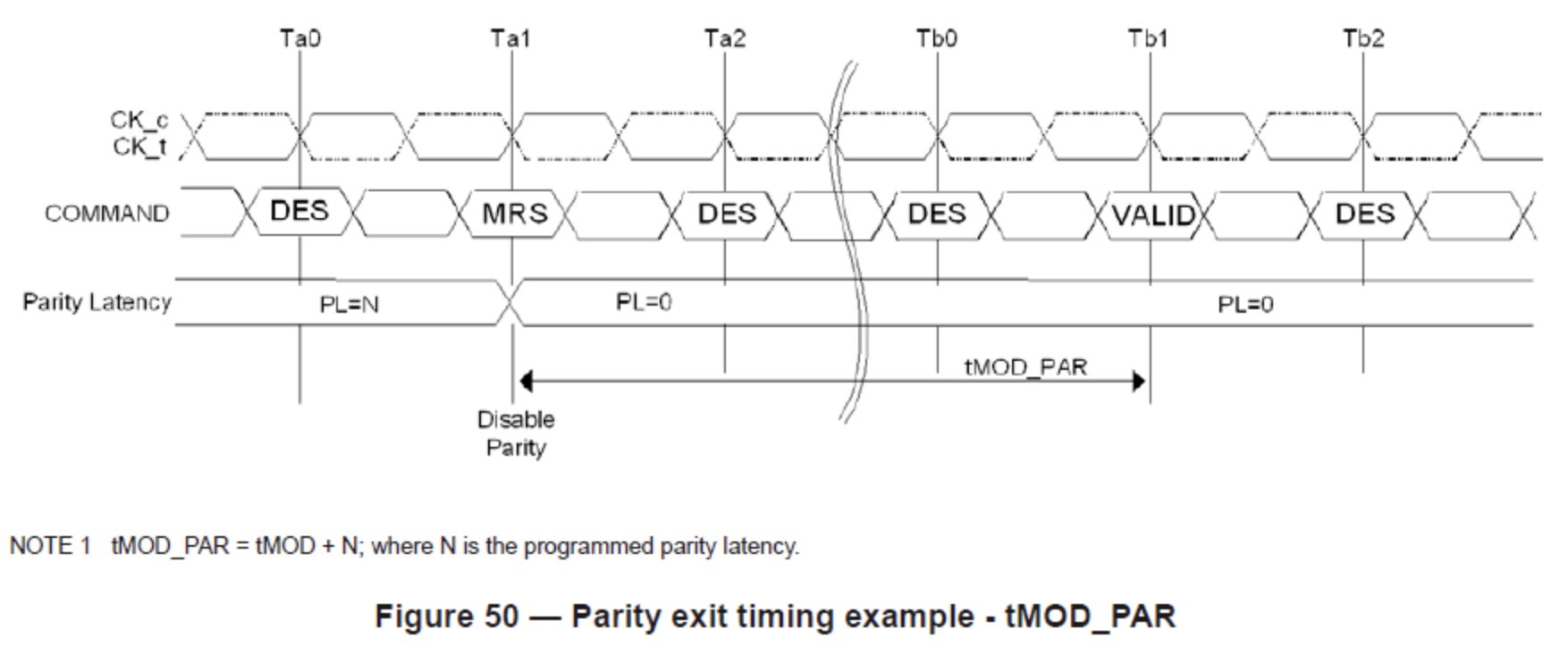

在DDR4 SDRAM中MR2.[A2:A0]是用来打开或关闭C/A Parity的定义域,默认状态位关闭。通过向MR5中的C/A Parity Latency写一个非0值,可以使能C/A Parity功能。但是在使能C/A Parity功能之前需要确保Parity Error位必须为0,也就是说在执行SDRAM命令之前不能有Parity错误。在C/A Parity打开时,对于所有的DRAM命令,Parity的附加延时是相对于C/A Parity关闭的时序的。在C/A Parity开启时,有效命令之间仅能使用DES命令,以防止SDRAM出现任何问题。C/A Parity仅能在DDL-on模式下开启,不支持DDL-off模式。

C/A Parity信号覆盖了ACT_n, RAS_n, CAS_n, WE_n 以及包含Bank地址与Bank Group的地址总线,CKE、ODT、CS_n信号是不包含在内的。DRAM应该将所有未使用的引脚当做0输入处理。比如说,die上将某些引脚悬空了,但是DRAM设备仍然使用了这些引脚,那么DARM内部需要将这些引脚当做0来处理。

Parity的惯用做法是偶校验,即所有用来进行Parity计算的输入包括Parity信号,应该保持为偶数个1。也就是说,通过改变Parity信号的值,来保证所有传输信号(包括Parity信号)中的1的总是为一个偶数。

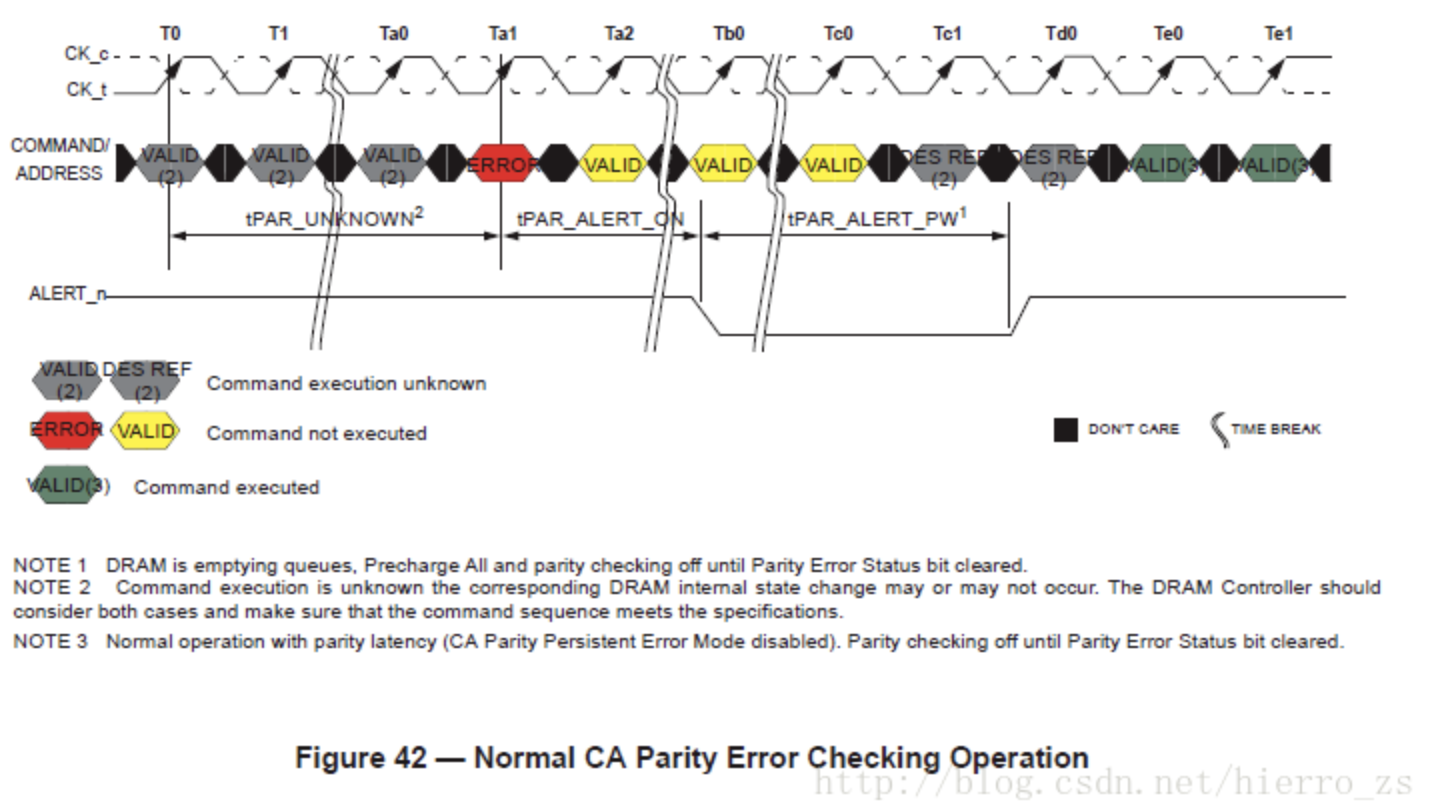

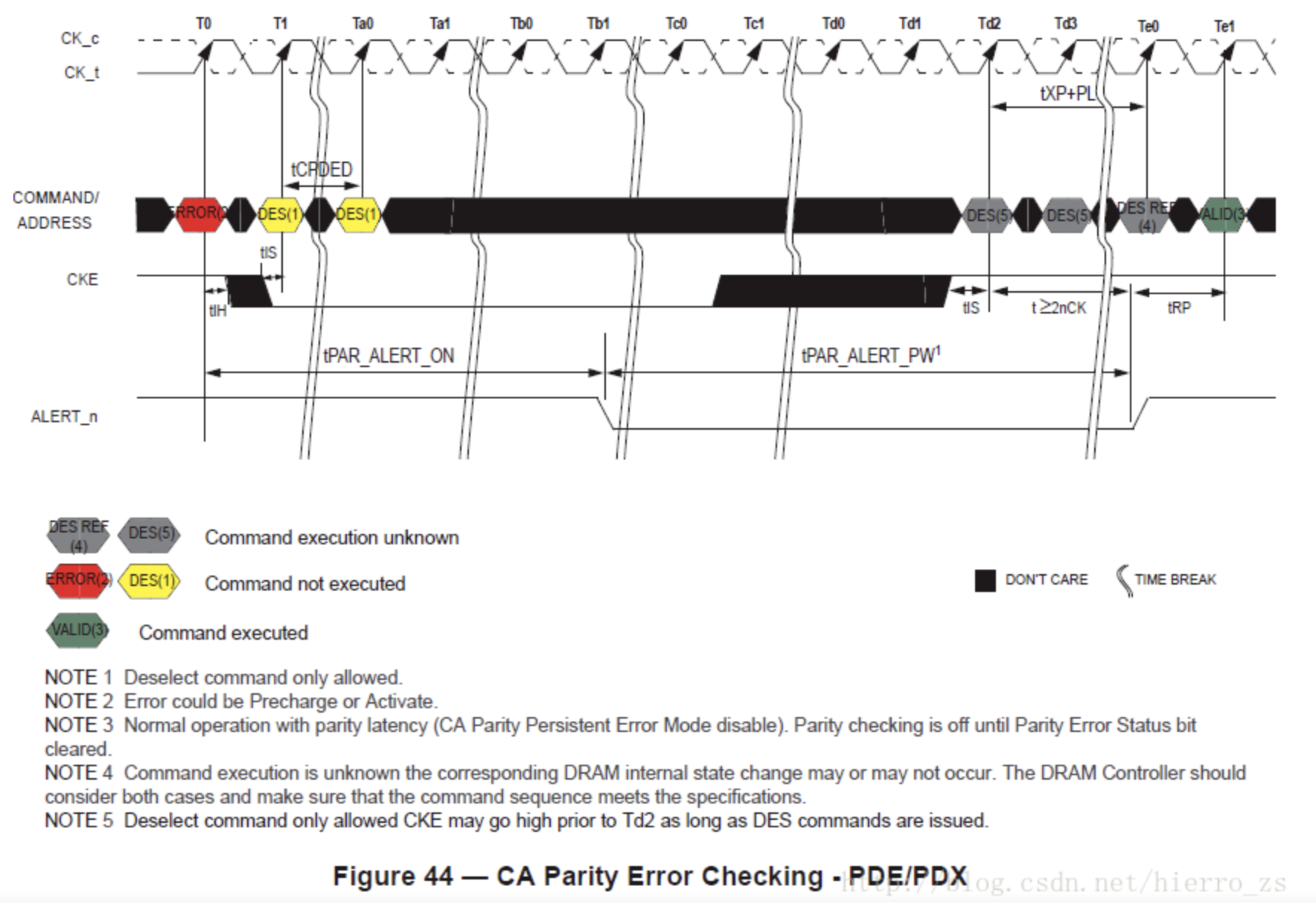

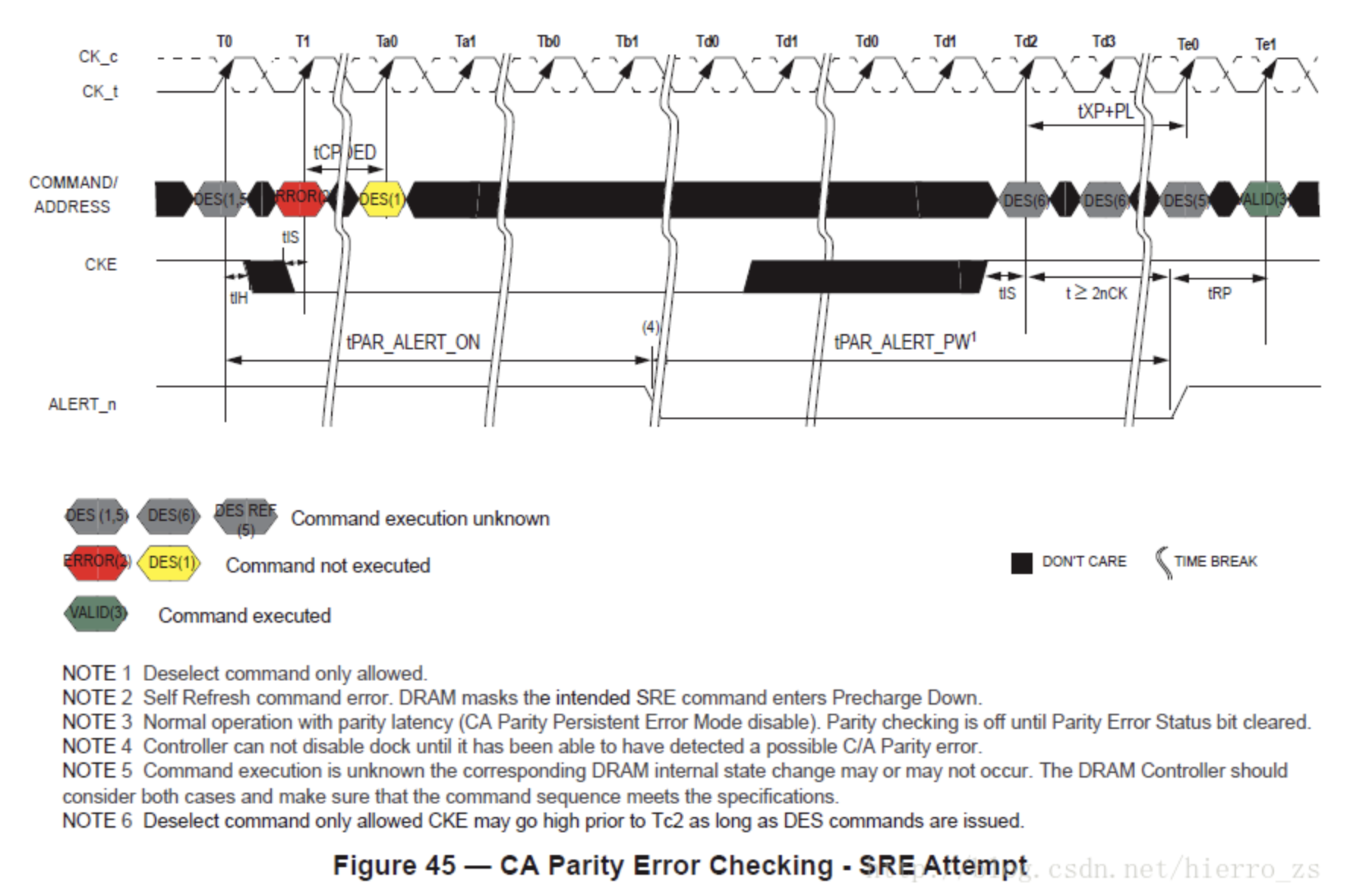

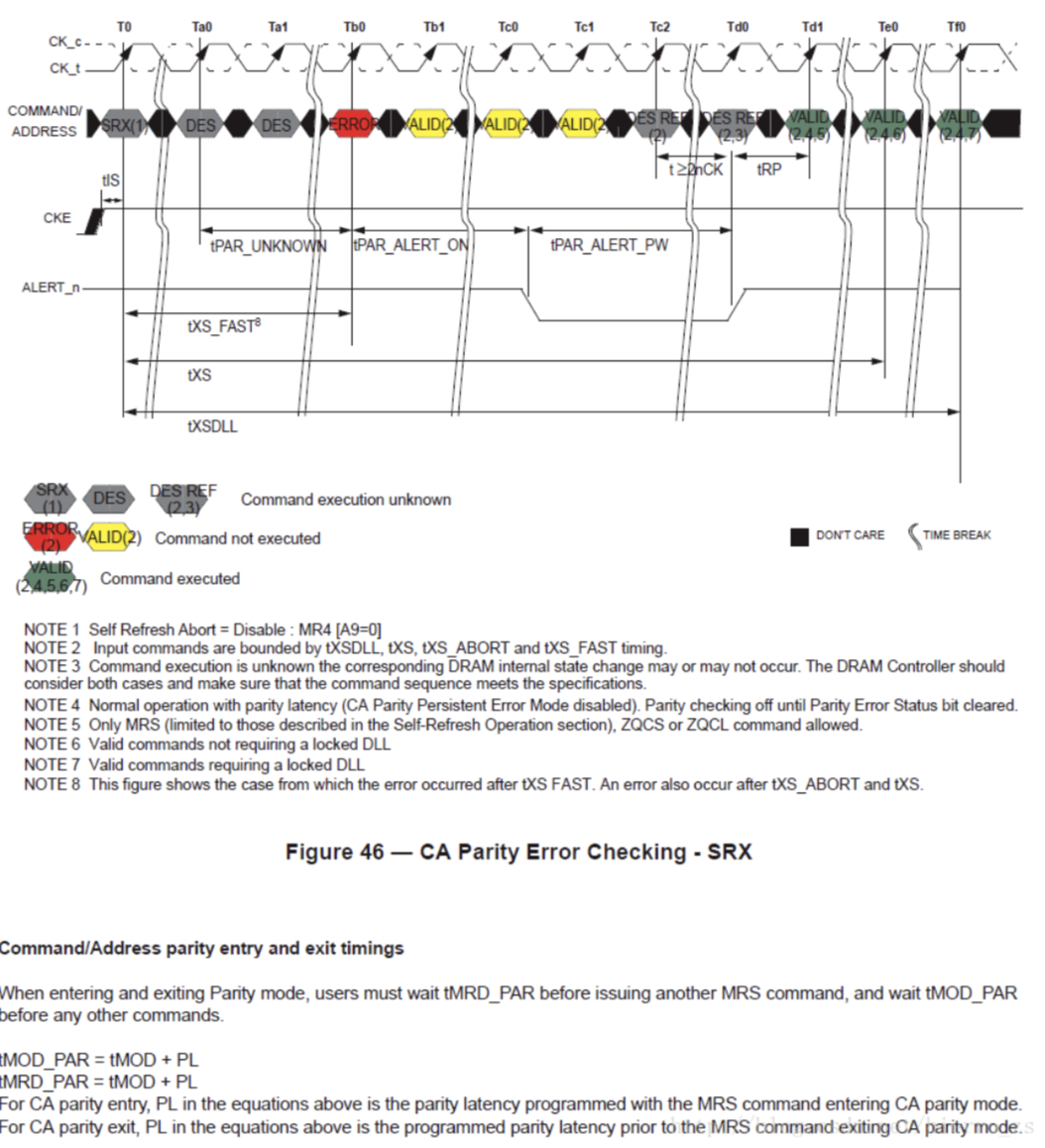

当DRAM检测到了任何一个被CS_n信号确认的命令存在Parity Error时,都需要执行如下步骤。

- 忽略出错的命令。当此错误命令之前的最大时间窗口(tPAR_UNKNOWN)中的命令可能也无法执行,例如,当一个读请求处于这时间窗口时,是不会被执行的,DRAM此时也不会驱动DQS输出。

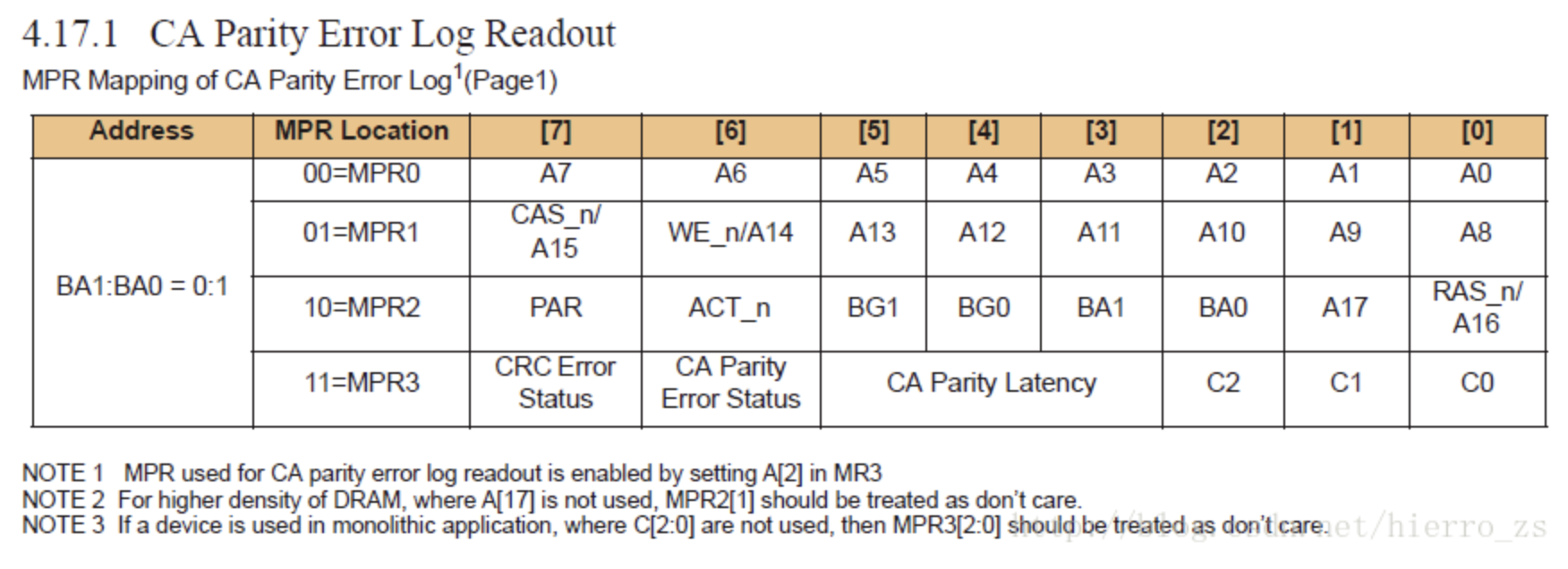

- 将出错的命令与地址位记录在Error Log 中,此Log位于MPR Page 1。

- 将模式寄存器中的Parity Error状态位置为1,Parity Error状态位必须在ALERT_n被DRAM释放之前被置位,即时间tPAR_ALERT_ON + tPAR_ALERT_PW(min)。

- 置位ALERT_n(低电平有效),需要在时间参数tPAR_ALERT_ON内完成。

- 等待所有正在进行的命令完成,这些命令都是在错误命令前的tPAR_UNKOWN时间内到达的。如果在退出自刷新命令后的tXS_Fast 与tXS窗口之间出现了C/A Parity错误,DRAM将延迟ALERT_n的有效时间,以保证正在进行的刷新命令能够顺利完成。

- 在关闭所有的已打开的Page之前,需要保证时间参数tRAS_min满足要求。DRAM在时间窗口tPAR_ALERT_ON + tPAR_ALERT_PW内不能发送任何命令。

- tPAR_ALERT_PW_min时间之后,DRAM可将ALERT_n拉高。

- 当DRAM处于一个已知的预充电状态之后,可将ALERT_n拉高。

- 在时间tPAR_ALERT_ON + tPAR_ALERT_PW之后,DRAM可接受任何其他不同操作的命令。在控制器将Parity Error状态位写为0之前,DRAM不会重新开始检查C/A Parity,在此之前控制器会将所有的命令都当做错误命令来执行。

- 当时间窗口tPAR_ALERT_ON + tPAR_ALERT_PW内出现刷新命令或者刷新命令是第一个有C/A Parity错误的命令,DRAM都会忽略这个刷新命令。此时控制器将按照需求发送额外的刷新周期。

- 在数据窗口tPAR_ALERT_ON + tPAR_ALERT_PW之后,随时可以读取Parity Error状态位,以确定是哪一个DRAM出现了相关的错误。在Parity Error状态位被清零之前,DRAM都会保存第一个错误命令的所有错误信息。

C/A Parity错误在模式寄存器中的定义如下。C/A Parity Latency为只可写,C/A Parity Error Status为可读可写,C/A Parity Log为只读。控制器仅可把C/A Parity Error Status写为0。若控制器强行将C/A Parity Error Status写为1,DRAM将选择性的阻塞此写请求。

在DDR4 SDRAM中,MR5.A9=1可使能“固定奇偶错误模式”。当此功能打开后,DRAM会在ALERT_n无效之后继续监测C/A Parity,即使此时C/A Parity Error Status为高电平。如果在错误状态位被清零之前,连续出现C/A Parity错误,那么此时MPR Page 1中的Error Log必须被视为无效。在固定奇偶错误模式下,ALERT_n信号保持有效脉冲的最小与最大时间需要遵循时间参数tPAR_ALERT_PW。当控制器检测到ALERT_n有效时,需要立马发送DES命令。发送DES的反应时间需要遵循时间参数tPAR_ALERT_RSP。

下图表示了出现C/A Parity 错误与ALERT_n信号有效的时序图。

4.18 控制器降档模式(Controller Gear Down Mode)

以下的几项描述了降档模式的进入序列。DRAM默认下是采用1/2的时钟比例,并且使用了低频的MRS命令模式,在每个MRS命令之前都增加了一个同步脉冲,从而可以与1/4时钟模式下操作命令总线的CS_n,CKE,ODT信号的在合适的时钟下对齐。在1/2模式下,不需要额外的MRS命令与同步脉冲来进入降档模式,且DRAM默认是处于1/2模式中的。

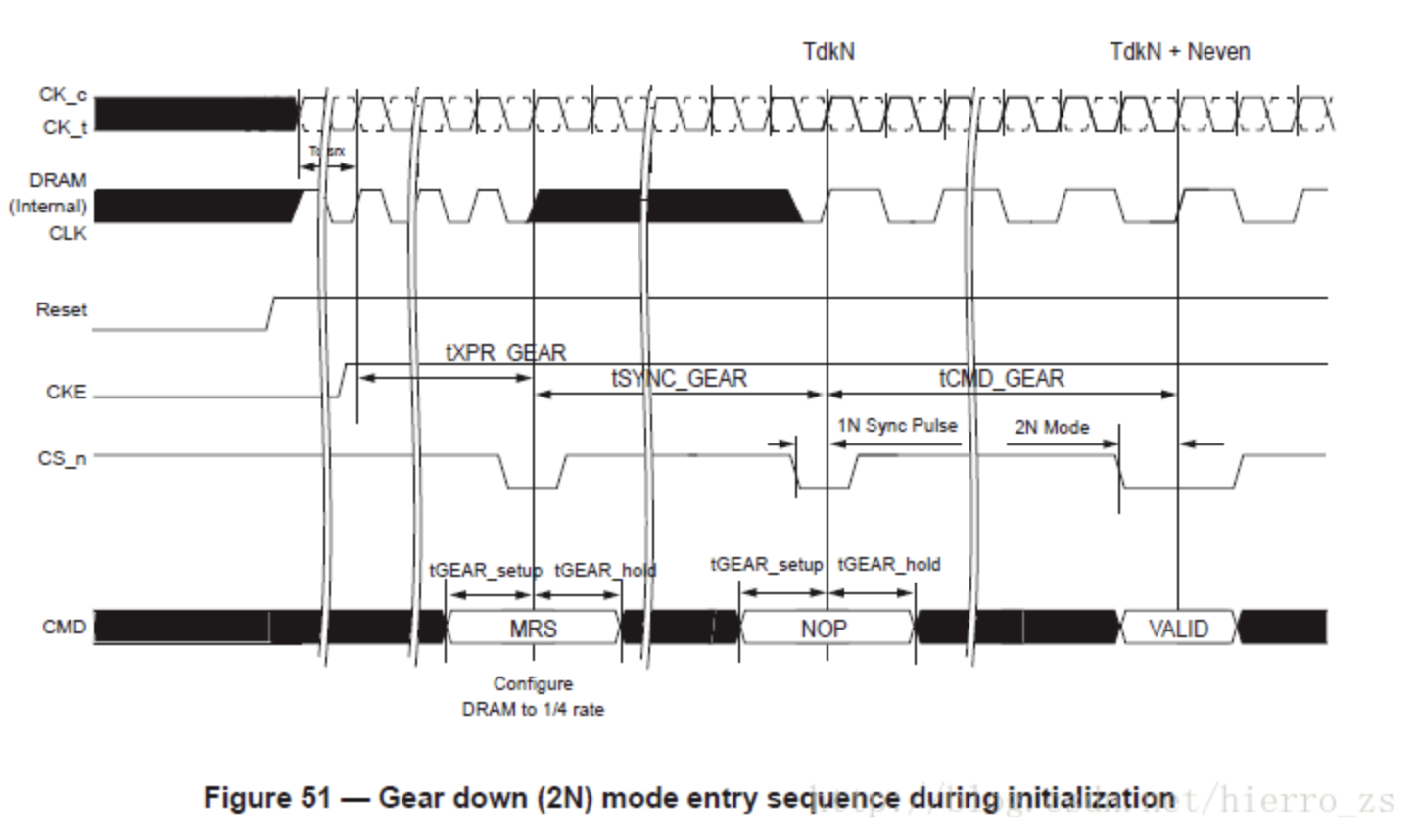

在初始中进入降档模式的序列如下所示:

- 在上电或初始化过程中,DRAM默认是处于1/2模式下。

- Reset有效,低电平有效。

- CKE有效,高电平有效,使能相应的Rank

- 通过一个N倍CK的低频CMD降档命令来实现MRS命令。此低频MRS命令也是通过一个1倍CS_n信号来确认的。

- 控制器通过发送一个N倍的NOP命令来实现一个1倍的同步脉冲,tSYCN_GEAR是一个偶数个时钟周期的参数。同时,同步脉冲也是从CMD命令的偶数个上升沿开始的。

- 在tCMD_GEAR时间之后开始2倍时钟下普通命令的操作。

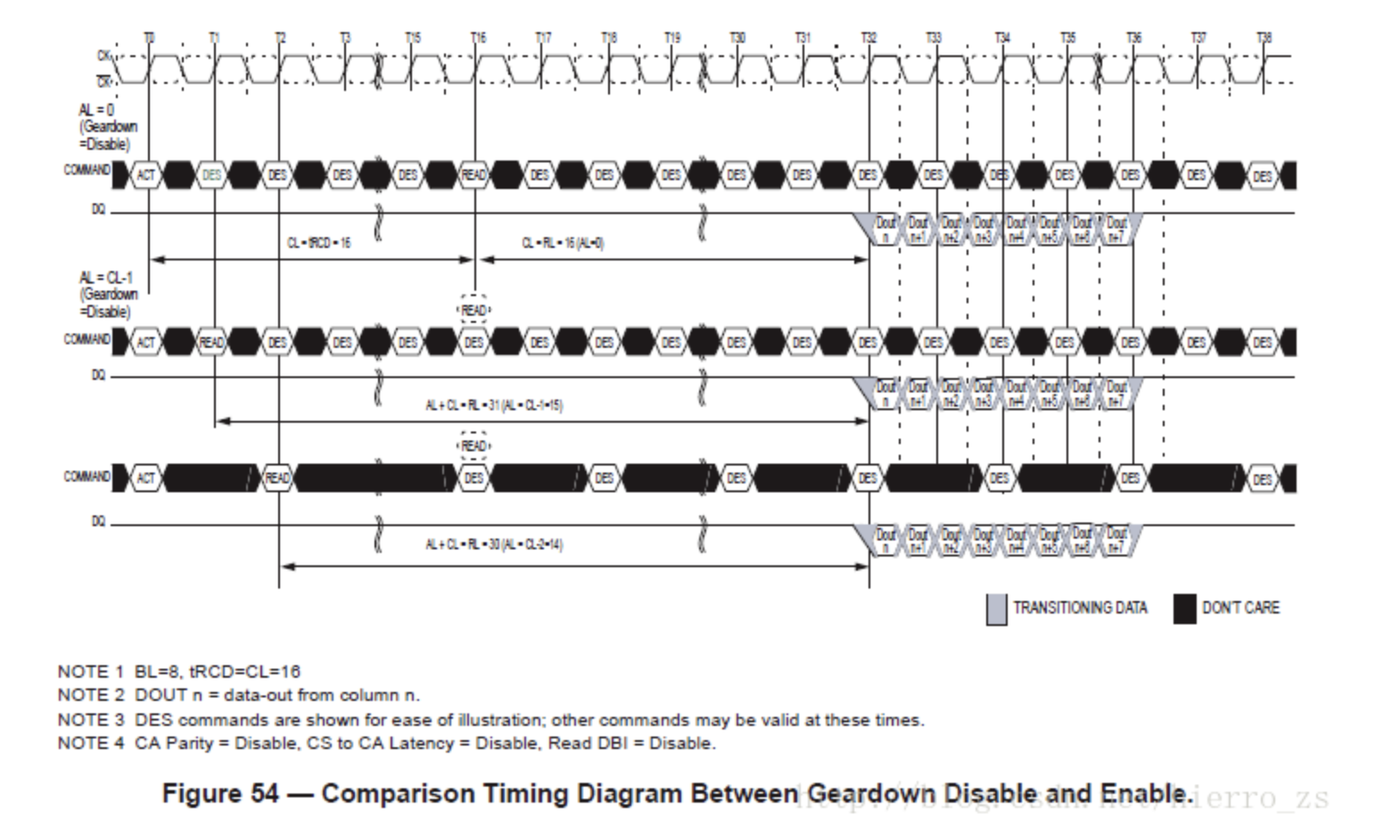

在1/4模式中的降档操作,需要使用如下的模式寄存器配置:

- CAS Latency (MR0 A[6:4,2]) : Even numbers

- Write Recovery and Read to Precharge (MR0 A[11:9]) : Even numbers

- Additive Latency (MR1 A[4:3]) : 0, CL -2

- CAS Write Latency (MR2 A[5:3]) : Even numbers

- CS to Command/Address Latency Mode (MR4 A[8:6]) : Even numbers

- CA Parity Latency Mode (MR5 A[2:0]) : Even numbers

下图中描述了在上电过程中,2N模式下的控制操作

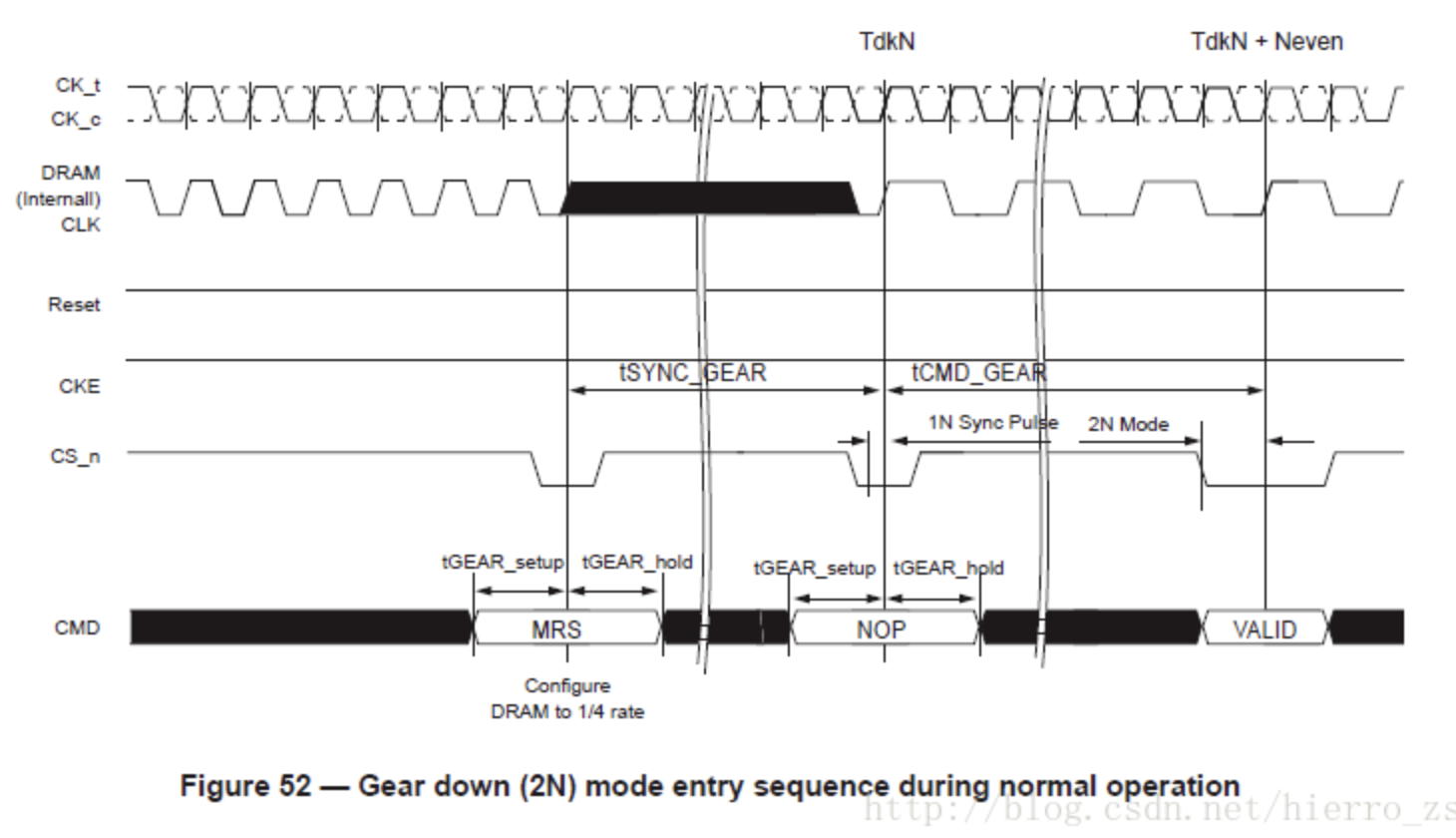

在CKE与RESET都设置为高电平时,geardown(1/2 rate to 1/4 rate)mode中的不同操作。

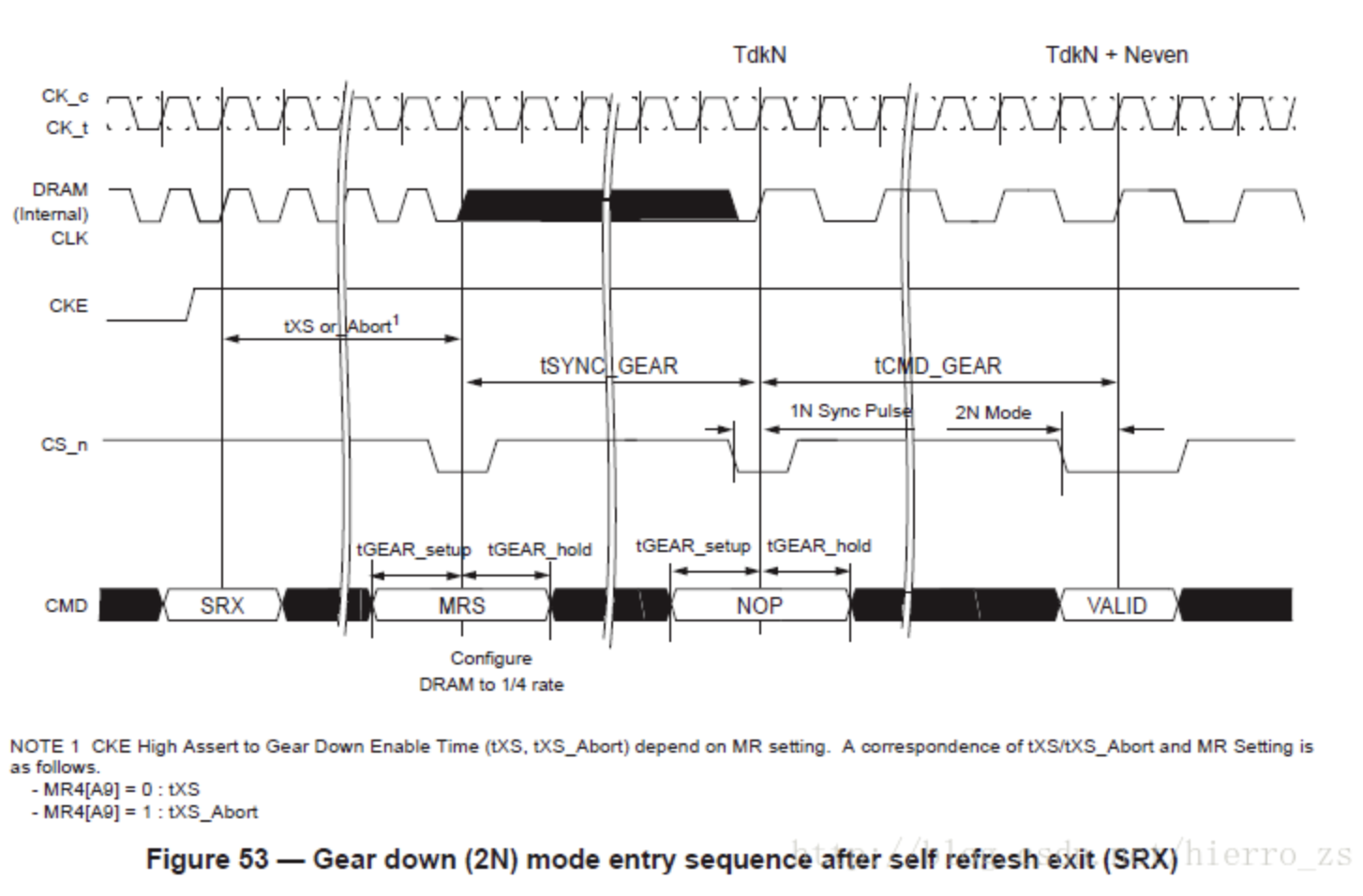

如果在进入或退出自刷新时操作1/2模式(1N),不需要MRS命令或同步脉冲,第一个有效命令之前的最小退出延时为tXS或tXS_Abort。如果在进入或退出自刷新时操作1/4模式(2N),DRAM需要MRS命令或者是同步脉冲,如下图所示。DRAM需要在自刷新模式和最大低功耗模式内部从2N模式复位至1N模式,由此可通过同步脉冲来与合适的时钟对齐。在自刷新模式中的操作如下图所示。

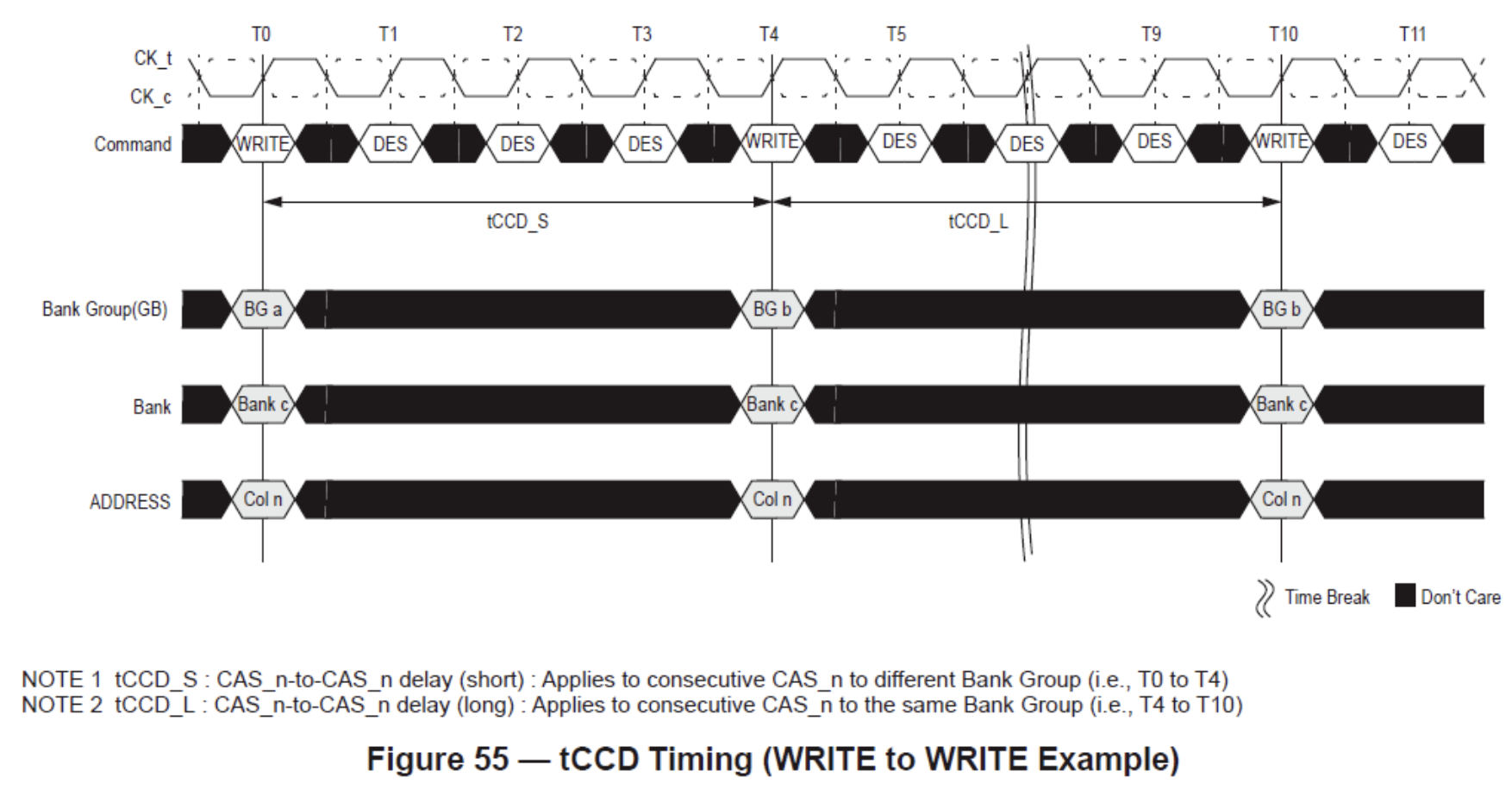

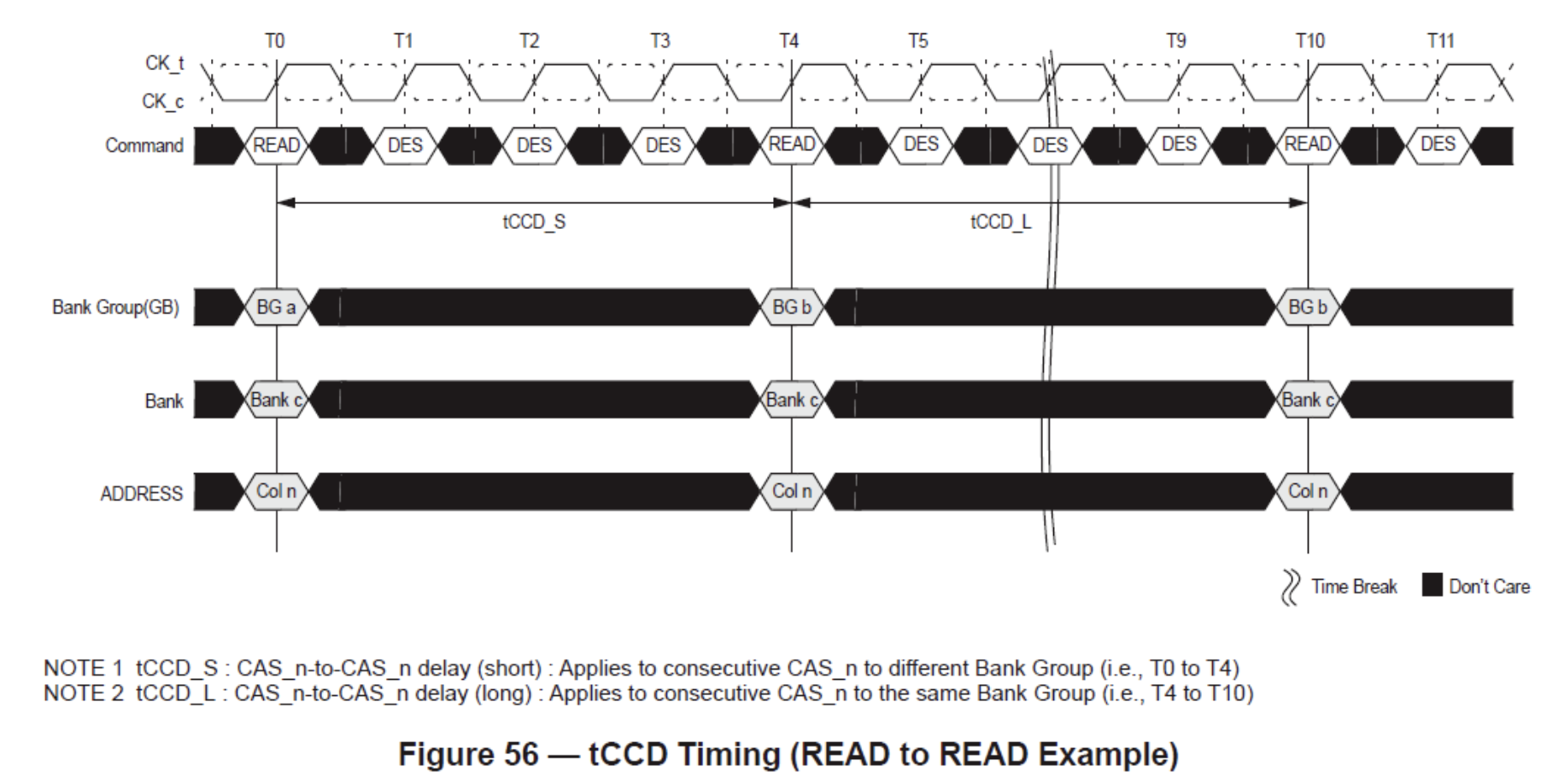

4.19 DDR4核心时序

原文:CSDN

作者:hierro_sic

相关文章推荐

- JESD79-4 第4章 SDRAM命令描述与操作(4.14-4.16)

- JESD79-4 第4章 SDRAM命令描述与操作(4.11-4.13)

- JESD79-4 第4章 SDRAM命令描述与操作(4.8-4.9)

- JESD79-4 第4章 SDRAM命令描述与操作(4.5-4.7)

- JESD79-4 第4章 SDRAM命令描述与操作(4.1-4.4)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。