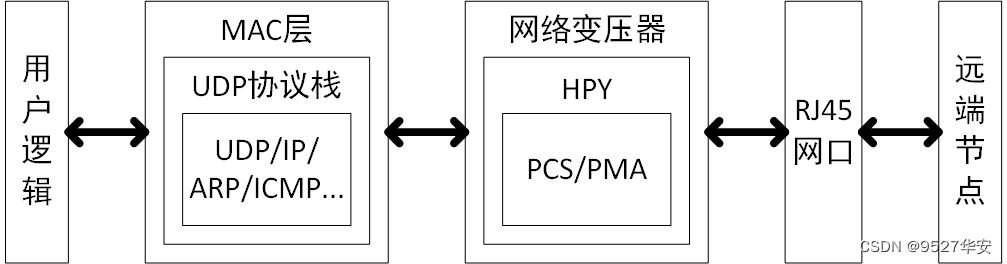

FPGA基于AXI 1G/2.5G Ethernet Subsystem实现千兆UDP通信 提供工程源码和技术支持

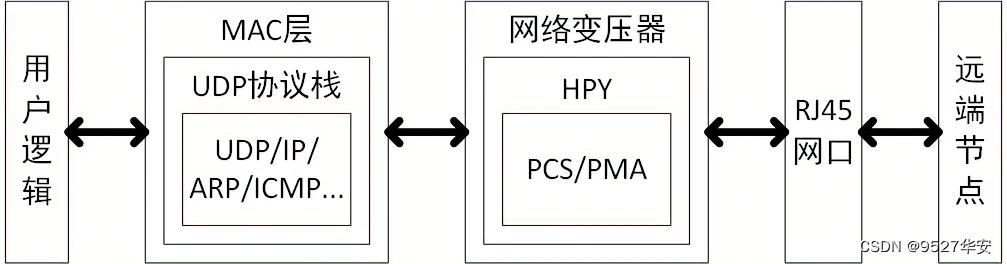

FPGA实现10G万兆网UDP通信 10G Ethernet Subsystem替代网络PHY芯片 提供工程源码和技术支持

FPGA基于SFP光口实现10G万兆网UDP通信 10G Ethernet Subsystem替代网络PHY芯片 提供工程源码和技术支持

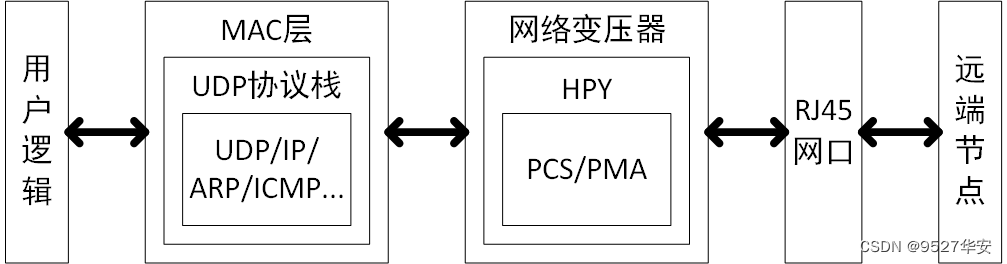

FPGA基于SFP光口实现1G千兆网UDP通信 1G/2.5G Ethernet PCS/PMA or SGMII替代网络PHY芯片 提供工程源码和技术支持

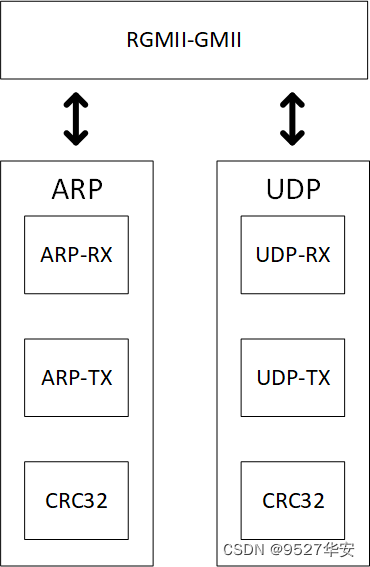

目前网上的fpga实现udp基本生态如下:1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是...

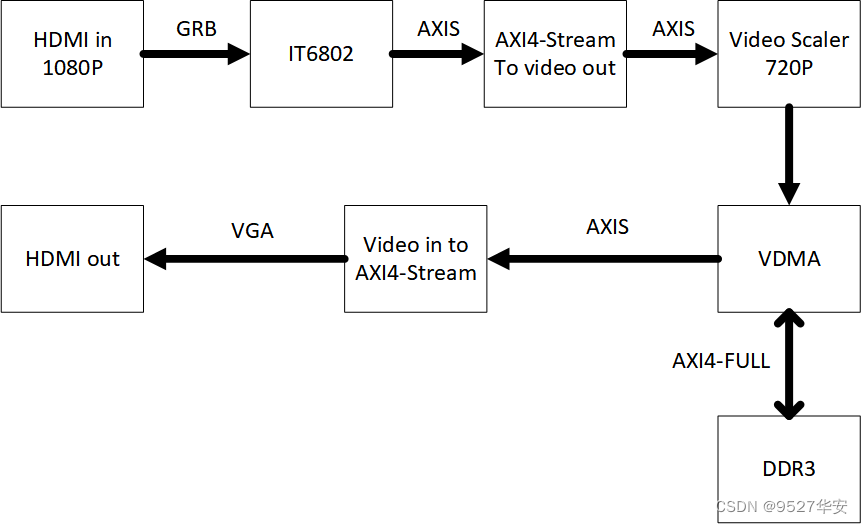

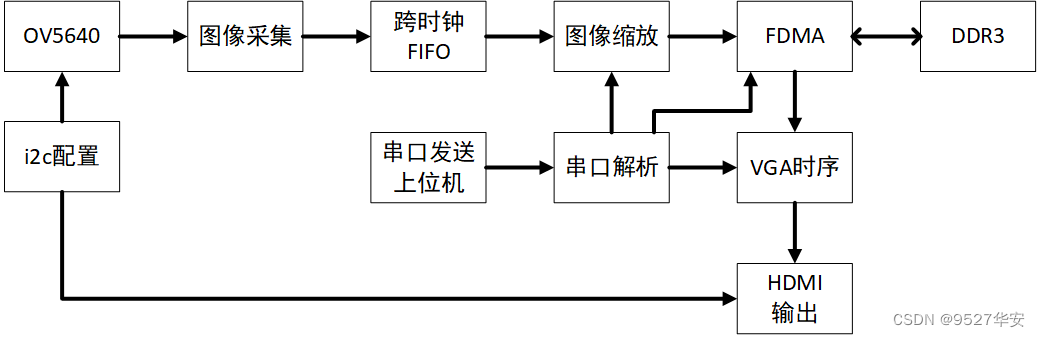

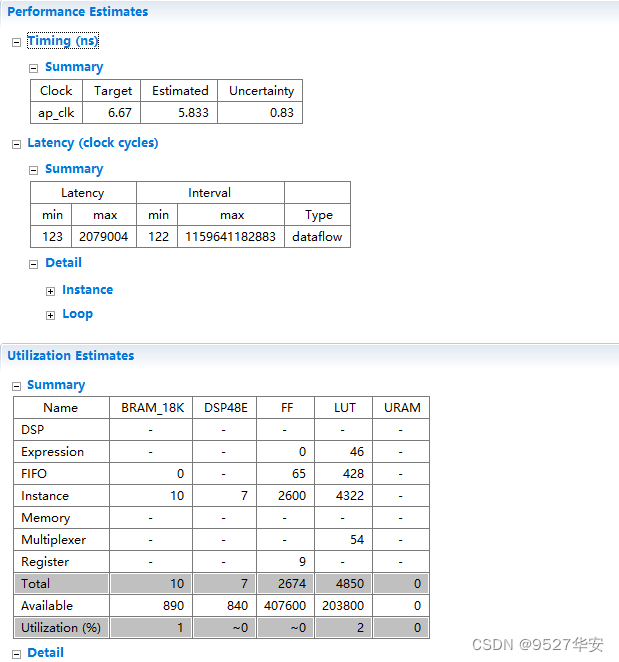

本设计图像缩放算法采用双线性插值,实现方式是Xilinx的HLS,采用C++语言实现代码级功能,再有HLS2019.1综合编译导出RTL级verilog代码,...

目前网上的fpga实现udp基本生态如下:1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是...

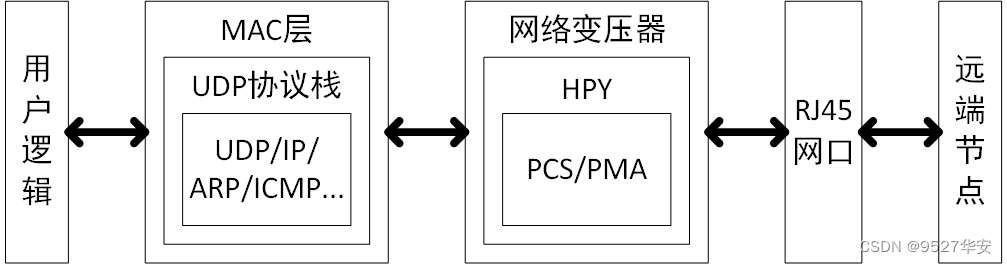

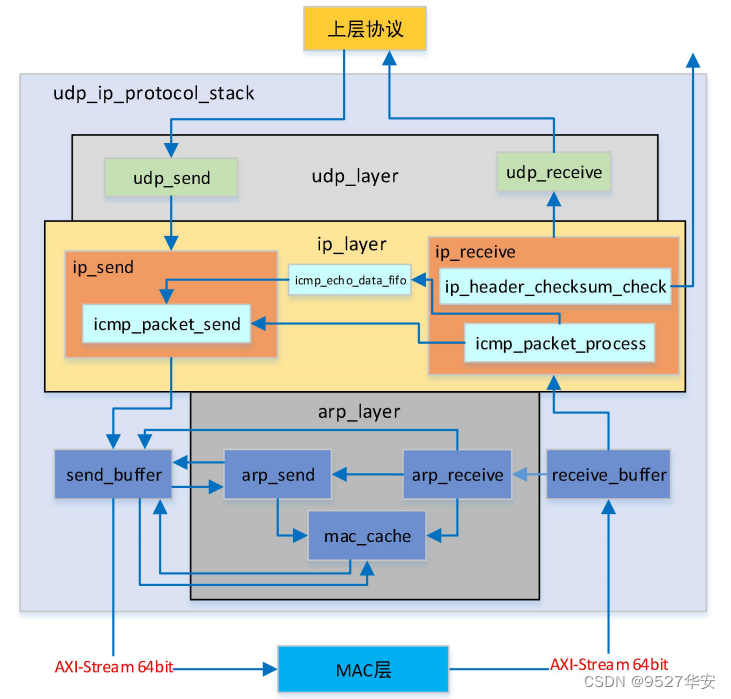

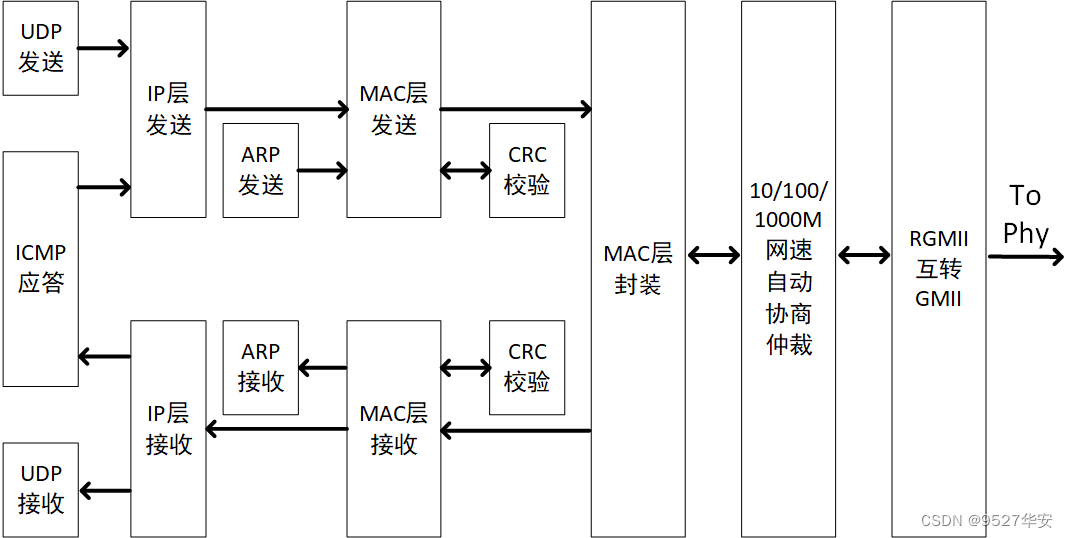

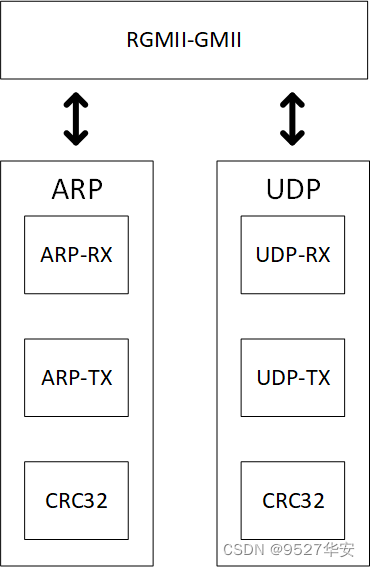

FPGA纯verilog实现UDP通信,三速网自协商仲裁,动态ARP和Ping功能,提供工程源码和技术支持

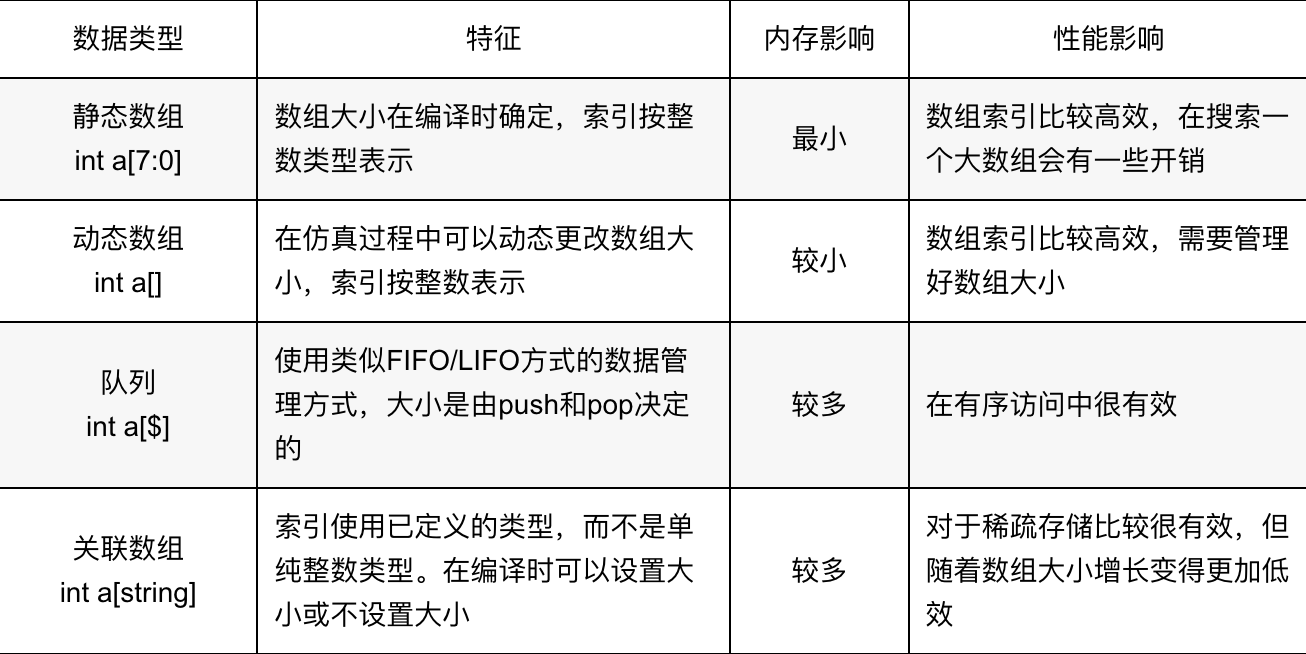

本文旨在帮助大家降低在编码过程中写出低性能和耗内存的概率,只要大家在写代码时稍注意下,积少成多。当然,使用代码分析工具也可以调...

目前网上的fpga实现udp基本生态如下:1:verilog编写的udp收发器,但不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是...

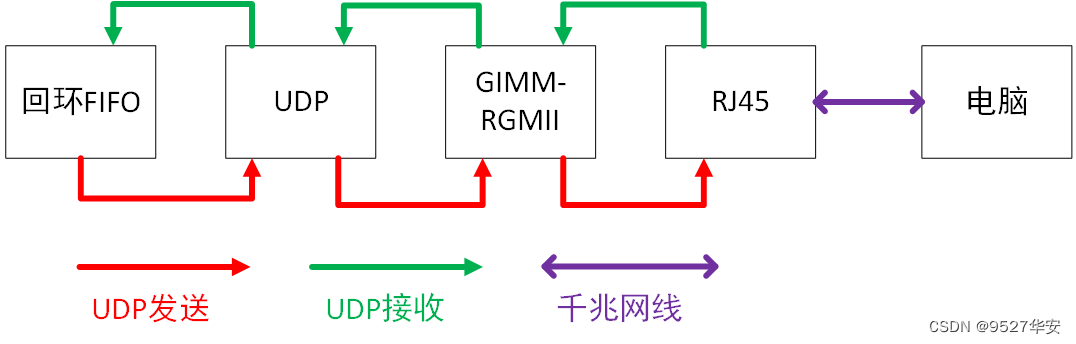

精简版UDP协议是一种资源占用少,不限FPGA硬件平台,纯Verilog代码实现的UDP通信方案,经本人反复验证,稳定性很高,关于精简版UDP请参...

FPGA实现UDP协议可难可易,具体根据项目需求而定,目前项目上的需求大概有如下几种:1、使用Xilinx系列FPGA实现UDP通信,且传输的数据量...

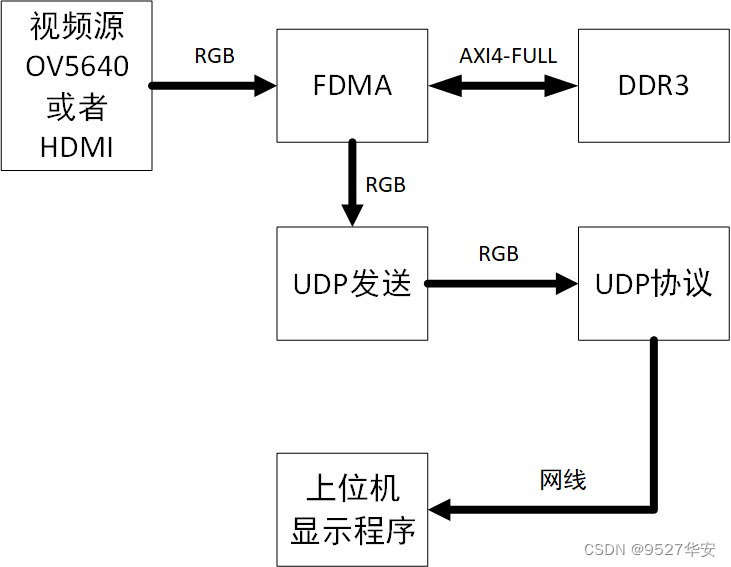

FPGA实现UDP传输是FPGA在通信领域的应用之一,只要有UDP收发模块,那么实现UDP传输就只剩下数据组包的事项了;之前我写过一篇文章介绍过...

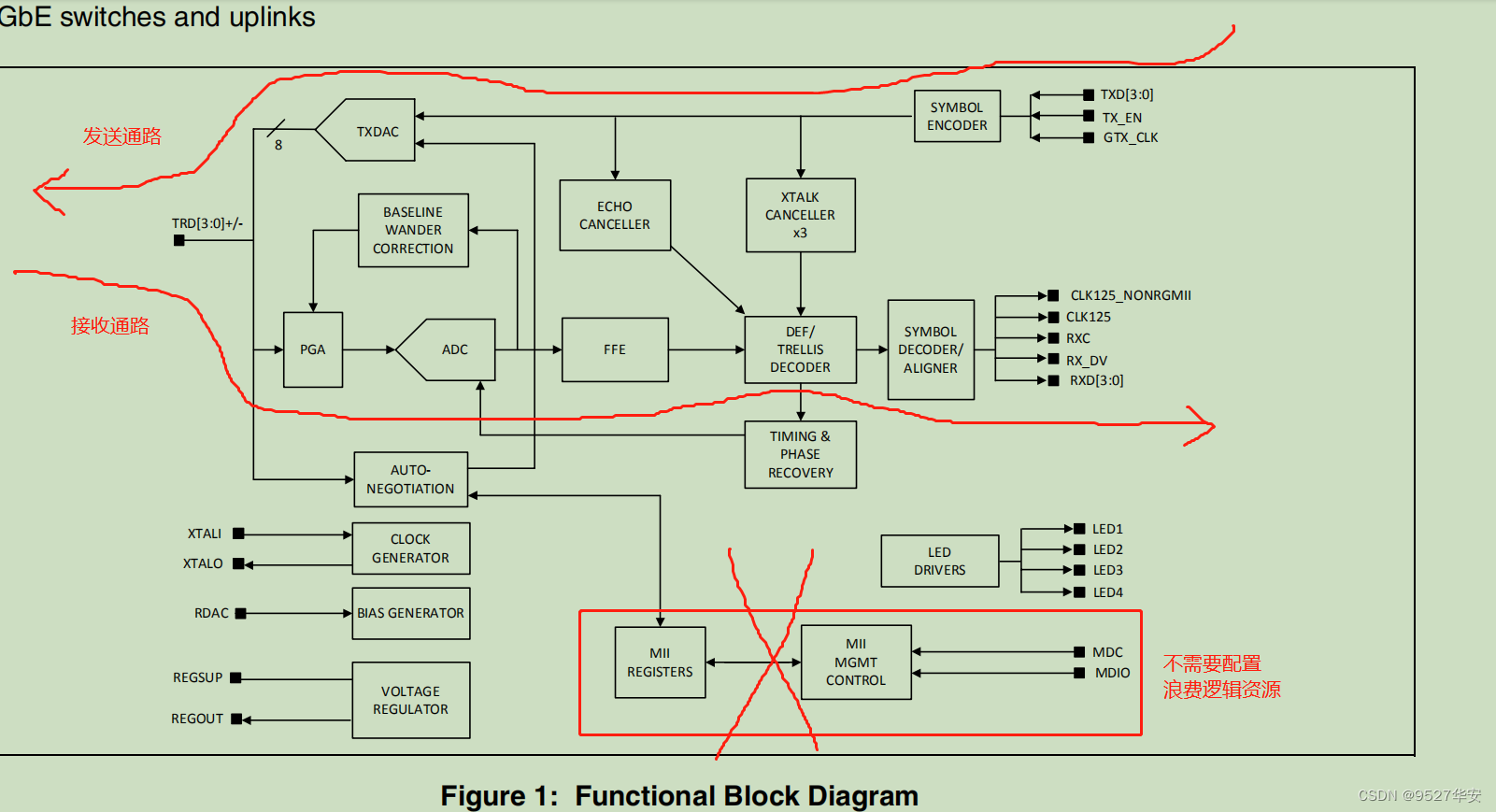

FPGA基于B50610实现UDP收发,纯verilog编写,带ping功能,提供工程源码和技术支持

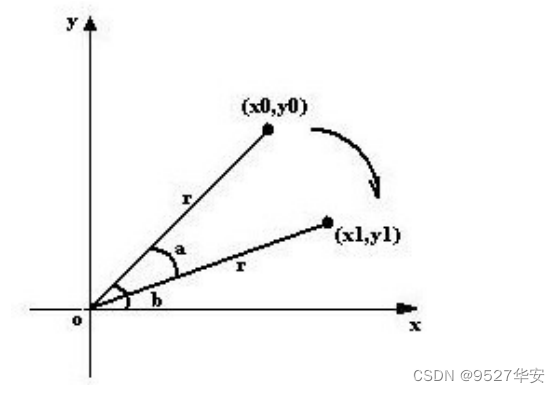

图像旋转是一种常用的图像处理技术,其基本原理就是指图像以某一点为中心旋转一定的角度,形成一幅新的图像的过程。当然这个点通常就是...

FPGA纯Verilog实现任意尺寸图像缩放,串口指令控制切换,贴近真实项目,提供工程源码和技术支持

不同分辨率的视频输出对应不同的时序和时钟,一般情况下是不存在同时或分时输出的,但现实项目中如果遇到这样的情况怎么办呢?很好办,...

图像任意位置显示指的是在显示屏上的显示,既然是任意位置显示,必须满足以下条件:1、要求显示的图像分辨率必须比显示背景的分辨率小,...

视频的字符叠加,简称OSD,是FPGA图像处理的基本操作,网上也有很多参考例程,但大多无法实现动态字符叠加,目前网上同行给出的方案有如...

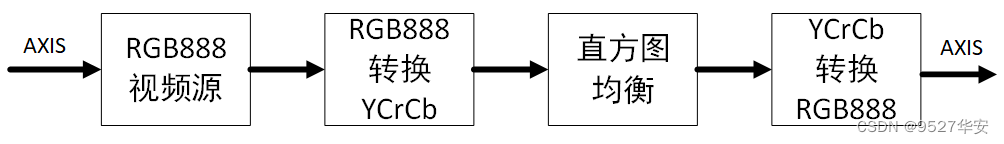

使用直方图均衡技术实现使用直方图均衡技术将原始图像的灰度直方图从比较集中的某个灰度区间变成在全部灰度范围内的均匀分布,是一种常...