终于来到了本系列的最后一篇。浮点操作通过异常标志来表示计算出现的不正常现象。软件可以通过这些异常了解浮点操作提供的结果是否可信。

在上一篇中,我们梳理了规范浮点数的计算规则。不过,浮点数不只有规范数一类编码,还包括NaN、无穷大和非规范数这样的特殊值。对于特殊值的处理,规则非常繁琐而且实现代价不小。对于Arm架构尤其如此,主要原因有两点:

IEEE-754标准中没有提供浮点运算的具体描述(伪代码)。标准中对于浮点运算过程的规定集中为下面这一句话:

舍入(Rounding)将无限精度的浮点数转换到某个特定的格式中,需要按照一定的规则在特定格式能够表示的浮点数中寻找与无限精度浮点数的近似。舍入时浮点数处理非常重要的属性,对于浮点数操作的结果影响明显。

在计算机体系架构中,实数的表示方式可以分为定点数和浮点数(整形可以归纳为定点数的一种)。定点数的所有比特都用来表示数值,其精度和范围由程序员定义。相同的二进制编码可能表示不同精度的数值,比如8比特定点数0x55(参见下图),即可能表示85(小数点在最低位右侧),可能表示3.4375(小数点在比特4右侧)。在使...

Ringbuffer(循环缓存)是软件中非常常用的数据结构之一, 在互联网应用、数据库应用等中使用广泛。处理器执行Ringbuffer的效率与其存储系统处理共享数据的性能息息相关。

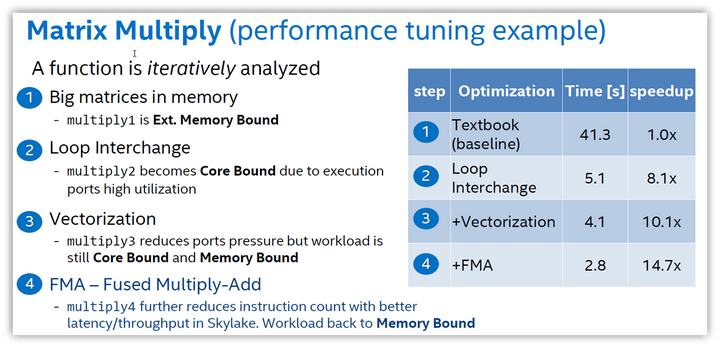

在Intel介绍top-down的演讲中,使用矩阵乘来演示用top-down方法来优化软件性能的过程,如下图所示。 本文尝试复现这个示例,并且提供更加细节的信息。需要声明的是,本文并不是一篇关于优化矩阵乘法程序的竞赛,重点在于展示利用Top-down分析优化软件性能的过程。 本文使用的测试平台是Intel Xeon Golden 5220,每颗芯片...

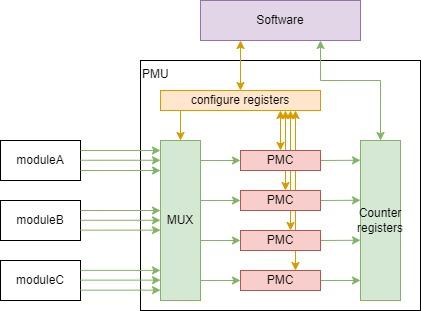

Top-down方法学由Intel提出,是一种软件性能分析技术。在众多软件性能分析技术中,Top-down使用了最多的硬件信息,与处理器微架构设计关系最为密切。目前,Top-down方法学已经成为服务器、桌面机领域进行软件性能分析的标准方法之一。

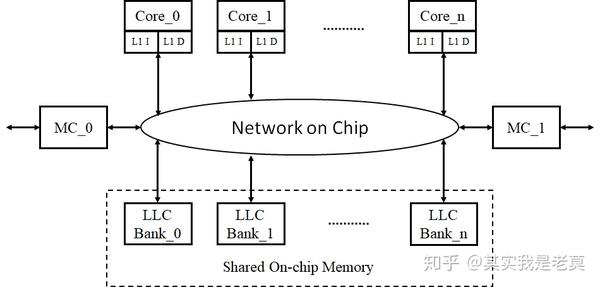

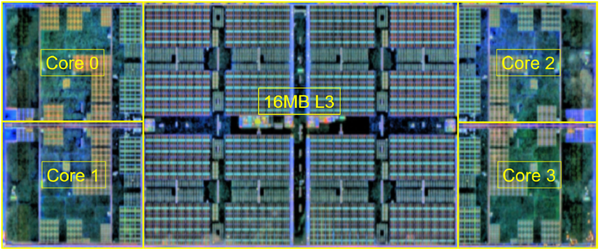

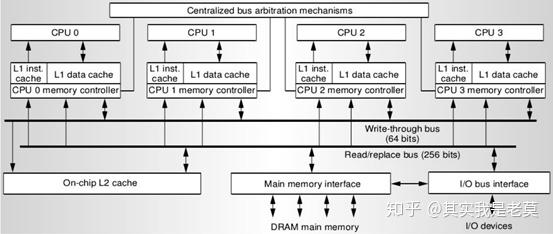

在第一部分我们已经阐述清楚了,片上多核系统分为CMP和MPSoC两种架构。CMP架构的特点是采用共享存储来交换数据,换言之就是每一个核心其实是可以“看见”完整的地址空间的。而MPSoC则更像是多个独立的子系统在单个芯片上的集成,一般是“按需设计”,多个系统之间的存储空间一般相互不可见。

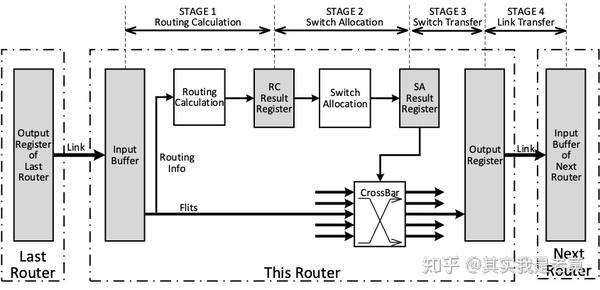

为了不拖更,现在也只能把原来比较宏伟的写作计划往简化了去搞。(此处应该有一配图,但是找不到那张图了所以先暂时空在这里)目的呢还是能尽快的把片上网络的相关内容都给大家过一遍。

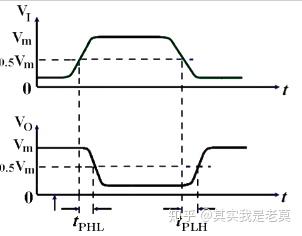

在网络模型中,物理层是信息传输的基础和载体,主要作用是实现信号在物理介质上的可靠传输。而要实现信号在物理介质上的可靠传输就涉及到了信号处理、编码原理、电子技术、电磁场与电磁波等多个领域的知识。这部分知识其实挺庞杂的,可以说通信工程这个专业四年大半时间都在搞懂这个问题。而剩下一小半时间则是在学习网...

ISSCC全称为IEEE International Solid-State Circuits Conference(国际固态电路会议),被誉为集成电路领域的"奥林匹克"。会上开放大量的很有价值的、经过实测的设计,供工业界和学术界参考使用。而工业界的踊跃参会更使得会议能够建立起工程研发和学术研究的桥梁。

系统级芯片也被称为片上系统,是指在单个芯片内部实现大部分甚至完整的电子系统功能的一种芯片。这种芯片是高端电子系统的核心,随着集成电路工艺技术的发展也逐步向中低端电子系统发展。如今,很多诸如腕表、手环之类的可穿戴设备以及智能玩具等低端嵌入式设备也都以系统级芯片为核心来开展设计。可以说片上系统已经成...

说的网络分层模型,想必现在但凡有点网络常识的学生都应该知道。多年来通信专业的教育给我留下的最深刻的烙印就是我可以对ISO提出的OSI七层模型倒背如流:从底层到上层依次是物理层、数据链路层、网络层、传输层、会话层、表示层、应用层。当然,正着也可以背下来:应用层、表示层、会话层、传输层、网络层、数据链路层...

深度模型压缩、加速、自动搜索。

腾讯AI,物联网等相关技术干货,欢迎关注

前瞻性的眼光,和持之以恒的学习~

安谋科技旗下首款AI产品周易NPU技术及应用公开课,技术干货等。如需咨询周易NPU合作,请邮件Eco-Partner@armchina.com。

Arm相关的技术博客,提供最新Arm技术干货,欢迎关注