PHY Interface For the PCI Express, SATA, and USB 3.1 Architectures

Version 4.3

©2007 - 2014 Intel Corporation—All rights reserved.

8 Sample Operational Sequences

本节描述了一些 PCIe、SATA 以及 USB 操作示例的时序图和过程(译注:其实只有 PCIe 的:)。本节涉及的时序图和过程都并非唯一或者必须的。

8.1 Active PM L0 to L0s and back to L0 – PCI Express Mode

这个例子中,PHY 在 MAC 控制下,对链路进行了主动电源管理(ASPM,Active State Power Management),从 L0 状态进入到 L0s 状态,随后重新回到 L0 状态。

当 MAC 或者更高层的逻辑想要将链路状态转移为 L0s 时,MAC 会发送一条电气空闲有序符号集(Electrical idle),使 PHY 发送逻辑转入空闲状态,并将 PHY 电源状态转移为 P0s。注意对于 16 或者 32 比特总线,MAC 需要始终在总线上对齐电气空闲有序符号集,使 COM 符号位于低字节位置(TxDataK[7:0])。

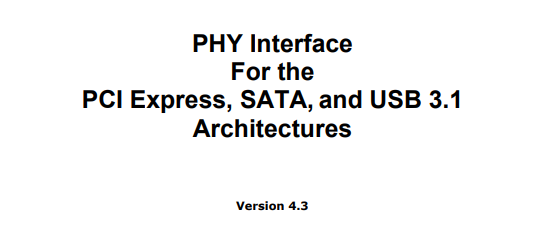

图 8-1-1 链路从 L0 进入 L0s 状态时序图

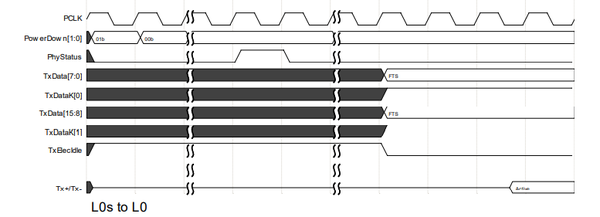

链路退出 L0s 状态的程序是这样的,MAC 将 PHY 从 P0s 状态转移为 P0 状态,等待 PHY 重新发送准备就绪后,(置起 PhyStatus),开始发送 FTS 序列(Fast Training Sequences)。注意,下图的 L0s 转为 L0 的状态图中,PHY 处于 2.5GT/s 速率。

图 8-1-2 链路从 L0s 进入 L0 状态时序图

8.2 Active PM L0 to L1 and back to L0 – PCI Express Mode

这个例子中,PHY 在 MAC 控制下,对链路进行了主动电源管理(ASPM,Active State Power Management),从 L0 状态进入到 L1 状态,随后重新回到 L0 状态。本例中的 PHY 属于 EP,(即面向上游端口连接),并且假设 EP 已经满足了 PCIe 协议中规定进入 L1 的所有条件。

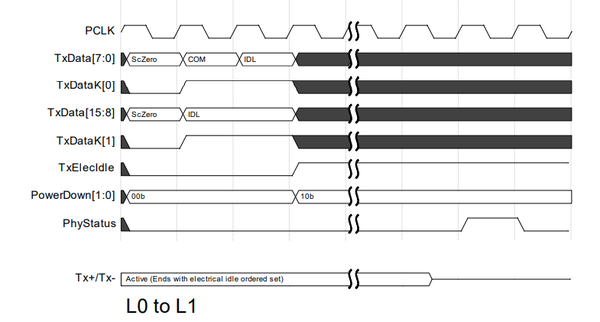

在 MAC 通过 PHY 发送 PM_Active_State_Request_L1 消息,并得到 PM_Request_ACK message 的回复后,MAC 和上例中一样,发送一条电气空闲有序符号集(Electrical idle),使 PHY 发送逻辑转入空闲状态,并将 PHY 电源状态转移为 P1。(译注:此处时序图相较上例而言,区别只是 PowerDown 将 00b 改为了 10b)

图 8-2-1 链路从 L0 进入 L1 状态时序图

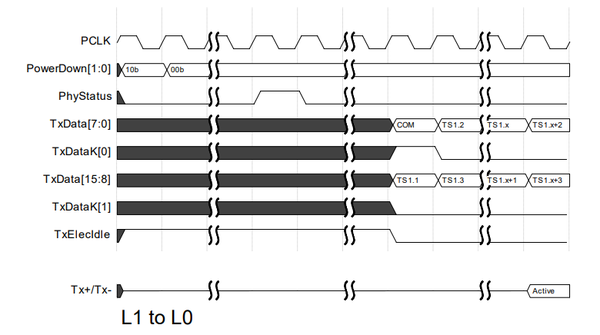

链路退出 L1 状态的程序是这样的,MAC 将 PHY 从 P1 状态转移为 P0 状态,等待 PHY 发送重新准备就绪后,(置起 PhyStatus),开始发送 TS1 (Training sequence)有序符号集。注意,下图的 L0s 转为 L0 的状态图中,PHY 处于 2.5GT/s 速率。(译注:此处和上例的区别主要在于 PHY 恢复 traffic 后发送的内容不同,从L0s 状态恢复时发送的是 FTS 序列。)

图 8-2-2 链路从 L1 进入 L0 状态时序图

8.3 Receivers and Electrical Idle – PCI Express Mode Example

本节中的示例只针对 2.5GT/s 速率的情况。注意,在 5.0 GT/s 或者 8 GT/s 速率时,RxElecIdle 信号对于 MAC 而言可能是不可靠的,MAC 需要根据 PCIe 3.0 或者 USB 3.0 协议中的相关内容提到的方法来检测 PHY 是否进入电气空闲状态。5.0 GT/s 速率下,可参阅第 6 章中的表 6-4 中的 RxElecIdle 定义。

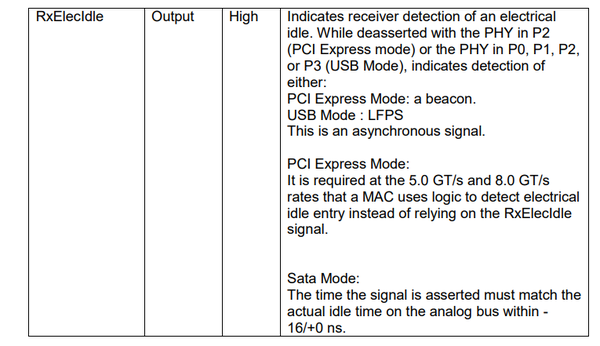

译注图 表 6-4 中的相关描述

本部分阐述了两个例子,分别涉及了从工作状态进入空闲状态,以及从空闲状态返回工作状态时,PIPE 接口的信号时序。在各传输情况中,RxElecIdle 信号和 RxValid 信号的跳变之间,可能存在很大的时间差。

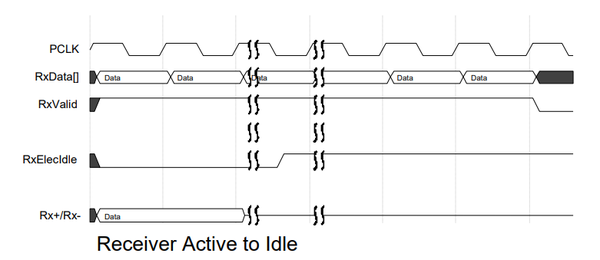

下图展示的是 PHY 从工作状态进入空闲状态时接口的响应。本例中,RxElecIdle 信号置高和 RxValid 信号置低和具体实现中弹性缓存的深度,以及符号同步逻辑的实现直接相关。注意,发送机在进入空闲状态的过程中可能会发送一些垃圾数据,这些垃圾数据会被传输到 RxData[] 信号线上,MAC 需要丢弃发送方进入电气空闲状态后,到本次 RxValid 信号置低期间,接收的任何数据。

图 8-3-1 接收机从工作状态进入空闲状态时序图

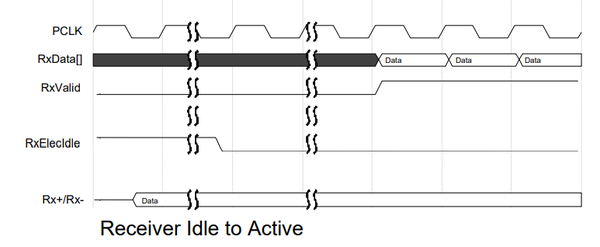

第二个例子是在接收机从空闲状态转回工作状态的接口响应。在本例中,RxElecIdle 信号置低(表示 Rx 差分信号线上开始有活动迹象),到 RxValid 信号置起之间存在一定时间间隔(表示 RxData[] 信号上出现有效数据)。这项延迟的大小取决于接收方重新训练的时间,以及弹性缓存的深度。

图 8-3-2 接收机从空闲状态重新进入工作状态时序图

8.4 Using CLKREQ# with PIPE – PCI Express Mode

CLKREQ# 用于下游设备请求上游设备关闭参考时钟的应用场景中。当 REFCLK 停止后,通常会导致 PIPE PHY 的输入时钟也同样停止。PCI Express CEM spec 允许下游设备在 L1 或者 L2 链路状态中停止 REFCLK。

关闭 REFCLK 的一般使用场景是,MAC 将 PHY 置于 P2 电源状态后,置低 CLKREQ#。重新打开 REFCLK 时,MAC 置高 CLKREQ# 信号,延时一段时间之后,延时的长短取决于 PHY 的具体实现,PHY 重新回到可用状态。

对于那些使用 CLKREQ# 来触发进一步电源管理措施的应用来说,PIPE 协议兼容 PHY 需要满足下述要求:

CLKREQ# in L1

当 MAC 将链路转移到 L1 状态,并且打算置低 CLKREQ# 以停止 REFCLK 时,在链路进入 L1 状态后,MAC 不是和通常一样将 PHY 转移为 P1 状态,而是直接将 PHY 转移为 P2 电源状态后,MAC 置低 CLKREQ# 信号。

之后,当 MAC 想重新使链路工作时,

- 置高 CLKREQ#

- 等待 REFCLK 稳定

- 等待 PHY 准备就绪

- 将 PHY 转移为 P0 状态后,重新开始链路训练

CLKREQ# in L2

当 MAC 将链路转移到 L2 状态,并且打算置低 CLKREQ# 以停止 REFCLK 时,在链路进入 L2 状态后,MAC 置低 CLKREQ# 信号。

之后,当 MAC 想重新使链路工作时,(译注:和 L1 时完全相同)

- 置高 CLKREQ#

- 等待 REFCLK 稳定

- 等待 PHY 准备就绪

- 将 PHY 转移为 P0 状态后,重新开始链路训练

Delayed CLKREQ# in L1

对于一条长时间空闲的 L1 链路,MAC 可能会希望停止其 REFCLK,这种情况下,PHY 本身处于 P1 状态,MAC 需要先将 PHY 转移为 P0 状态,再转移为 P2 状态,之后置低 CLKREQ# 信号。

使链路恢复的操作和先前的例子一致。

原文: Mindshare

译者: LJGibbs

文章来源:https://zhuanlan.zhihu.com/p/514542659

《PCI Express Technology 3.0》翻译系列

- PHY Interface 协议翻译:7.20 - 7.27

- PHY Interface 协议翻译:7.6 - 7.12

- PHY Interface :7 PIPE Operational Behavior 7.1-7.5

- PHY Interface :3 PHY/MAC interface & 4

- PHY Interface 协议翻译: 2 Introduction

- PCI Express Technology 3.0 Chapter 6 流量控制 5-7 节

- PCI Express Technology 3.0:Chapter 6 流量控制 1-4 节

- 《PCI Express Technology 3.0 》Chapter 5 第3 节

- 《PCI Express Technology 3.0》Chapter 5

- PCI Express Technology 3.0:Chapter 1 Background/背景

更多IC设计技术干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。