本系列专栏记载一些 Physical Design/STA 方面的知识,形式包括翻译、转载和原创。

对笔者个人而言,这是一个前端工程师的后端知识学习笔记。

本篇转载自 VLSI.pro https://vlsi.pro/useful-skew/ , 原作者: Sini Mukundan

译文

对于时钟树(clock tree)构建,传统的方法是采用零偏斜(Zero Skew)设计或者平衡偏斜(Balanced SKew)设计。即让每个时钟接收端(Sink)上的的插入延迟(Insertion Delay)保持相等,以便每个节点同时接收到时钟( 或者尽可能接近同时接收时钟 )。

这样一来,时钟路径的设计与数据路径的设计就完全独立了。首先确保时钟信号在允许的范围内到达每个触发器,如果数据路径也能在时钟信号的允许范围内满足时序要求,那么理论上时序就可以收敛。

然而,在一些大型设计中实现零偏斜可能代价高昂且不必要。而有意识地使用不平衡的时钟偏斜来满足一些时序路径,则称为 Useful Skew。

P&R 工具可以将 Useful Skew 用作 CTS (时钟数综合)和其他优化阶段的选项,利用时钟信号的偏斜,以可接受的裕量(Margin)减少来满足设计整体时序收敛。

让我们首先看一个通过时钟偏斜来满足时序的示例。

示例

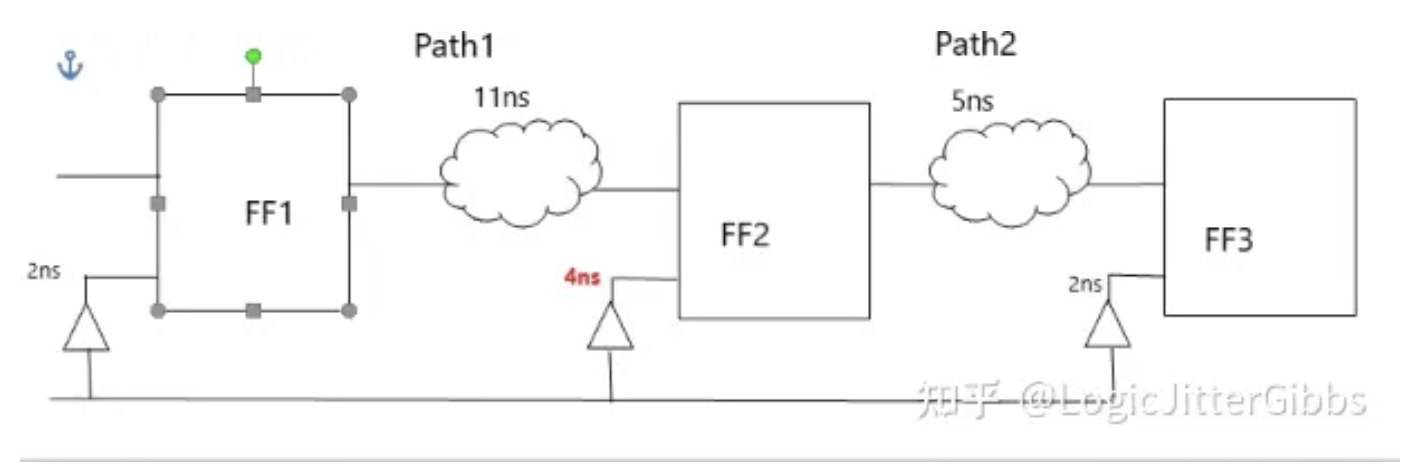

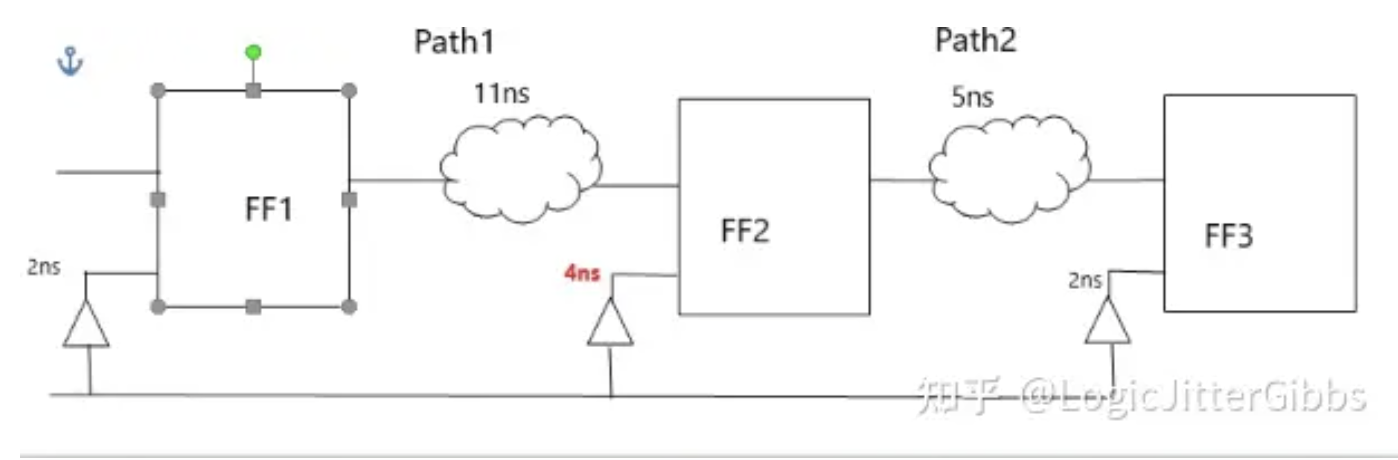

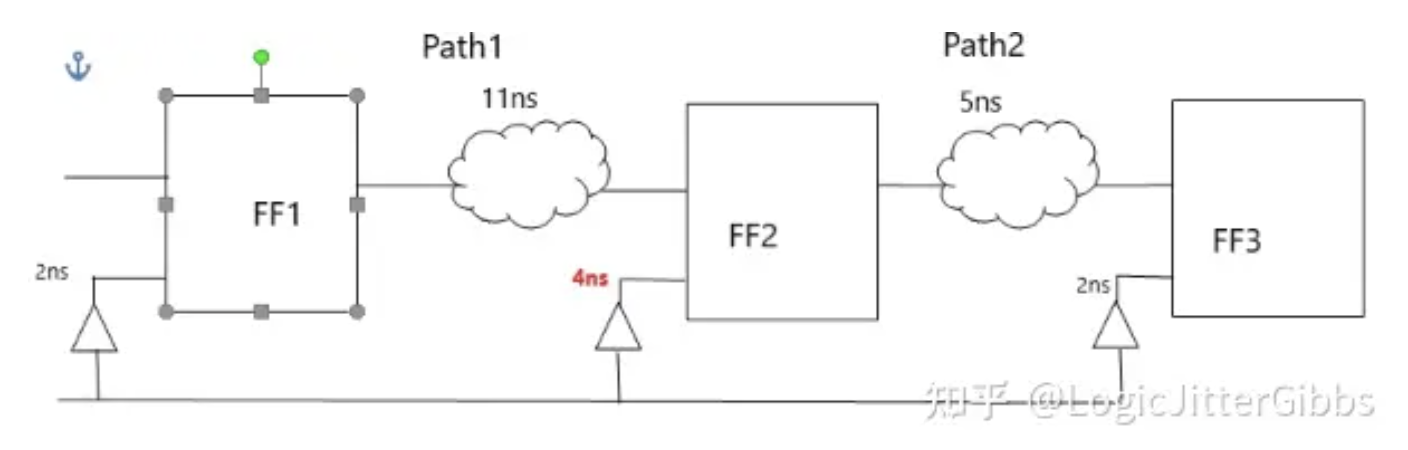

图中是一个时钟零偏斜,但是路径上存在 Setup 时序违例的示例设计。

假设电路的时钟周期为10ns,每个触发器的时钟引脚插入延迟为2ns。在此示例中,我们还假设 flops 的建立和保持时间为零。路径 1 的组合逻辑延迟为 11ns,路径 2 的组合逻辑延迟为 5ns。

路径1的建立时序要求为:

2ns(时钟路径延迟到 FF1/CP)+ 11ns < 2ns(时钟路径延迟到 FF2/CP)+10ns(时钟周期)13ns < 12 ns--> 时序违例

如果我们决定保持时钟网络不变,我们需要通过减少路径 1 的组合路径延迟来修复这个时序违例。然而,路径 2 的时序裕量实际上相当充足。 2ns+5ns < 2ns+10ns --> 时序裕量充足

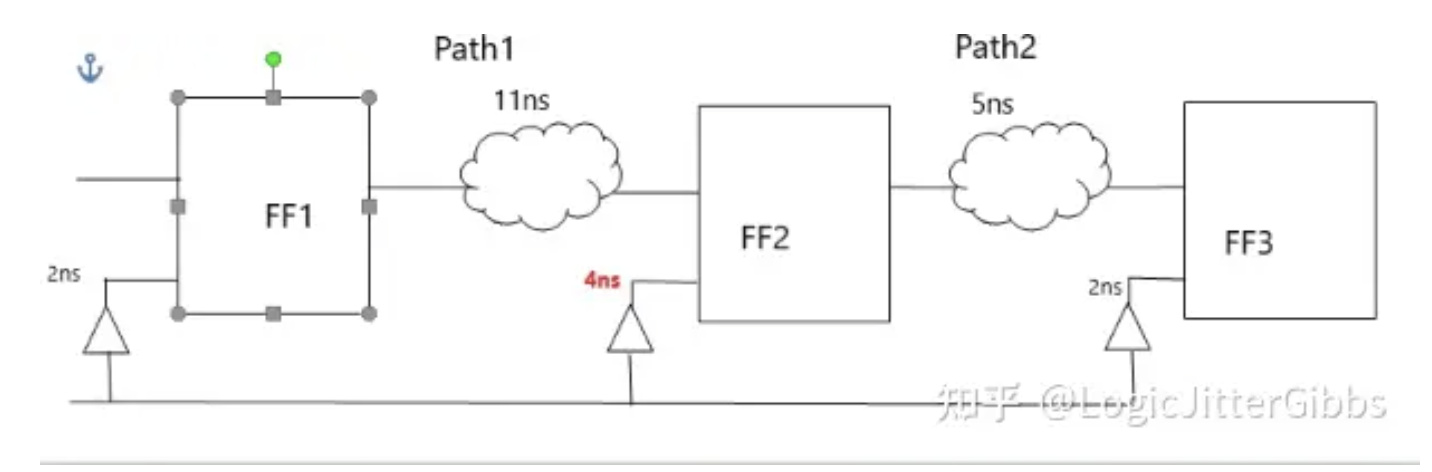

因此,理想情况下,我们可以从路径 2 借用一些周期时间,但前提是其他路径不受影响。让我们有意在 FF2 上引入一些时钟偏斜来实现这一点。此时 FF2 的时钟插入延迟从 2ns 变成了 4ns。

现在的建立时序要求是:

2ns(时钟路径延迟到 FF1/CP)+ 11ns < 4ns(时钟路径延迟到 FF2/CP)+ 10ns(时钟周期)

13ns < 14ns--> 时序收敛

然而,现在这两个触发器之间存在 2ns 的时钟偏斜,因此路径2的时序也发生了变化:

4ns(时钟路径延迟到 FF2/CP)+ 5ns < 2ns + 10ns

9ns < 12ns--> 仍然没有违例,尽管现在的裕量变小了。

当启用 “ Useful Skew” 时,PnR 工具可以改变时钟网络并引入有意的时钟偏斜,以较小的代价满足时序要求。在Innovus 工具中,相关实用命令包括:

setOptMode –usefulSkew false

setOptMode -usefulSkew true -usefulSkewPreCTS true

setOptMode -usefulSkew true -usefulSkewPostCTS true申明:本文由文心一言翻译,笔者在其译文的基础上调整润色。

用 AI 翻译

已经提前告诉 AI 翻译文章的领域是集成电路物理设计。

但是翻译质量也一般,大部分内容需要笔者调整,比如

- 基础专有名字翻译错误,比如 setup timing 翻译为建立时序,timing closed 翻译为关闭设计等等

- 没有合适翻译的专有名词硬翻,比如 useful skew 翻译为 有用的偏斜,是这个意思没错,但其实可以不翻。

- 原文作者描述感觉还是比较口语化,翻译出来的中文语感很一般,比如作者用 here 表示语气词,AI 就一定会加上 ‘这里’。

这里 AI 相当于帮忙做了点辅助工作。从技术的角度来看,AI 翻译技术文章的能力应该是可观的,笔者后续还会继续在这方面做一些探索。比如尝试给 AI 更多上下文提示/试试别家 AI 比如 ChatGPT 等。

原文

For clock trees, the traditional way is to go with zero skew or balanced skew. For each of the sinks, the insertion delay is kept to be equal so that each node receives the clock at the same time(or as close as physically possible). Here, your clock design is completely independent of your data path design. You are ensuring the clock signals come to each data sync point within a permissible variation, and the design can theoretically be timing closed if the data paths also can meet the timing within a permissible range of the clock signal.

However, meeting zero skew in some large designs can be unnecessarily costly. If clock skew is used intentionally to meet timing then it is called useful skew. P&R tools can use useful skew as an optimization option in CTS and other stage optimizations to leverage the clock signal in meeting timing, with acceptable margins.

Let us first see an example of clock being skewed to meet timing.

Given below is a design with zero skew, but setup timing violation.

Let’s take the clock period of the circuit as 10ns, with 2ns insertion to delay to clock pin of each register. Let’s also assume that the setup and hold times of the flops are zero for this example. The path1 combinational delay is 11ns and path2 combinational delay is 5ns.

The setup timing requirement of path 1 is:

2ns(clock path delay till FF1/CP) + 11ns < 2ns(clock path delay till FF2/CP)+10ns(clock period)

13ns < 12 ns--> Timing Violation

If we decide to keep the clock network intact, we need to fix this timing violation by reducing the combinational path delay of Path1. However, path2 timing is met with considerable margin. 2ns+5ns < 2ns+10ns So, ideally we could borrow some cycle time from path2, if no other paths are affected by it. Let’s introduce some clock skew to do just that.

Now the setup timing requirement is 2ns(clock path delay till FF1/CP) + 11ns < 4ns(clock path delay till FF2/CP)+10ns(clock period)

13ns < 14ns --> PassHowever, now there is a clock skew of 2ns between these registers, and the Path2 timing has now changed to:

4ns(clock path delay till FF2/CP)+5ns < 2ns+10ns

9ns < 12ns–-> Still not violated, even though margin is now less.

PnR tools when enabled ‘useful skew’ can change the clock network and introduce intentional skew to meet timing with smaller cost. Some of the useful commands in Innovus tool are:

- setOptMode –usefulSkew false

- setOptMode -usefulSkew true -usefulSkewPreCTS true

- setOptMode -usefulSkew true -usefulSkewPostCTS true

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- DDR 学习时间 (Part C - 3): DFI PHY 与 DFI 时钟频率比

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

- JESD79-4 第4章 SDRAM命令描述与操作(4.20-4.23)

- JESD79-4 第4章 SDRAM命令描述与操作(4.17-4.19)

- JESD79-4 第4章 SDRAM命令描述与操作(4.14-4.16)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。