本系列专栏记载一些 Physical Design/STA 方面的知识,形式包括翻译、转载和原创。

对笔者个人而言,这是一个前端工程师的后端知识学习笔记。

本篇转载自 VLSI.pro https://vlsi.pro/minimum-pulse-width-check/ , 原作者: Sini Mukundan

译文

Minimum Pulse Width 最小脉冲宽度检查是为了确保时钟信号的脉冲宽度足够宽,使 cell 内部操作能够完成。也就是说,为了获得 cell 上稳定的输出,你需要确保在触发器的时钟引脚上的时钟信号至少具有某个 “最小” 的宽度。

这个术语的正式定义如下,它是信号上升沿穿越 VDD 的 50% ,到信号下降沿穿越 VDD 的 50% 之间的间隔。如果谈论低电平信号,则是信号下降沿穿越 VDD 的 50% 到信号上升沿穿越 VDD 的 50% 之间的间隔。

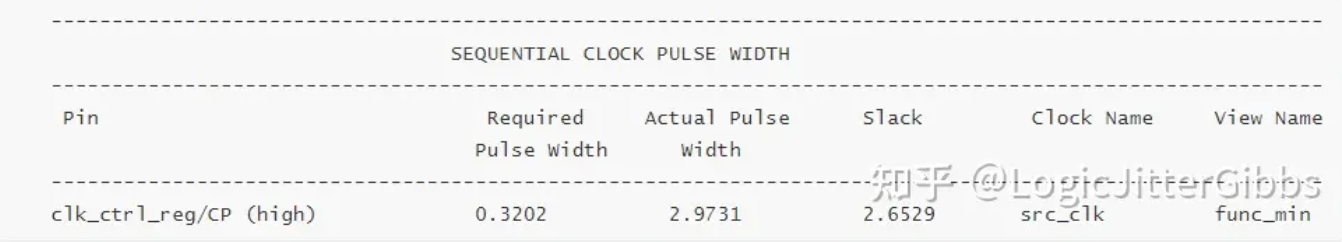

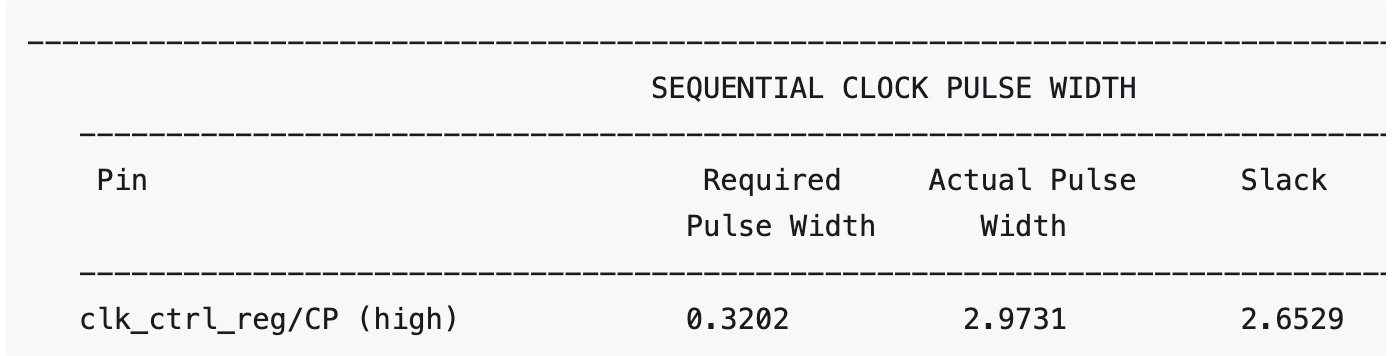

从下方这个报告中可以看到,输入引脚 transition 或 skew 会影响其电路任意点的实际脉冲宽度。这就是为什么我们在创建时钟树时使用特殊的 CTS cell 而不是普通 buffer 的原因。

在ETS,或 Cadence 最新的(译注:当时为 2015 年) STA 工具 TEMPUS 中,你会看到这样的报告:

在这个例子中,时钟周期为 6ns,占空比为 50%。即在此处,clk_ctrl_reg/CP 上的时钟信号应该至少保持高电平 0.3202ns(请注意,TEMPUS 中的默认时间单位是ps)。实际信号保持高电平 2.9731ns。因此,在 src_clk 的 CP 引脚上没有最小脉冲宽度违规。

约束设计

现在,让我们看看如何为设计指定最小脉宽约束。

1.使用.lib文件

最小脉冲宽度取决于工艺节点和标准单元库设计。 .lib 文件中的内容是对指定工艺节点的标准 cell 特性的建模。在 .lib 文件中查找 timing_type : min_pulse_width;。这项属性定义了 flop的时钟、复位和置位引脚,或 latch 的使能引脚的最小脉宽。

示例 .lib 文件中的约束定义:

pin (CP) {

clock : true;

direction : input;

max_transition : 2.5;

capacitance : 0.00774191;

timing () {

related_pin : "CP";

timing_type : min_pulse_width;

rise_constraint (mpw_constraint) {

index_1 ("0.1, 0.6, 1.3, 1.9, 2.5");

values ("0.131, 0.800, 1.596, 2.392, 3.066");

}

fall_constraint (mpw_constraint) {

index_1 ("0.1, 0.6, 1.3, 1.9, 2.5");

values ( "0.361, 0.800, 1.596, 2.392, 3.066" );

}

}index_1 代表 CP 引脚的 transition,表中的最后一个值是该引脚的 max_transition。values表示指定的引脚 transition 的最小脉冲宽度值。

2.SDC命令 set_min_pulse_width

为了设置特定的最小脉冲宽度约束,您可以使用命令 set_min_pulse_width。

示例SDC文件中的约束定义:

set_min_pulse_width -high 3.0 [all_clocks]

set_min_pulse_width -low 2.0 [all_clocks]如果既没有指定高电平也没有指定低电平,则该约束适用于高电平和低电平信号。

报告违规

在大多数STA工具中,您可以使用 report_timing 或类似的命令来报告违规情况。

report_timing -check_type pulse_width您还可以使用TEMPUS中的 report_min_pulse_width 命令来报告脉冲宽度值。

申明:本文由文心一言翻译,笔者在其译文的基础上调整润色。

原文

Minimum pulse width checks are done to ensure that width of the clock signal is wide enough for the cell’s internal operations to complete. i.e. to get a stable output you need to ensure that the clock signal at the clock pin of the flop is at least of a certain ‘minimum’ width.

If you need a formal definition of the term, it is the interval between the rising edge of the signal crossing 50% of VDD and the falling edge of the signal crossing 50% of VDD. If talking in terms of low signals, it is the the interval between falling edge of the signal crossing 50% of VDD and the rising edge of signal crossing 50% of VDD. Now you can see how the input pin transition or slew will affect the actual pulse width at any point. This is the reason why we use special CTS cells instead of regular buffers while creating a clock tree.

In ETS(or TEMPUS as the newest Cadence tool for STA is called), you will see a report like this:

In this example, the clock period is 6ns with a duty cycle of 50%.i.e. Here, the clock signal at clk_ctrl_reg/CP should be high at least for 0.3202ns (please note that the default time unit is ps in TEMPUS). The actual signal is high for 2.9731ns. Hence there is no minimum pulse width violation at the CP pin for src_clk.

Constraining the design

Now, let us see how you can specify this constraint for your design.

1.Using .lib fileMinimum pulse width depends on the technology node and the standard cell library design. You will have these modeled in your .lib file. Look for timing_type : min_pulse_width; in your liberty file. These will be defined for clock, reset and preset pins of a flop, or the enable pin of a latch.

pin (CP) {

clock : true;

direction : input;

max_transition : 2.5;

capacitance : 0.00774191;

timing () {

related_pin : "CP";

timing_type : min_pulse_width;

rise_constraint (mpw_constraint) {

index_1 ("0.1, 0.6, 1.3, 1.9, 2.5");

values ("0.131, 0.800, 1.596, 2.392, 3.066");

}

fall_constraint (mpw_constraint) {

index_1 ("0.1, 0.6, 1.3, 1.9, 2.5");

values ( "0.361, 0.800, 1.596, 2.392, 3.066" );

}

}The index_1 is the transition at pin CP, and the last value in the table is the max_transition of the pin. The values denote the minimum pulse width values for the pin transition specified.

SDC command ‘set_min_pulse_width’

To specifically set the minimum pulse width constraint, you can use the command set_min_pulse_width

set_min_pulse_width -high 3.0 [all_clocks]

set_min_pulse_width -low 2.0 [all_clocks]

If neither high now low is specified the constraint applies to both high and low signal levels.

Reporting the violations

You can use in majority of STA tool, report_timing or a similar command.

report_timing -check_type pulse_widthYou can also use the command report_min_pulse_width in TEMPUS to report the pulse width values.

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- [[译文] 芯片设计后端知识笔记: Useful Skew 介绍](https://aijishu.com/a/1060000...)

- DDR 学习时间 (Part C - 3): DFI PHY 与 DFI 时钟频率比

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

- JESD79-4 第4章 SDRAM命令描述与操作(4.20-4.23)

- JESD79-4 第4章 SDRAM命令描述与操作(4.17-4.19)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。