本期我们学习美光的一篇文章,关于低功耗 DDR,即 LPDDR 和标准 DDR 的对比介绍,本文是对这篇文章粗略翻译。

这篇文章中的 DDR 和 LPDDR 指的都是第一代 DDR/LPDDR,时代有点久远(2007),和目前主流的 LPDDR4/5 和 DDR4/5 有显著不同。但是对理解 LPDDRx 和 DDRx 的区别还是有些参考意义。读者可以按需阅读。

原文链接:TN-46-15

原文是美光 DDR Technology Note (TN) 系列文章中的一篇,写的比较详尽又比较好懂,大家可以看下这系列的文章。美光 DDR4 TN

申明:本文由网易有道速读翻译,笔者在其译文的基础上调整润色。

0 引言

这篇 Technology Note 概述了低功耗 DDR (LPDDR) SDRAM 与标准 DDR SDRAM 在初始化和时钟方面的差异,以及低功耗 DDR SDRAM 所独有的一些特性,包括温度补偿自刷新 ( TCSR, temperature-compensated self refresh )、部分阵列自刷新 ( PASR, partial-array self refresh )、深度省电模式 ( DPD, deep power-down) 和时钟停止模式(Clock stop mode)等。

设计混合使用低功耗 DDR SDRAM 或标准 DDR SDRAM 的系统是一种常见的做法。了解两种类型的 DDR SDRAM 存储设备之间的功能和体系结构差异可以帮助设计者更好地设计这些系统。

1 低功耗和标准 DDR SDRAM 的区别

以下是低功耗 DDR SDRAM与标准 DDR SDRAM器件之间的功能和架构差异列表:

- 初始化 // Initialization

- 输入/输出 // input/output

- 时钟 ( CAS延迟 ) // Clocking (CAS latency)

1.1 初始化

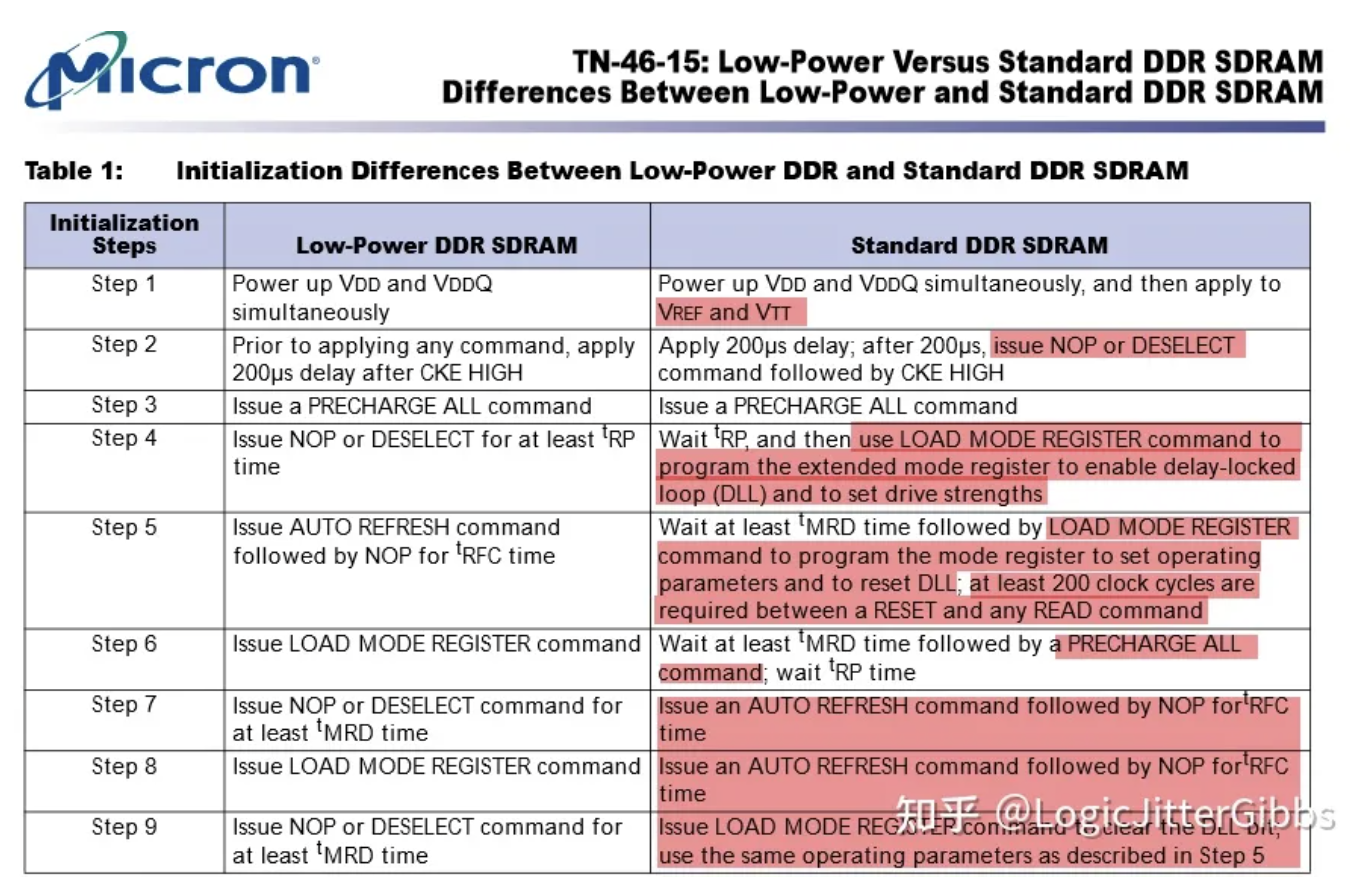

下表是两者初始化过程的比较,高亮了两者之间的明显区别

LPDDR 初始化步骤

- 同时给 VDD 和 VDDQ 供电。

- 在发送任何命令之前,在 CKE 为高电平后延迟 200 微秒。

- 发送 PRECHARGE ALL 命令。

- 延迟至少 tRP 时间,然后使用发送 NOP 或者 DESELECT 命令。

- 发送 AUTO REFRESH 命令,然后延迟至少 tRFC 时间后发送 NOP 命令。

- 发送 LOAD MODE REGISTER 命令。

- 延迟至少 tMRD 时间,然后发送 NOP 或 DESELECT 命令。

- 发送 LOAD MODE REGISTER 命令。

- 延迟至少 tMRD 时间,然后发送 NOP 或 DESELECT 命令。

标准 DDR 初始化步骤

- 同时给 VDD 和 VDDQ 供电,然后再给 VREF 和 VTT 供电。

- 延迟 200 微秒后, CKE 置为高电平,发送 NOP 或 DESELECT 命令。

- 发送 PRECHARGE ALL 命令。

- 延迟 tRP 时间后,使用 LOAD MODE REGISTER 命令来设置扩展模式寄存器,以启用延迟锁定环路(DLL)和设置驱动强度。

- 延迟至少 tMRD 时间后,使用 LOAD MODE REGISTER 命令来配置模式寄存器中的运行参数和 reset DLL;在 RESET 命令和任意读命令之间需要至少 200 个时钟周期。

- 等待至少 tMRD,发送 PRECHARGE ALL 命令;等待 tRP。

- 发送 AUTO REFRESH 命令,然后延迟至少 tRFC 时间,发送 NOP 命令。

- 发送 AUTO REFRESH 命令,然后延迟至少 tRFC 时间,发送 NOP 命令。

- 使用 LOAD MODE REGISTER 命令来设置扩展模式寄存器,以清除 DLL reset bit,保持第五步中设置的运行参数。

尽管低功耗 DDR SDRAM 和标准 DDR SDRAM 的初始化步骤看起来是相同的,但是在设计混合系统时应该考虑到一些差异,比如命令序列。

低功耗 DDR SDRAM 和标准 DDR SDRAM 同时为 VDD 和 VDDQ 供电,但标准 DDR SDRAM 还需要系统为 VREF 和 VTT 供电。

两种形式的 DDR SDRAM 之间的另一个区别是使用 LOAD MODE REGISTER 命令的方式。在标准 DDR SDRAM中,LOAD MODE REGISTER 命令用于设置延迟锁定环(DLL)以及其他参数,如驱动强度。

发送 LOAD MODE REGISTER 命令的顺序也存在差异。例如,在标准 DDR SDRAM 中,LOAD MODE REGISTER 命令在 PRECHARGE 命令之后发出; 然而在低功耗 DDR SDRAM 中,LOAD MODE REGISTER 命令是在发出 PRECHARGE,和 AUTO REFRESH 之后。

输入/输出

LPDDR 的 LVCMOS 接口的实现非常简单,并且直流功耗非常小。LVCMOS 能够提供稳定的高低电平信号; 然而,由于其阈值电压的不确定性,输入/输出缓冲器需要更高的电压摆幅来确保可靠的开关。译注:LPDDR IO 电压为 1.8V,兼容 LVCMOS。

DDR SDRAM 采用 JEDEC 标准 2.5V (SSTL_2 兼容) 输入和输出。SSTL_2 接口的优点包括对称的高低电平电压值、改进的信号完整性和更好的抗噪声能力。此外,SSTL_2 假定传输线具有 termination。对高速信号而言,termination 是很重要的,以减少反射,噪声和增加时间裕度。由于标准 DDR SDRAM 的运行速度比低功耗 DDR SDRAM 高,因此使用 SSTL_2 接口作为标准 DDR SDRAM 的输入和输出是合乎逻辑的。

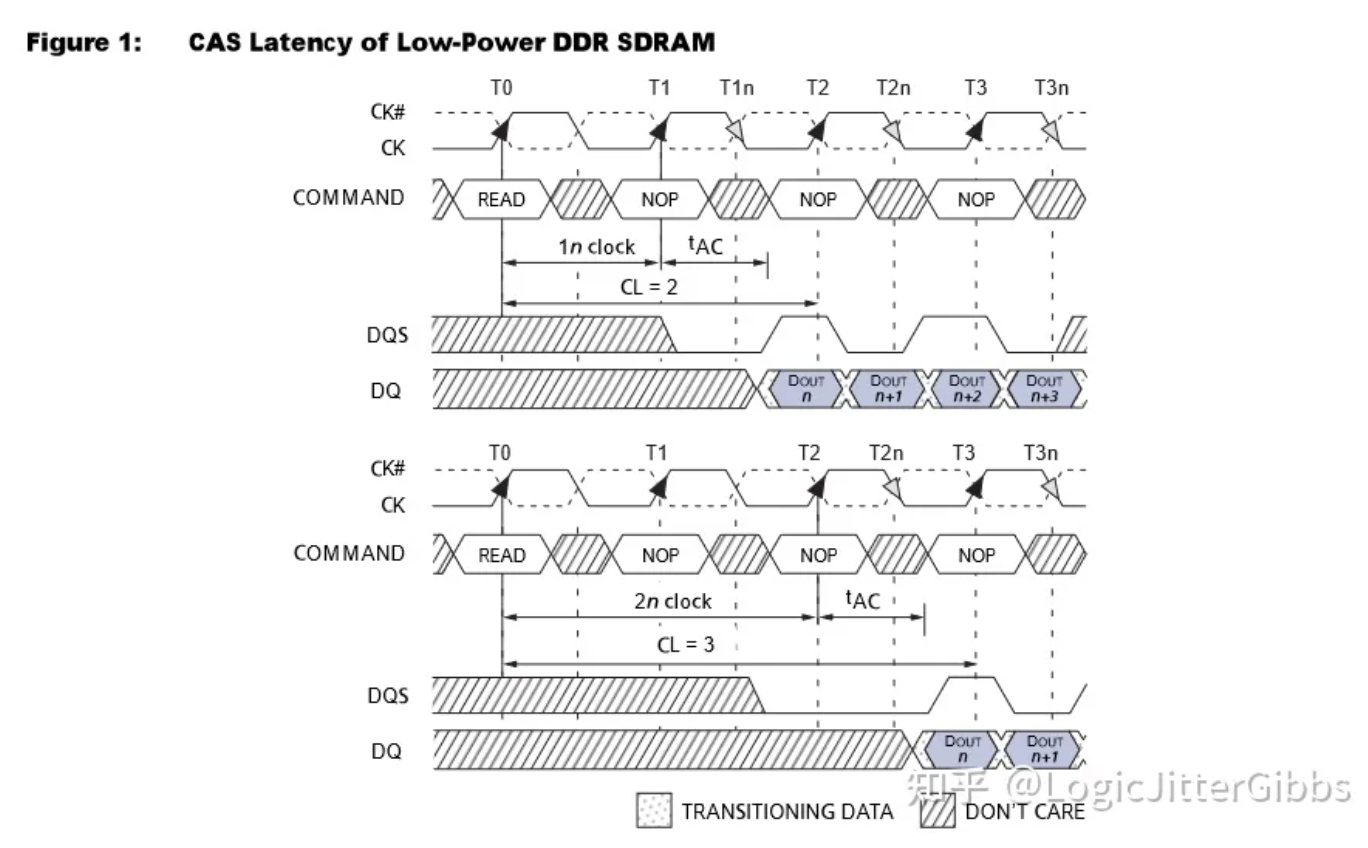

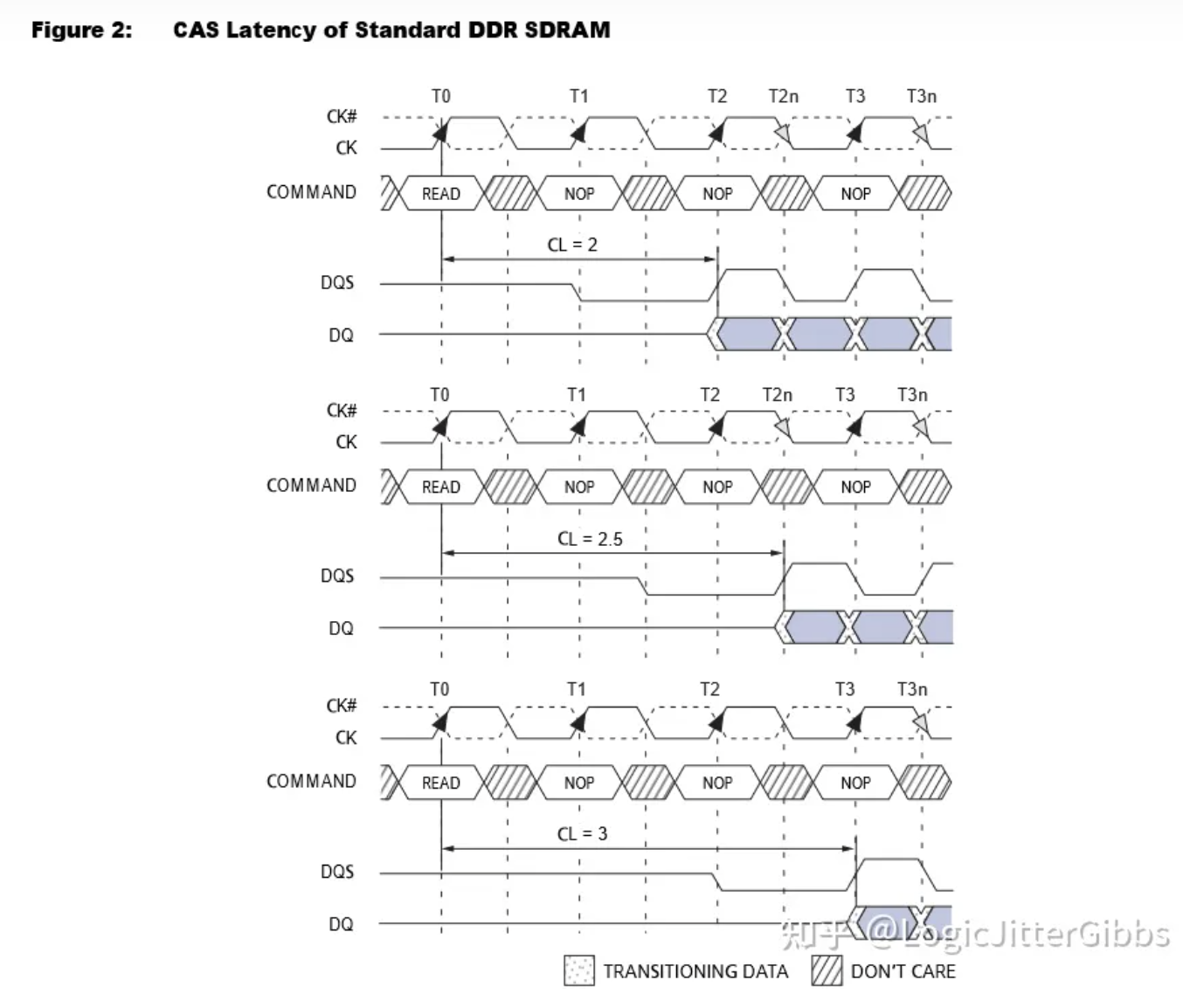

数据驱动时钟沿差异

标准 DDR SDRAM 内部使用延迟锁定环路(DLL)电路,将数据与时钟边缘对齐; 然而,由于低功耗 DDR SDRAM 受功耗限制,移除了 DLL 电路。因此,低功耗 DDR SDRAM 的数据在 CLK 上升沿发送并经过 tAC 时延后到达。这导致有可能有效数据比时钟上升沿先到达,如原文第 3 页上的图 1 所示。图 1 和原文第 4 页上的图 2 对比显示了低功耗 DDR SDRAM 和标准 DDR SDRAM 之间的数据时钟差异。 由于没有 DLL 电路,JEDEC 没有在低功耗 DDR SDRAM 协议中规定时钟抖动(clock jitter)参数。但是,有些场景下可以通过计算得到时钟抖动参数。例如,对于 tCK 为 7.5ns 的情况,假设占空比为 50% ( tCL = 3.0ns, tCH = 3.0ns),可接受的上升沿或下降沿时钟抖动计算如下:

时钟抖动 = tCK - tCL - tCH

时钟抖动 = 7.5ns - 3ns - 3ns = 1.5ns

低功耗 DDR SDRAM 独有特性

低功耗DDR SDRAM具有以下特性:

- 温度补偿自刷新 (TCSR)

- 部分阵列自我刷新 (PASR)

- 深度省电 (DPD)

- 时钟停止模式

温度补偿自刷新

低功耗 DDR SDRAM 采用片上温度传感器采样器件温度,根据器件温度控制刷新间隔。更新 JEDEC 标准中规定的 TCSR 位不会对设备产生影响。片上自刷新振荡器将继续根据当前器件温度,以出厂时设定优化的温度-速率刷新阵列。TCSR 仅适用于自刷新(Self-refresh)模式,不适用于自动刷新(Auto refresh)模式。

部分阵列自刷新

为了节约功耗,PASR 功能使控制器能够选择自刷新期间刷新的内存量。可选的刷新选项包括:

- 完整阵列:Bank 0,1,2 和 3

- 半阵列: Bank 0 和 1

- 四分之一阵列: Bank 0

- 八分之一阵列: Bank 0,行地址MSB = 0

- 十六分之一数组: Bank 0,行地址 MSB 和 MSB-1 都等于零

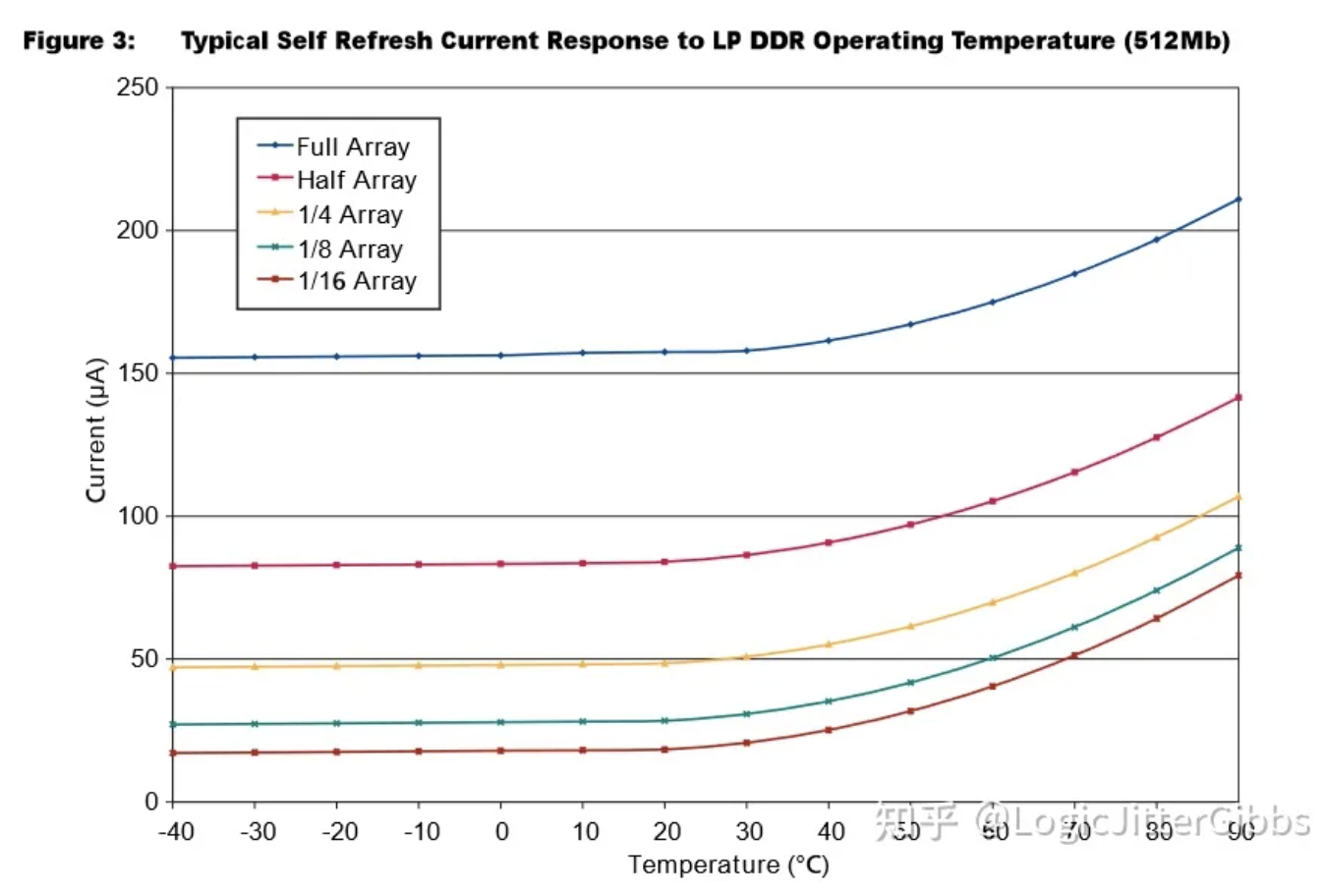

图 3 显示了不同 PASR 配置下的自刷新模式消耗的电流。

可以看到 PASR 可以减少自刷新期间的电流消耗。图中随着温度升高消耗的电流增多,这是因为温度升高后,自刷新间隔变短。

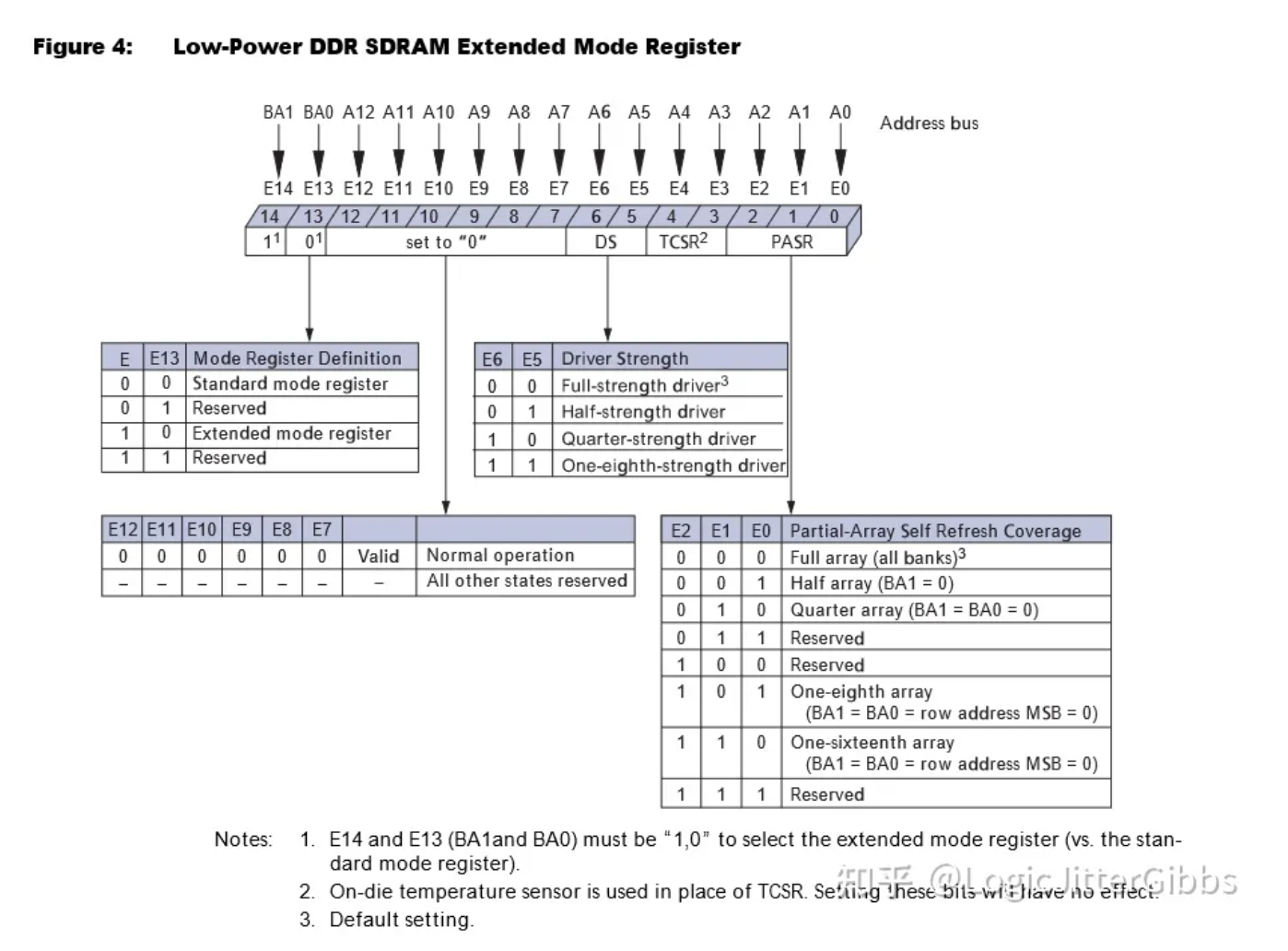

通过如图 4 所示模式寄存器的 Bit 2-0,可以配置 PASR 选项。根据所选的PASR选项,未刷新的阵列部分将不会保留数据,内存控制器只能访问所选的阵列部分。

深度省电模式

低功耗 DDR SDRAM 提供深度断电 (DPD) 功能,可以有效地降低阵列的功耗并降低漏电流。不需要保留 DDR 数据的应用程序可以在保持系统电源的情况下使能 DPD 。设备进入DPD模式后,将不再保留数据。

在进入 DPD 模式之前,所有 Bank 都必须处于空闲状态,数据总线上没有活动 (必须满足 tRP 时间)。此模式是通过保持 CS# 和 WE# 低,RAS 和 CAS 在时钟上升沿为高,而 CKE 为低。CKE必须保持低电平以维持 DPD 模式。

时钟必须在退出 DPD 模式之前保持稳定。通过在命令总线上使用 NOP 或 DESELECT 命令置高 CKE 来退出 DPD 模式。在退出 DPD 模式时,需要提供给 DRAM 200µs 的有效时钟,同时命令总线上存在 NOP 或 DESELCT 命令。之后还需要发送一个 PRECHARGE ALL 命令和重新进行一个完整的 DRAM 初始化序列。

时钟停止模式

时钟停止模式功能可以节省应用程序的功耗,因为时钟翻转率减少了。通过以下任何一种方法,都可以节省功耗:

- 当数据传输需要不同速率时,更改时钟频率

- 在时钟停止模式期间保持 CKE 高,CK 和 CK# 分别保持低电平和高电平

低功耗 DDR SDRAM 使时钟能够在工作期间改变频率,但只有在满足所有时序参数和所有刷新需求的情况下。

如果没有正在进行的数据访问 (无论是写还是读操作),时钟可以完全停止; 如果有正在进行 WRITE 或 READ 操作,那么在停止时钟之前,必须确保整个 Burst 的数据通过了所有数据路径。在时钟停止模式内,在时钟停止模式期间保持 CKE 高,CK 和 CK# 分别保持低电平和高电平 。在重新启动时钟后,在发出有效命令之前,需要等待一个时钟周期和发送至少一个 NOP 命令。

结论

本技术说明概述了低功耗 DDR SDRAM 和标准 DDR SDRAM 存储设备之间的时钟和初始化差异。 此外,本技术说明解释了以下在标准DDR SDRAM 中没有的低功耗 DDR SDRAM 功能:

- 温度补偿自刷新 (TCSR)

- 部分阵列自我刷新 (PASR)

- 深度省电 (DPD)

- 时钟停止模式

只要在软件中考虑了初始化和时钟差异,DDR SDRAM 控制器也能够驱动使用相同硬件接口的低功耗 DDR SDRAM设备。

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

- 【译文】 芯片设计后端知识笔记: Minimum Pulse Width 检查

- 【译文】芯片设计后端知识笔记: Useful Skew 介绍

- DDR 学习时间 (Part C - 3): DFI PHY 与 DFI 时钟频率比

- JESD79-4 第4章 SDRAM命令描述与操作(4.24)

- JESD79-4 第4章 SDRAM命令描述与操作(4.20-4.23)

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。