本文介绍了 Armv8-A 中的内存模型。 它首先解释描述内存的属性来自哪里以及它们如何分配给内存区域。 然后介绍可用的不同属性并解释内存...

本文介绍了 Armv8-A 中的内存转换,这是内存管理的关键。 它解释了虚拟地址如何转换为物理地址、转换表格式以及软件如何管理Translation...

说明:在默认情况下,本文讲述的都是ARMV8-aarch64、armv9架构,linux kernel 5.10,optee3.14, TF-A 2.5

引流关键词: Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU...

引流关键词: 内存屏障, DSB,DMB,ISB,inner,outer,memory barrier,Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-share...

关键词: Non-cacheable,,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU、V...

引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,i...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1. 思考和质疑在一个大架构大系统中,有哪些一致性需要维护?我们先看如下一张...

高速缓存控制器(cache controller )是负责管理高速缓存内存的硬件块,其方式对程序来说在很大程度上是不可见的。它自动将代码或数据从主...

cache是多级的,在一个系统中你可能会看到L1、L2、L3, 当然越靠近core就越小,也是越昂贵。一般来说,对于big.LITTLE架构中,在L1是core...

ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然而...

带着问题去学习,关于cache的一些思考:1、L1/L2/L3 cache到底在哪里?L1/L2/L3 cache分别都是多大?2、L1/L2/L3 cache的组织形式都是怎...

ARMv8有31个通用寄存器X0-X30, 还有SP、PC、XZR等寄存器下面详细介绍写这些通用寄存器(general-purpose registers):

引流关键词: optee、ATF、TF-A、Trustzone、optee3.14、MMU、VMSA、cache、TLB、arm、armv8、armv9、TEE、安全、内存管理、页表…

想不想一夜暴富?拥有很多很多钱,买很多很多房,工作也不忙,无压力,不用亲自Coding和Debug,还有大把大把的时间在CSDN上挥霍...... ...

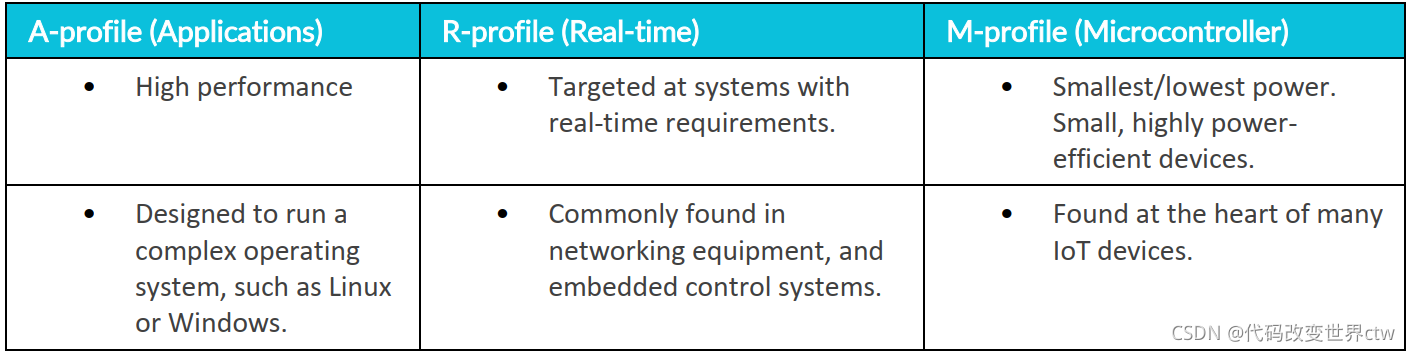

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录👈👈👈1、简介 & 概述ARMv8/ARMv9架构入门到精通-[前言] ---- 必看armv8/armv9的简介-...

rw_semaphore的乐观自旋、handoff机制与mutex的对应机制代码实现略微不同,但是这些机制的思想是完全一样的,因此本章不再赘述乐观自旋...

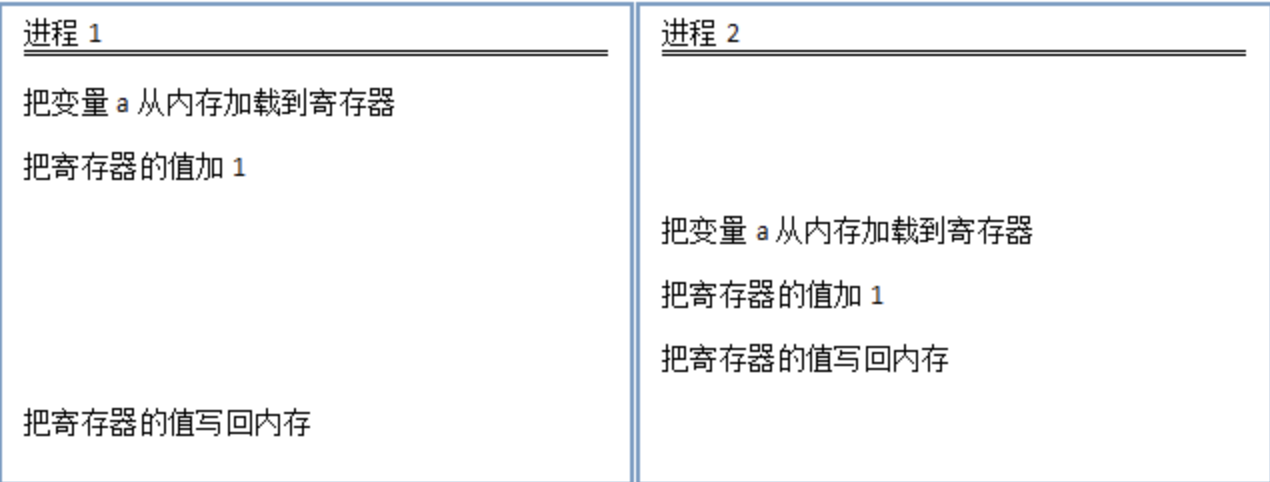

作者 | Aaron来源 | 内核工匠(ID:Linux-Tech)概述从浅到深,逐步分析各种同步机制的功能。1、原子操作解决“读-修改-回写”的完整性,...

【本期受访人:Jay Goldberg——半导体咨询公司D2D Advisory首席执行官。几十年来,他在半导体公司金融咨询、并购交易流程管理方面积累了...

03、EL1&0 Translation regime Stage2、EL2 Translation regime stage1、EL2&0 Translation regime stage1 这三者的区别是什么?