很多人做模拟电路的朋友,都希望有一款“模拟FPGA”,希望有一个“模拟的Verilog”,但现实是没有“模拟的Verilog”只有混合信号建模语言-Veri...

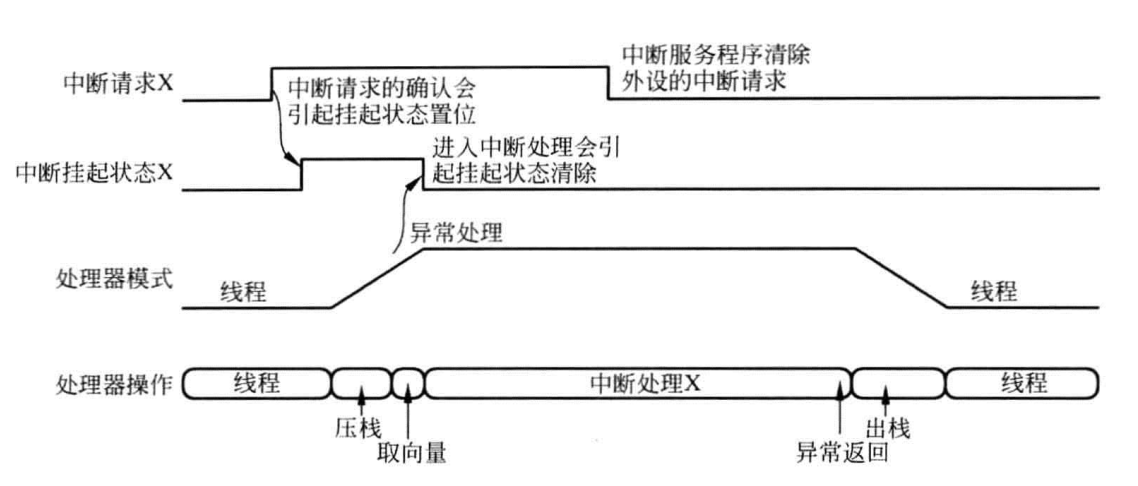

电平触发是外设的中断请求有持续的电平信号,若电平信号在处理器从ISR返回之前没有被取消,则中断返回后将再次触发已经服务过的中断。

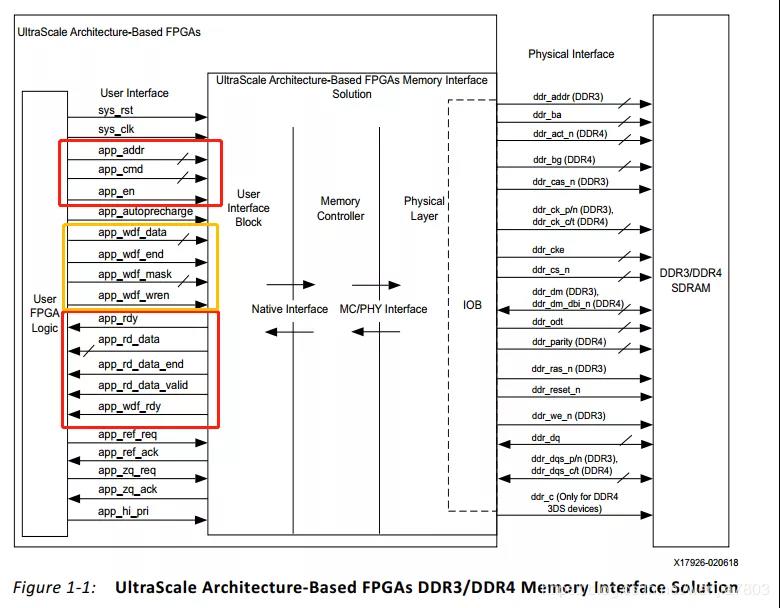

参考资料《pg150-ultrascale-memory-ip》以该手册的脉络为主线,对DDR3/4控制器进行探讨。

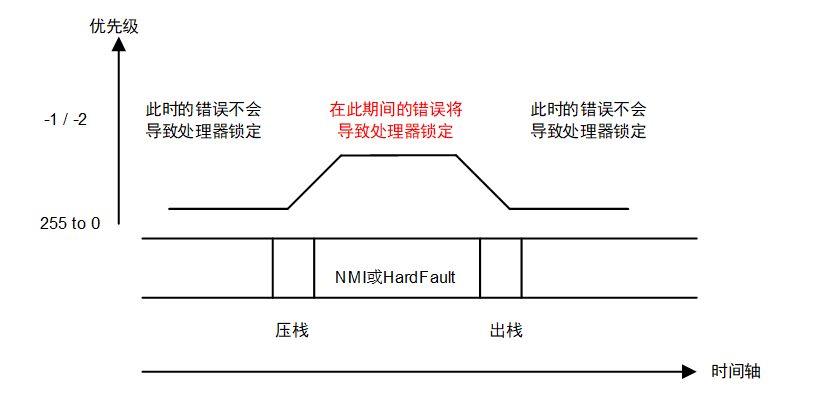

每一个外部中断都有一个对应的优先级寄存器,Cortex-M0中NVIC-IPR共有8个寄存器,而每个寄存器管理4个IRQ中断,所以M0的IRQ中断源最多只...

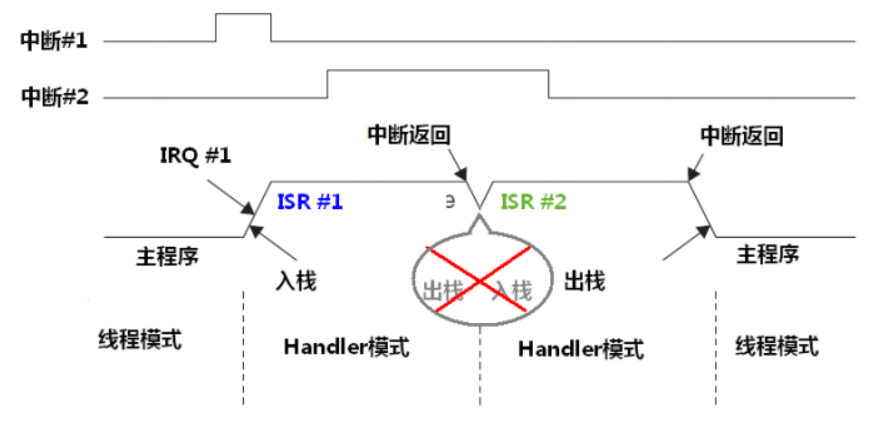

在前几天有客户问了一个问题:如果外部中断来的频率足够快,上一个中断没有处理完成,新来的中断该如何处理?

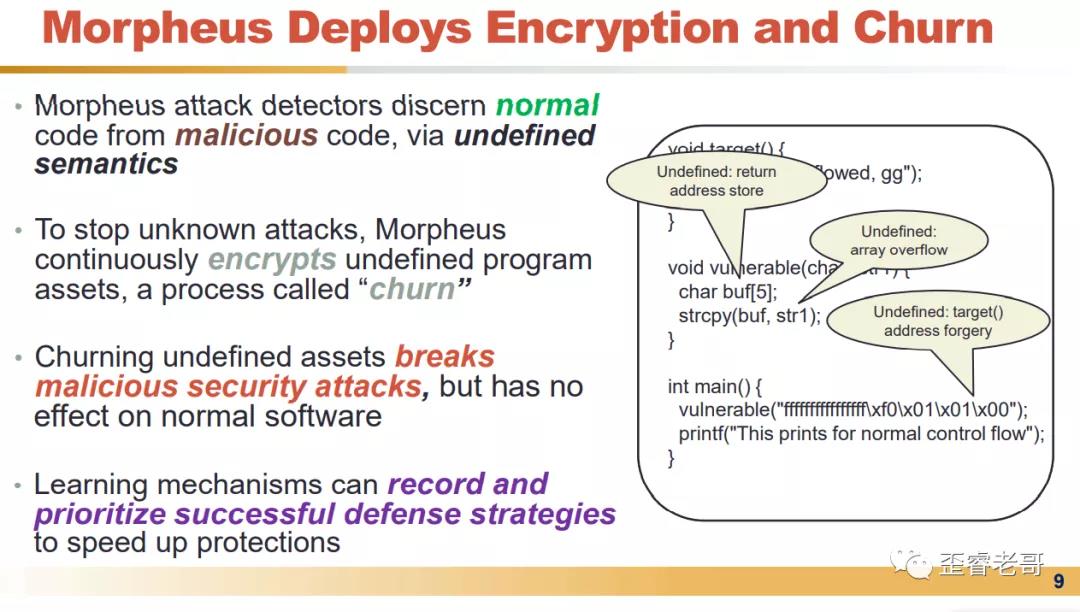

今年的hotchips 33 ,密歇根大学的Austin教授带来MORPHEUS II。上一个版本的MORPUHES 最早出来的时候,被称作:“无法破解”的芯片,号称5...

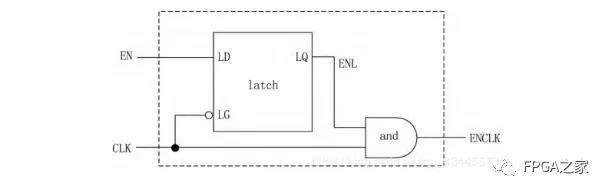

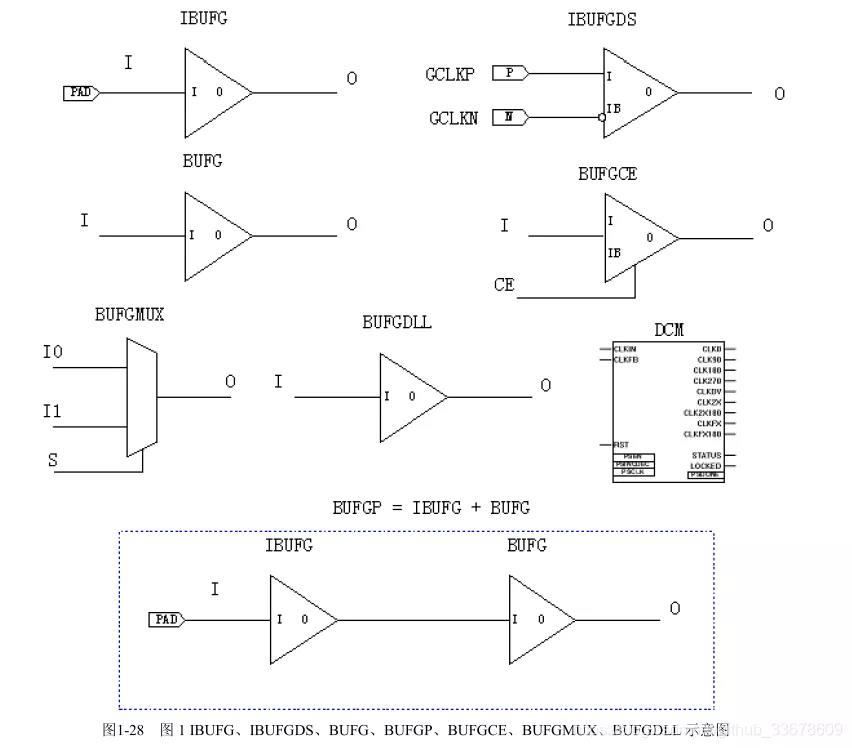

门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分...

在调试程序时,有时Keil会出现报错弹窗“Target is lockup”,我们就没办法再对MCU进行下载、仿真等操作,这个就有可能是处理器处在锁定状...

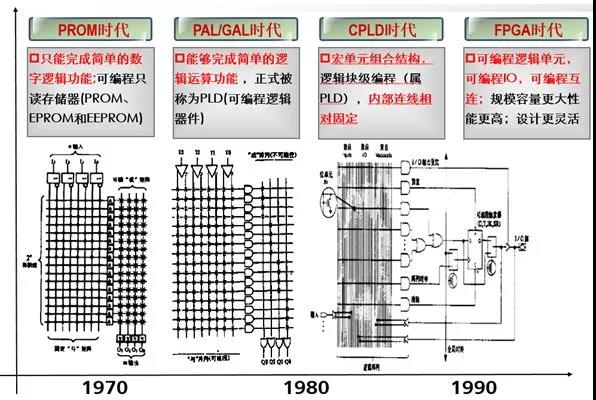

随着云计算,大数据和人工智能技术应用,单靠CPU已经无法满足各行各业的算力需求。海量数据分析、机器学习和边缘计算等场景需要计算架构...

波形文件一般用于仿真后记录波形文件,用于做详细分析和研究。说一下几种波形文件WLF(Wave Log File)、VCD(Value Change Dump)文件,fsd...

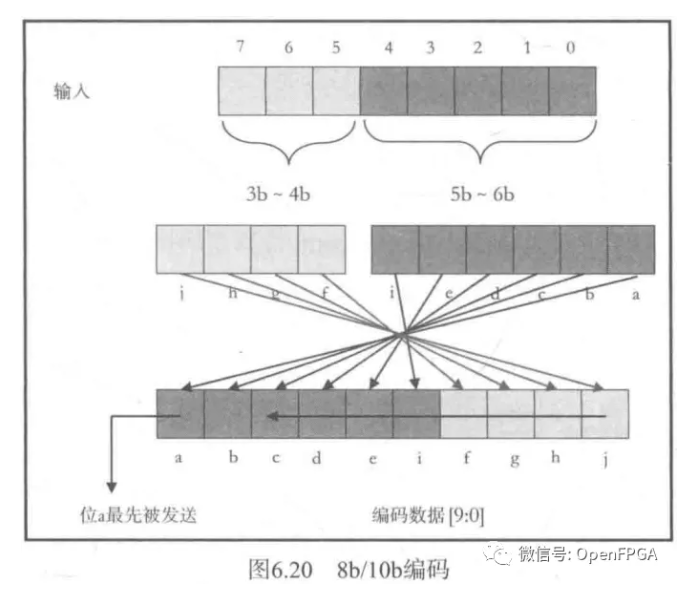

8b/10b编码/解码是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的编解码方式。在发送端,编码电路将串行输入的8比特一...

在Cortex‐M0内核上搭载了一个异常响应系统,支持众多的系统异常和外部中断。其中,编号为1-15的对应系统异常,大于等于16的则全是外部...

大家对使用传统 EDA 工具的设计流程已经驾轻就熟,运行工具,根据分析结果纠错或改进,修改若干参数,然后循环迭代。

在上几个章节中我们介绍了MM32相关的IEC60730-1 B类认证启动自检与运行自检的相关的流程,本章节我们将会介绍一下ClassB认证的程序流程...

就我个人而言,我觉得编写sequence是在验证任何IP时最具挑战性的部分。首先需要仔细构想场景,然后coding。如果没有任何程度的复用,我...

1. IBUFG 即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUFG单元,否则在布...

该FPGA项目旨在详细展示如何使用Verilog处理图像,从Verilog中读取输入位图图像(.bmp),处理并将处理结果写入Verilog中的输出位图图像...

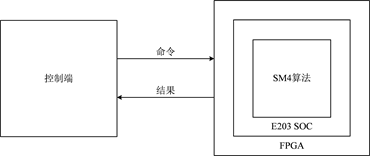

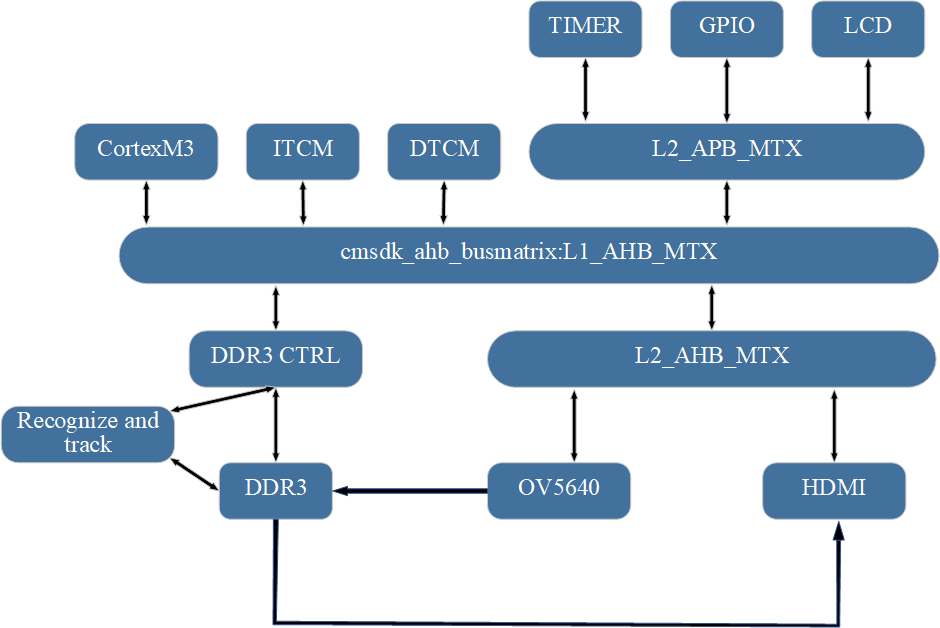

参赛单位:北京理工大学队伍名称:飞虎队指导老师:李彬参赛杯赛:Arm杯参赛人员:余裕鑫 胡涵谦 刘鹏昀获奖情况:全国总决赛一等奖,华...

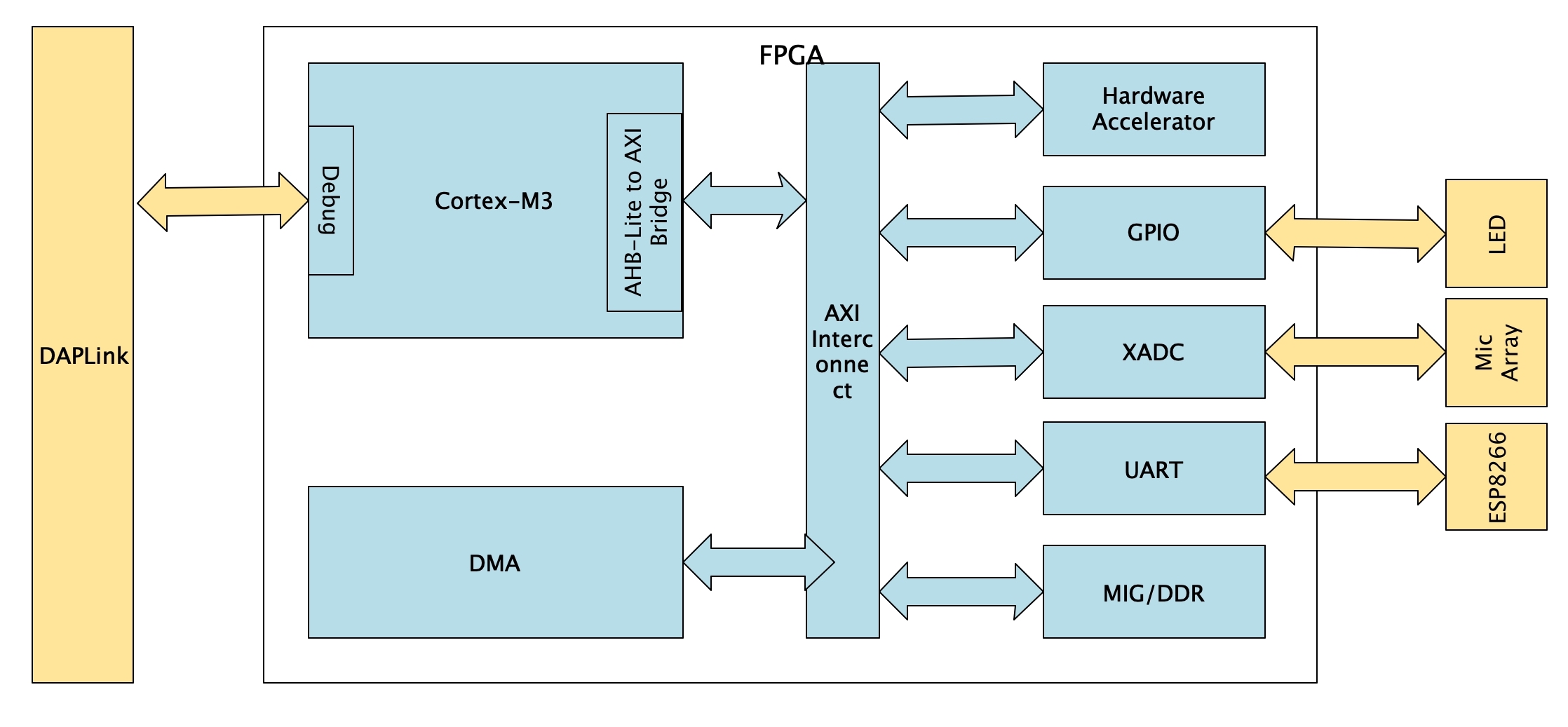

参赛单位:武汉理工大学队伍名称:木大木大指导老师:钟毅,张家亮参赛队员:甘云汉,陆国威,万禹壮总决赛奖项:一等奖(ARM杯企业大奖)

杯赛题目:基于蜂鸟E203 RISC-V处理器内核的SoC设计参赛要求:研究生组/本科生组赛题内容:基于芯来科技的开源蜂鸟E203 Demo SoC进行扩...