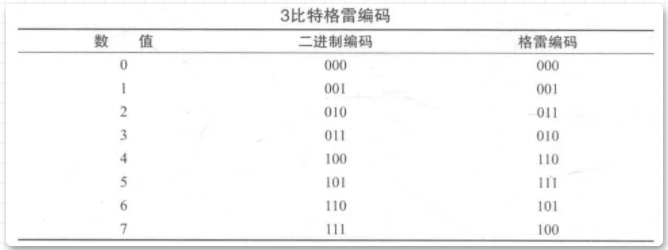

格雷编码是由弗兰克•格雷于1953年发明的,最初是以发明专利的形式出现的。格雷码的主要特点是相邻编码值中只有一个比特发生改变,下面表...

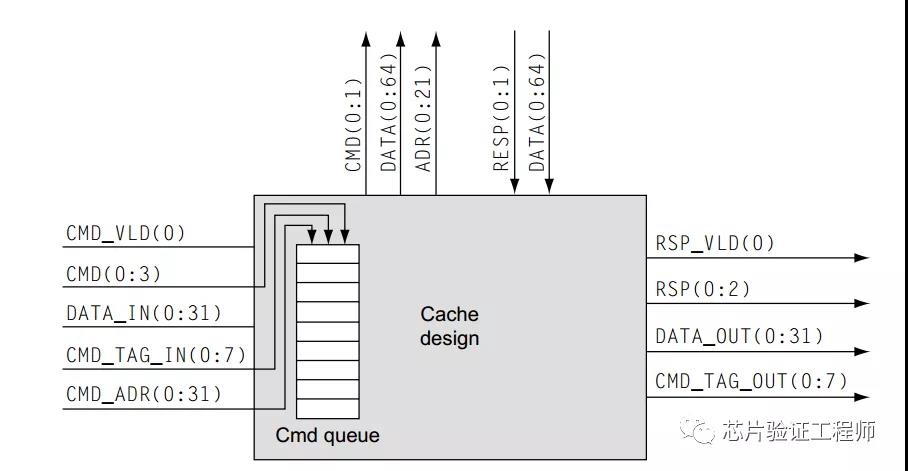

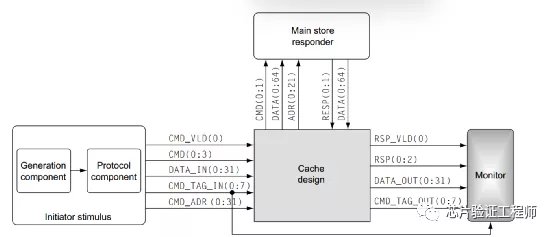

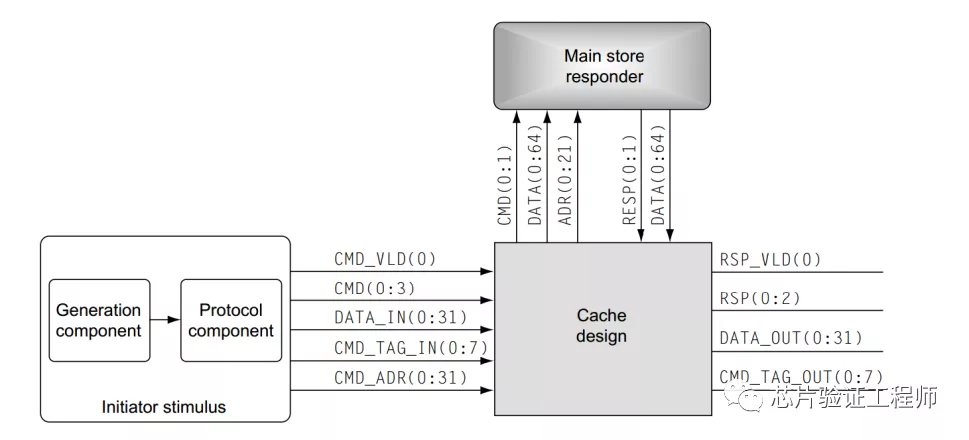

大多数基于仿真的验证环境都是黑盒验证。验证工程师学习设计的规格,然后编写验证环境中的 drivers, monitors, checkers,和scoreboard。...

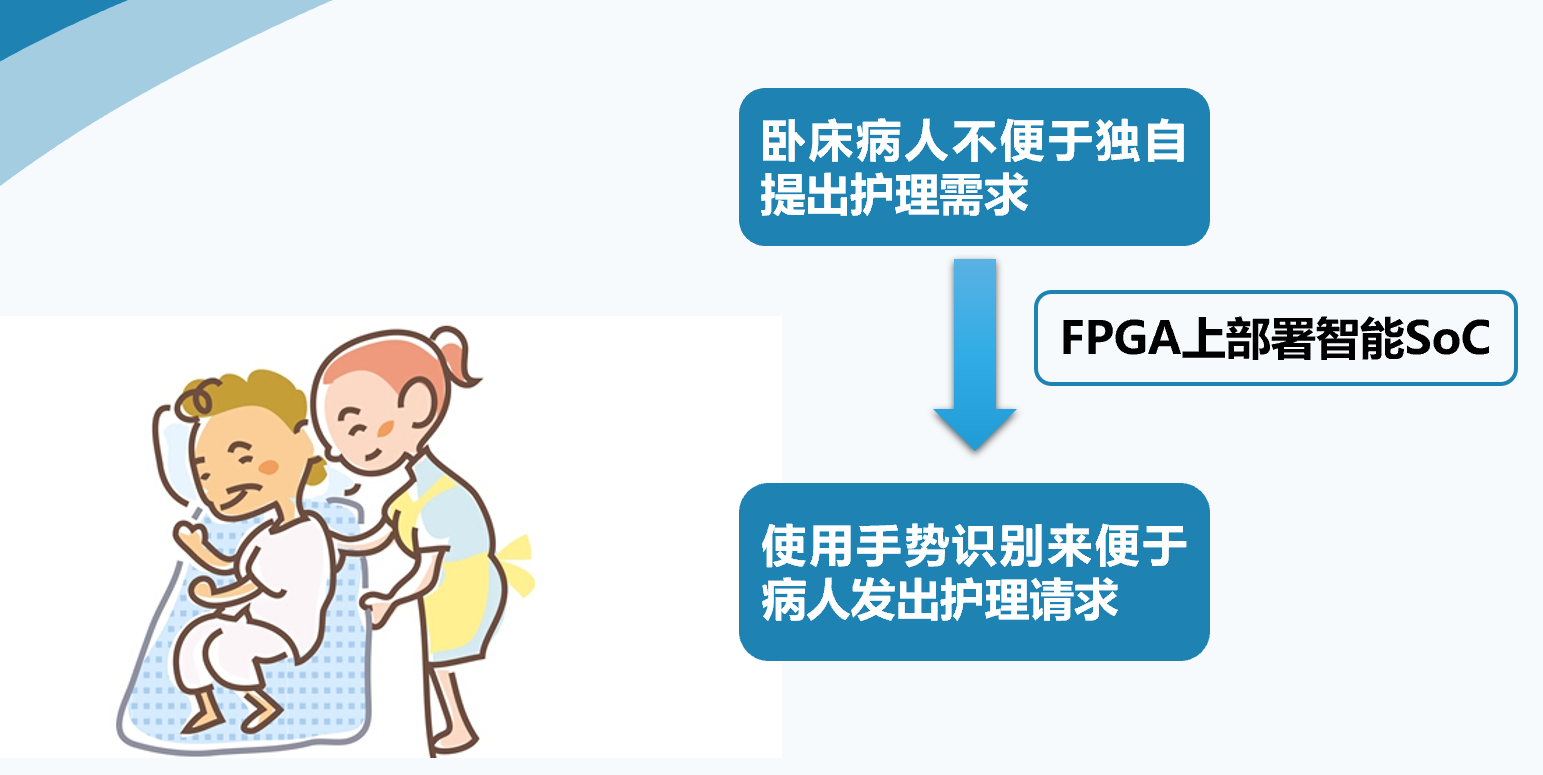

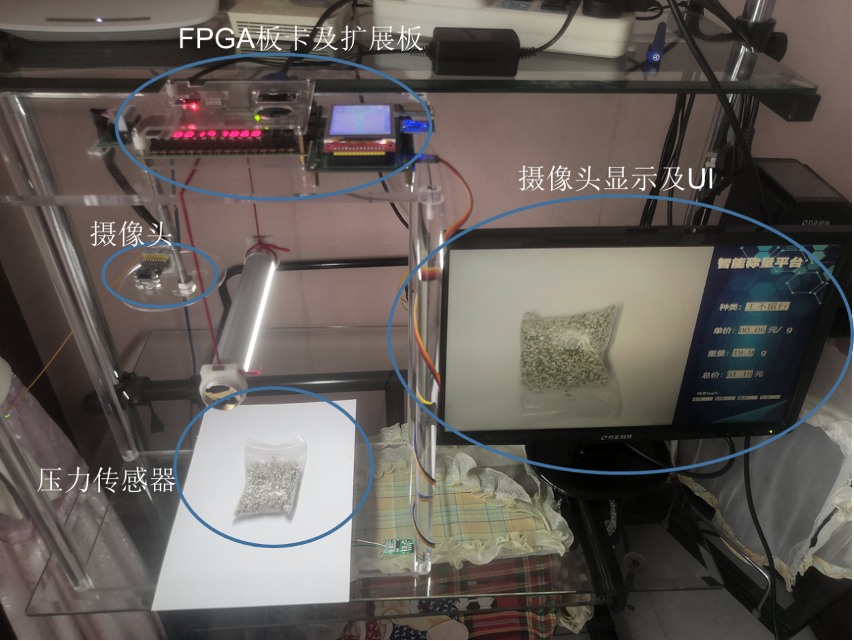

参赛单位:上海交通大学队伍名称:芯灵手巧指导老师:王琴、景乃锋参赛队员:林圣凯、林新源、莫志文总决赛奖项:二等奖

新冠疫情席卷全球,有效佩戴口罩可以极大程度地减小病毒感染的风险。本项目开发了一种如图所示的基于arm Cortex-M3处理器和深度学习加速...

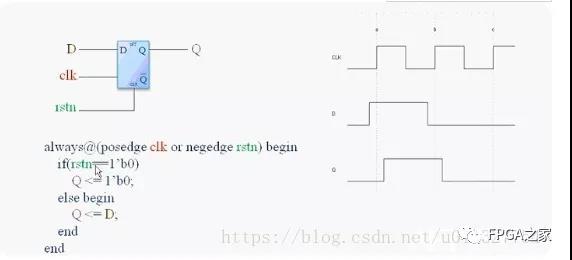

今天写一下时序问题常见的跨时钟域的亚稳态问题。D触发器的原理图和程序:D触发器有个明显的特征就是建立时间(setup time)和保持时间...

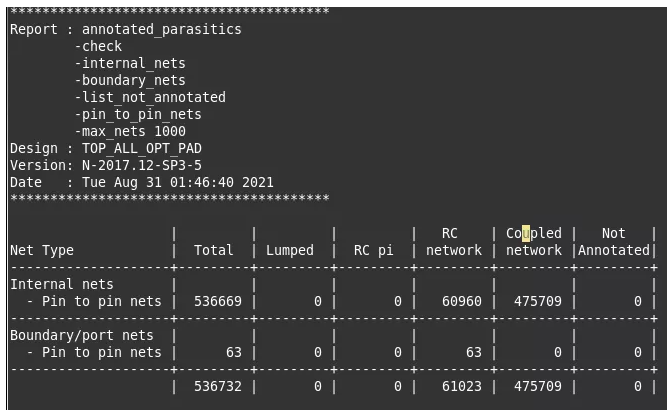

当然,你也可以通过timing report中的相应的符号来确认反标成功与否。这种方式的缺点是无法得到一个全面的统计。即便你看的那条path反标...

本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。杯赛题目:Diligent杯:基于FPGA开源软核的硬件加...

低压差分传送技术是基于低压差分信号(Low Volt-agc Differential signaling)的传送技术,从一个电路板系统内的高速信号传送到不同电路系...

1、DSA(Domain-Specific Architectures,特定领域的体系结构*)将成为未来十年甚至更长时间,计算机体系结构的趋势。

monitor 是一种观察环境的组件,不驱动任何设计的信号,用于观察DUT的:■输出,检查输出接口是否遵守协议并采样数据给scoreboard■输入,...

1、主动驱动DUT,例如时钟和复位。复杂的DUT激励还会包含一些对于激励的开关控制以达到各种边界场景,这个组件称之为initiator (在UVM...

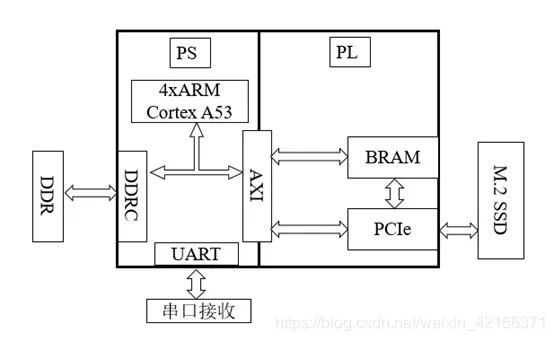

近期实验室项目需对2GB/s的高速数字图像数据实时存储,后续数据带宽将提升至30GB/s。经调研,SATA协议的固态硬盘理论存储有效带宽为600M...

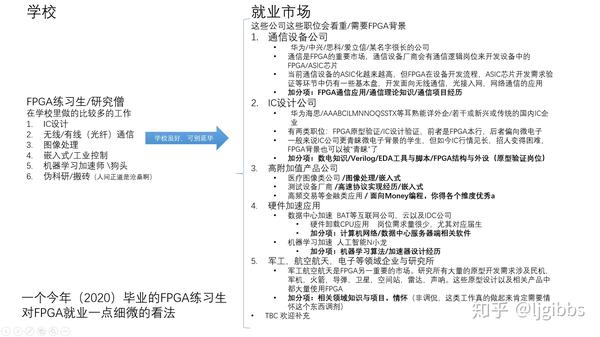

不断演进的本文,尝试回答同学们与 FPGA 就业相关的其他问题。努力不说空话套话,尽可能举自己或者身边人遇到的情况作为例子。但样本有...

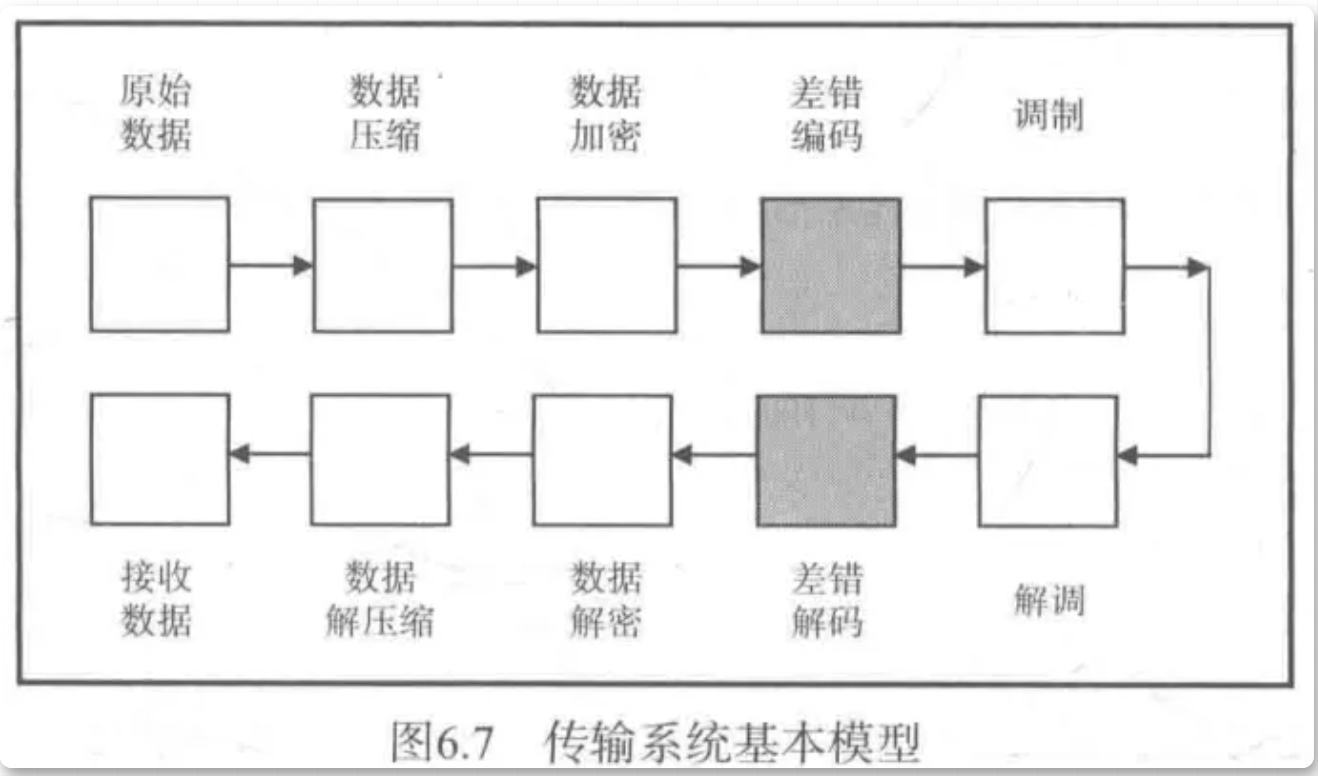

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特),可以计算岀它们的奇偶校验...

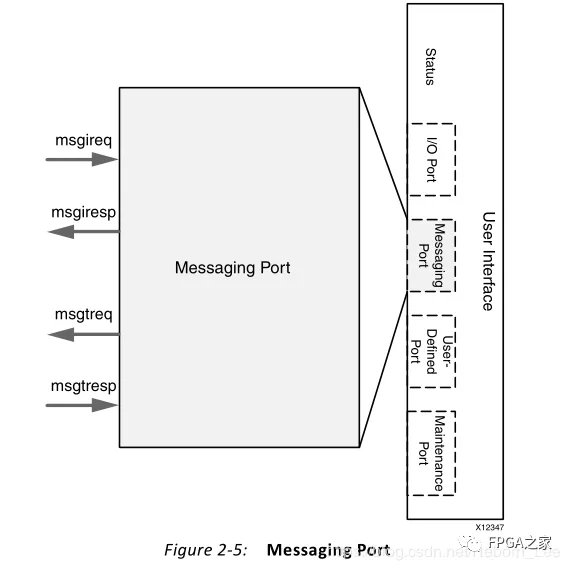

消息传递端口是可选接口(消息也可以组合到I / O端口上,并使用Vivado集成设计环境(IDE)设置视为写入事务)。单独的Messaging端口遵循...

上篇文章:SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port)根据数据手册PG007,介绍到了逻辑层接口的IO口,今天想...

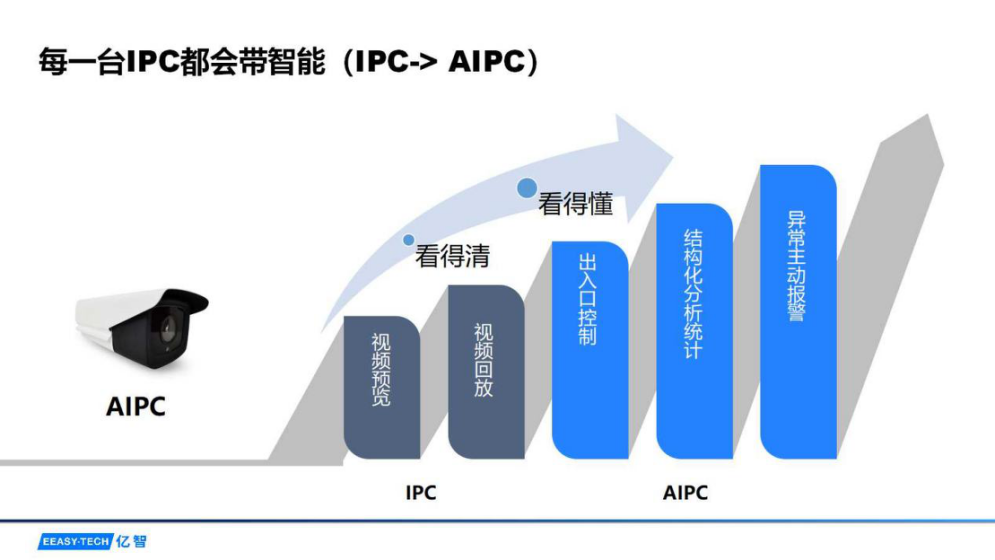

《安创“芯”视野》第32期,邀请到了亿智电子安防产品部VP魏唯,他从安防摄像机的市场发展趋势,智能IPC落地面临的主要挑战等方面,为我们...

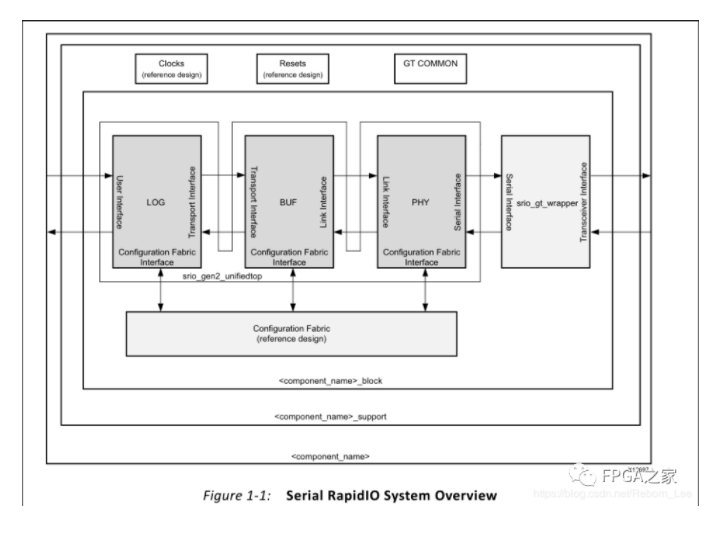

系统总览RapidIO标准分为三层:逻辑,传输和物理。逻辑层定义整体协议和数据包格式。这是端点启动和完成事务(transaction)所必需的信...

在过去的50到60年中,检错与纠错技术有了长足的发展。现今我们对检错和纠错理论有了更好的理解,并且该理论还在不断的发展。编码理论已...

System Generator从入门到放弃(九)-利用Vivado HLS block实现Vivado HLS调用C/C++代码