刚毕业那会研究了一段时间的3D-Torus,近期又看了CHI和CMN相关的内容,感觉互联架构挺有意思的。我想尝试做一个支持AXI协议的互联架...

✎ 编 者 按 通过继承Bundle,在SpinalHDL中我们可以定义各种各样的复合数据类型。今天,关于Bundle的几个容易被忽略的点,一同来看下。

✎ 编 者 按 该小系列就SpinalHDL中关于StreamArbiter部分从基础原理到最终的实现细节进行总结。本篇先从roundRobin讲起。

SpinalHDL是一种基于scala的硬件描述语言,能够提供更高级别的参数化和抽象能力。它解决了Verilog的痛点,并且和传统的IC-flow和谐共存...

先来看一个非常简单的例子,假定我们有一个输入数组,长度为8,此时我们根据select信号选择对应的输入作为输出。

忆往昔写Verilog与SystemVerilog时,在仿真过程中,不可避免的会出现多进程并发的情况,在构建仿真架构时,总是少不了这几个语法的出现:

今天来谈谈SpinalHDL中StreamCCByToggle组件设计不足的地方。前言 在之前的文章里,曾经有过一篇就StreamCCByToggle的具体细节原理展...

SpinalHDL中的StateMachine设计思路让我个人觉得耳目一新,写出来的代码如同伪代码般令人读着如同一种享受。然而在有些设计里会有要求是...

今天,再来好好聊聊SpinalHDL中的FIFO。也许你是逻辑设计老手,但好好看看这篇文章,或许你也会有新的思考。

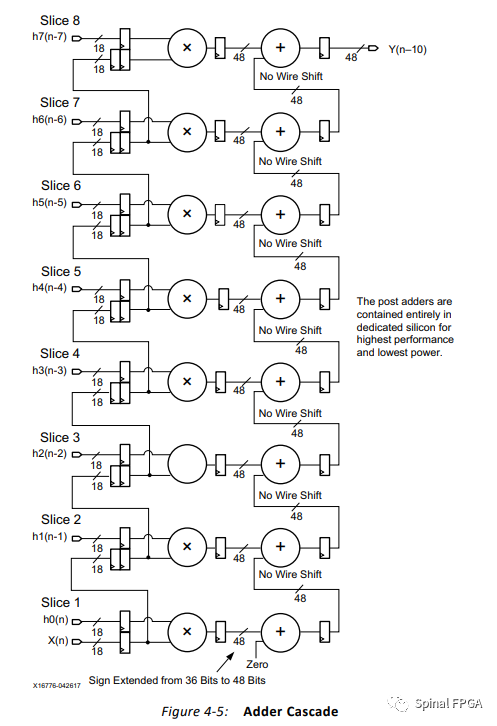

本文来源:yportne不同型号的 FPGA 的硬件资源不同,你所设计的电路结构可能也要相应变化。让我们以一个简单的例子,FIR 滤波器,来看看...

最近遇到一个对输入以2为底求对数向下取整的逻辑需求。正好可以研究下如何去实现以2为底求对数向上取整及向下取整的实现。

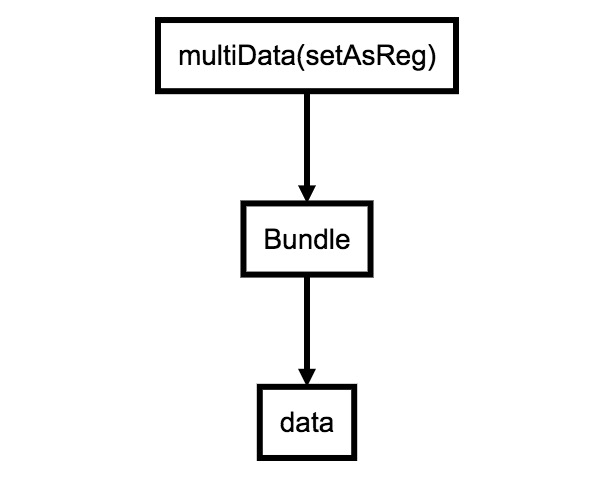

在设计中一旦牵涉到复杂的数据结构,封装是不二选择,这不仅能够让我们的代码看起来更优雅,也能够减少代码中的那些体力活儿(连线)。当...

本篇教程来源于微信网友王璞。很多Spinal HDL新手朋友碰到环境安装的问题,特别是Windows下需要重新编译Verilator之类的工具,对新手很...

在逻辑设计时,有这么一个场景很常见:对于输入的一组总线,我们需要改变其中的某些信号的赋值,而其他信号保持不变输出。正如下面的设...

众所周知,SpinalHDL仿真目前仿真器首推Verilator,无论是在Mac还是Linux下安装都很轻松,唯独在Windows下安装是一件令人头疼的事情,由...

在前面的五篇文章中,对于Axi4总线互联的所有设计细节都已经做了介绍。那么剩下的就是集成工作了。再来回顾整个总线互联架构:

本文主要记载如何从零开始在win平台搭建SpinalHDL开发环境并跑通第一个spinal project demo。

相较于Axi4写通路,多通路的多选一就容易多了。对于Axi4ReadOnlyArbiter,其仅需处理两个问题:

Decoder解决了一拆多的问题,那么Arbiter就需要解决多选一的问题。对于写通道,axi4有aw、w、b三个通道,相应地Arbiter就需要解决:

对于Axi4读操作而言,其指令的完成由ar、r两个通道完成,相较于写操作,其通道数虽然少了一个,但也是两个方向的数据流: