本文翻译自技术白皮书《CXL Memory Expansion: A Closer Look on Actual Platform》

MLPerf存储基准测试V1.0衡量存储系统在AI工作负载下的性能表现,其核心指标是在给定的训练模型和GPU型号下,存储系统能提供的带宽以及支...

IPC(Instructions Per Cycle)是指每个周期的指令执行数,用于衡量处理器的执行效率。IPC越高,表明处理器在相同频率下可以执行更多指令。

引言:由于服务器CPU核心数量的不断提升,不少客户发现在部分场景用单插槽(即单路CPU)就能替代以前的双CPU。

近日,天翼云联合权威科技媒体InfoQ举办了以“新存储,更轻量”为主题的线上技术分享会。天翼云存储产品线总监武志民讲解了HBlock的创新设...

近日,天翼云联合InfoQ举办了以“新存储,更轻量”为主题的线上技术分享会。天翼云存储产品线总监潘亚莲以“轻量级存储集群控制器HBlock的...

上周我分享了FMS 2024会议的资料,唐杰总留言说 “给写个导读呗”。说实话看资料也是个耗时间精力的活,比如去年我工作比较忙,所以三大技...

基本操作git branch 查看当前分支git branch -a 查看所有分支git pull 更新当前分支git checkout XXX 切换到某分支git checkout . 放弃...

在IB/RoCE网络环境中,经常会遇到一些网络相关的配置不当问题,这些问题可能导致性能出现降级。本文对这些问题做一个总结,以供记录备忘。

Netsol基于性能设计,其MRAM支持快速数据读写操作,支持Octal SPI (OPI),工作频率高达200MHz,数据传输速度高达400MBps。

我们知道 LPDDR4 相比 DDR4 一项重要的改动是在单个颗粒上支持独立的双通道(Channel),单个通道位宽 16 比特。这样一来,系统可以在 D...

本文内容,来自蚂蚁集团异构计算与推理引擎负责人-赵军平老师,在AICon全球人工智能开发与应用大会上的演讲ppt。

我在昨天的撰文《VMware分层内存愿景:NVMe与CXL Accelerator方案》中,刚发过SNIA 2024 Compute, Memory, and Storage Summit的资料,...

这是2024年的春季,一年一度的SNIA Compute, Memory, and Storage Summit(CMS,计算、内存和存储峰会)在线上举办。我又当了一把资料的...

今天分享的是2024 OCP Storage Tech Talk 的演讲资料,官网来源是[链接],也有qiang外的视频。唯一美中不足的是,ppt(pdf)只有一个单...

随着人工智能技术的快速发展,语音交互已成为越来越重要的人机交互模式。特别是在智能家居、个人助理和客户服务支持等领域,对语音聊天...

夏天马上就要到了,“瘦身”不光是特定人群的需求,也是数据中心的需求。构建轻量化、低碳化、高性价比的新型数据中心,更有效地支撑经济...

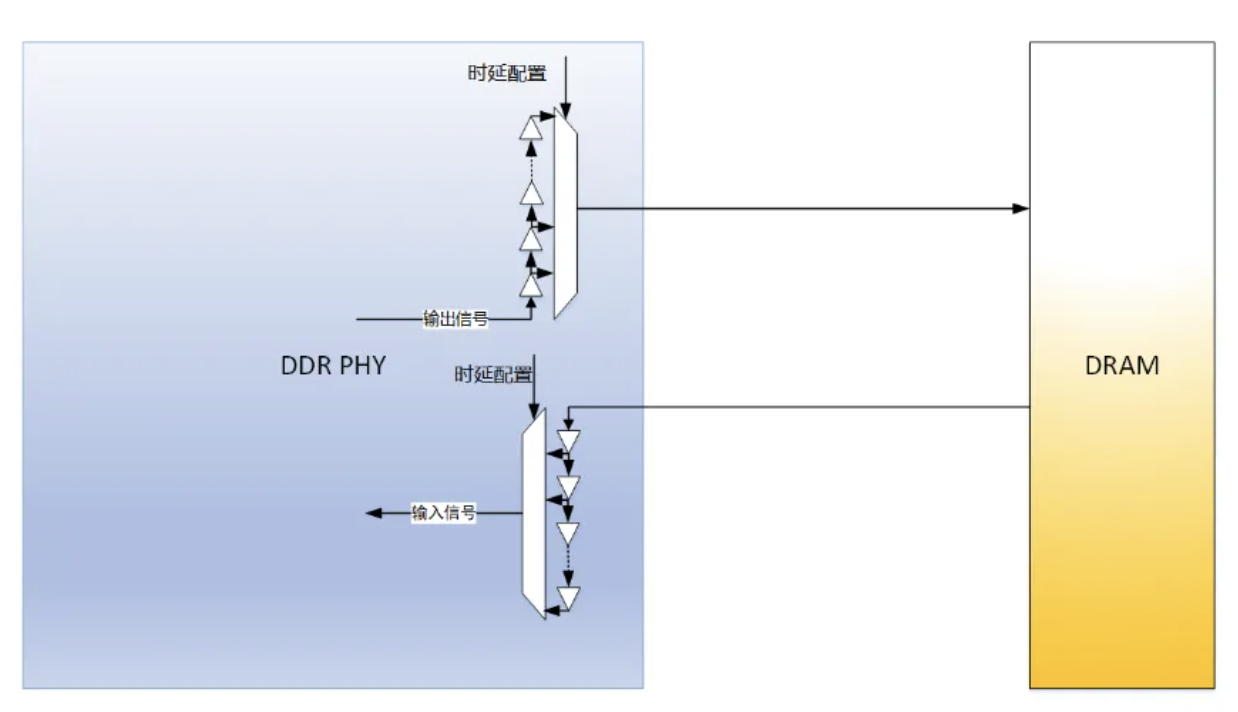

DDR接口速率越来越高,每一代产品都在挑战工艺的极限,对DDR PHY的训练要求也越来越严格。本文从新锐IP企业芯耀辉的角度,谈谈DDR PHY训...

过去一年半,AI大模型标志性的应用相继出现,从ChatGPT到Sora一次次刷新人们的认知。震撼的背后,是大模型参数指数级的增长。

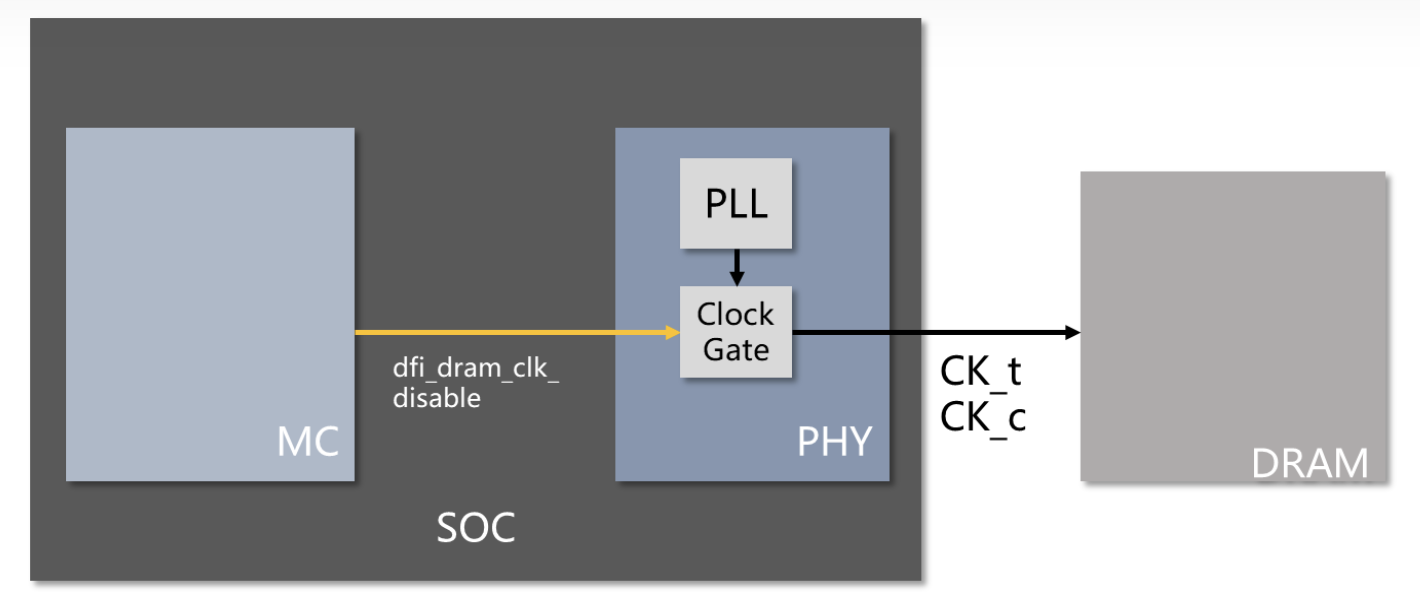

当 DRAM 处于自刷新状态时,系统可以保持提供给 DRAM 的 CK 时钟,或者关闭时钟供给。一般来说,停止 CK 时钟能够进一步降低 DRAM 和系...