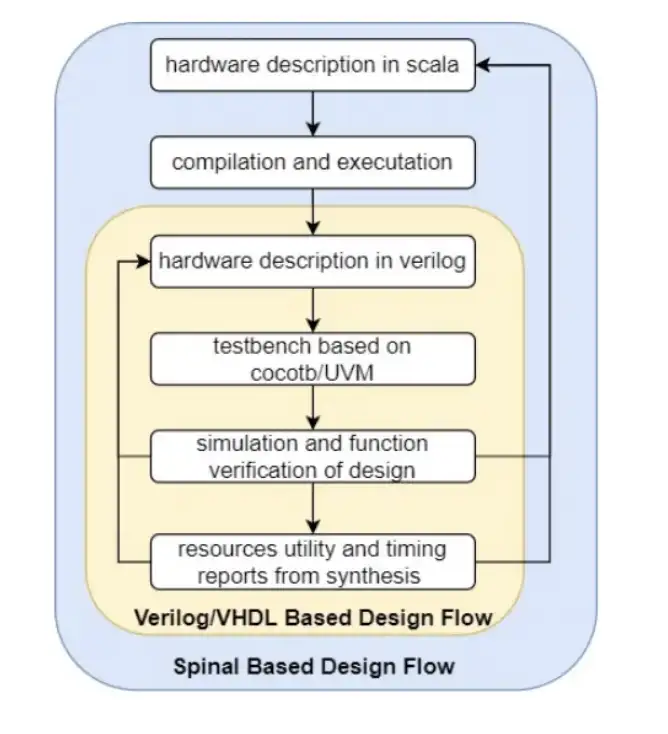

我们在编写一些比较复杂的 Verilog 代码时,通常需要进行大量的手动连线工作,这种工作十分容易出错,并且在代码模块的嵌套层级较多时,...

在 FPGA 的群里,经常会有人讨论以后 Verilog 会如何发展?HLS 和 DLS 谁会胜出?用 Python 来写更快还是现在用的相对多一些的 Chisel ...

Verilog 语言和 VHDL 语言是两种不同的硬件描述语言,但并非所有人都同时精通两种语言,所以在某些时候,需要把 Verilog 代码转换为 VHD...

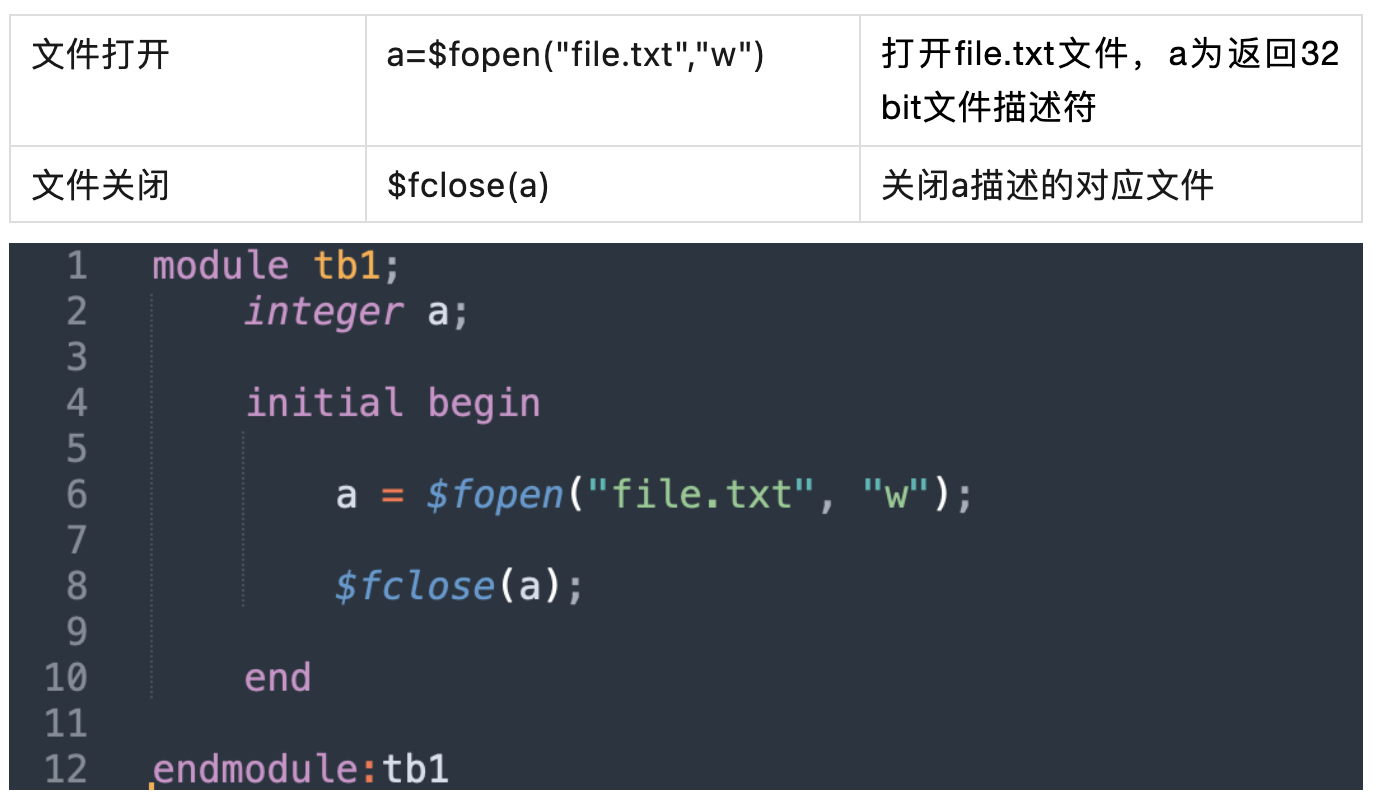

在Verilog中,文件读取和写入是非常有用的。从文件中读取测试激励输入,并写入输出以供比对。 在Verilog中读取或写入文件的方法很少。如...

说明:这种方法相当简单朴素,python做出需要的字符串,写到文件。好处是不需要技巧,坏处是python代码可维护性较差。

在介绍CLAHE算法之前必须要先提一下直方图均衡化,直方图均衡化算法是一种常见的图像增强算法,可以让像素的亮度分配的更加均匀从而获得...

传说这个世界上只有代码三种编辑器,Vim , Emacs 和其他编辑器,其中Vim被称作编辑器之神,Emacs被称为神的编辑器,当然,其他编辑器永...

Verilog提供了很多对文件操作的系统任务和函数,例如打开关闭文件、向文件写入值、从文件读出值等等。

我们在编写一些比较复杂的Verilog代码时,通常需要进行大量的手动连线工作,这种工作十分容易出错,并且在代码模块的嵌套层级较多时,更...

摘要:领域特定架构已成为计算机发展的一种趋势。在提供更高效算力的同时,它也给底层硬件的开发带来了更大的挑战。传统的芯片设计和验...

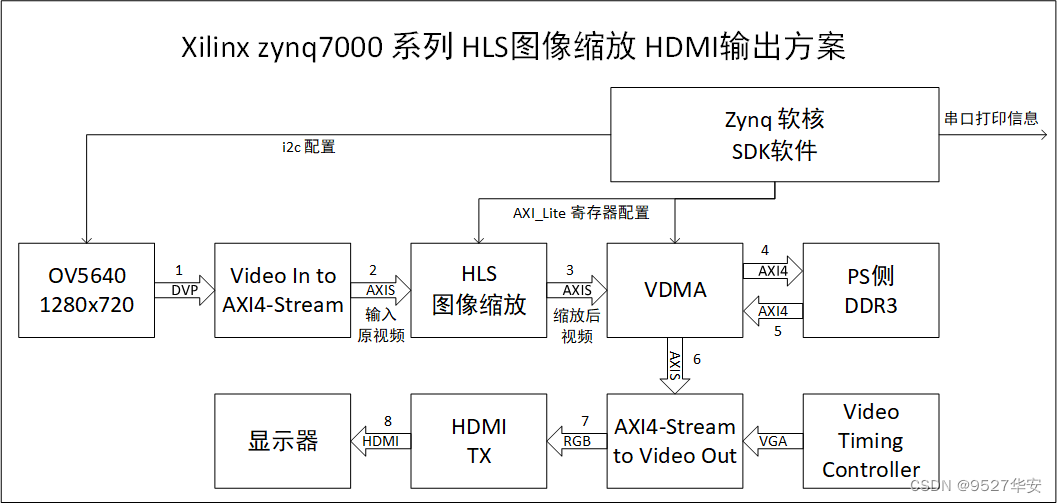

没玩过图像缩放都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。目前市面上主流的FPGA图像缩放方案如下:1...

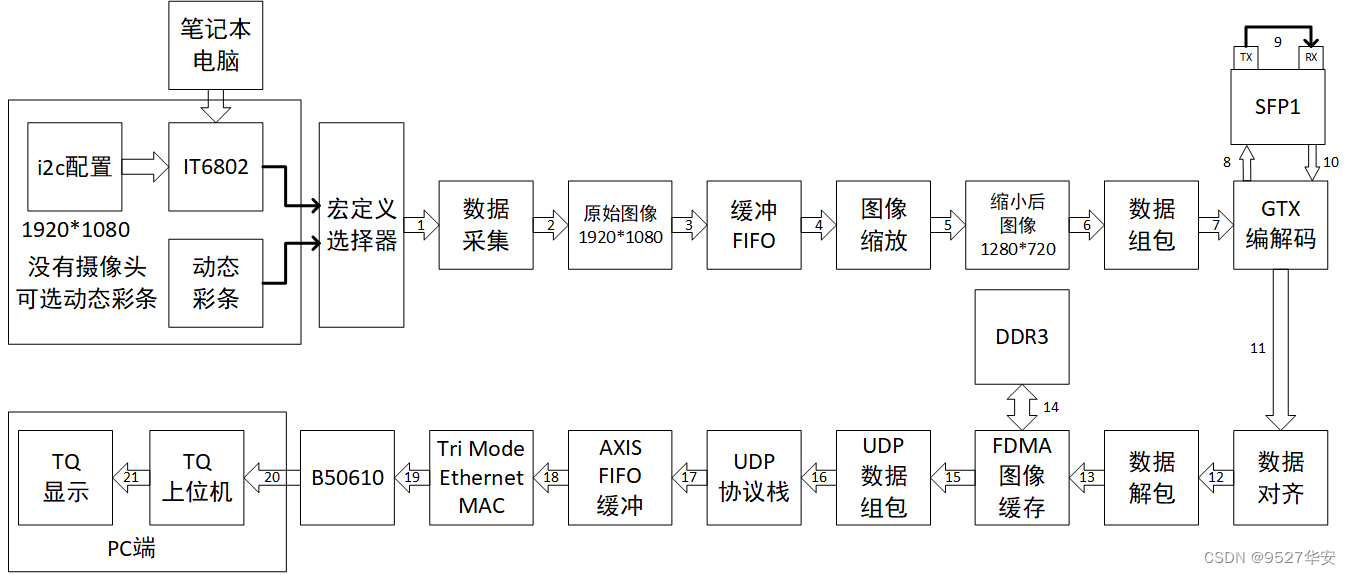

FPGA高端项目:图像缩放+GTX+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

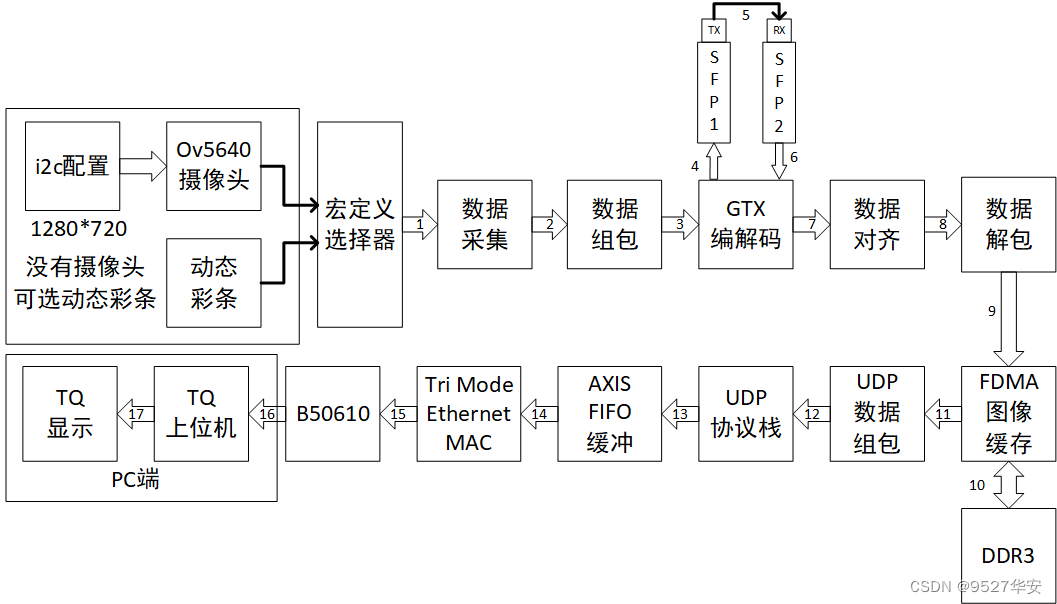

FPGA高端项目:图像采集+GTX+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

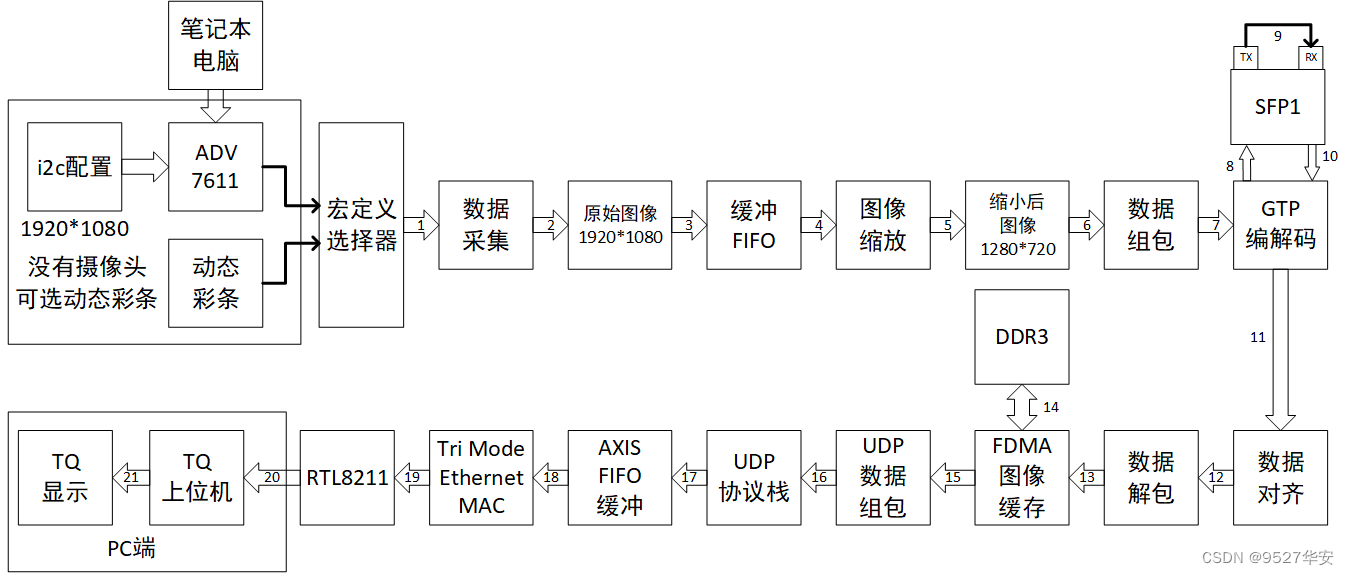

FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

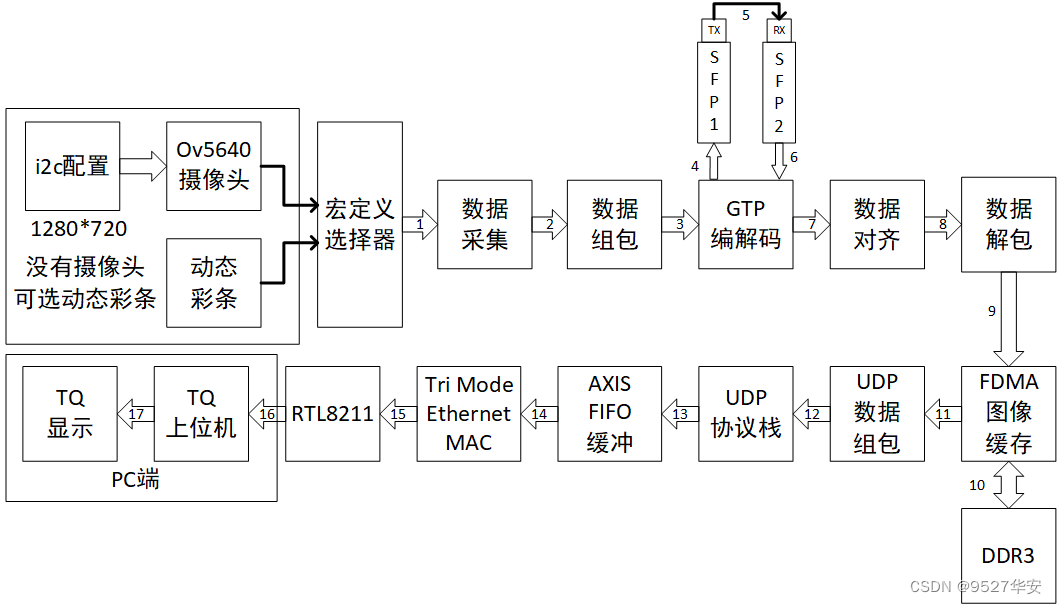

FPGA高端项目:图像采集+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

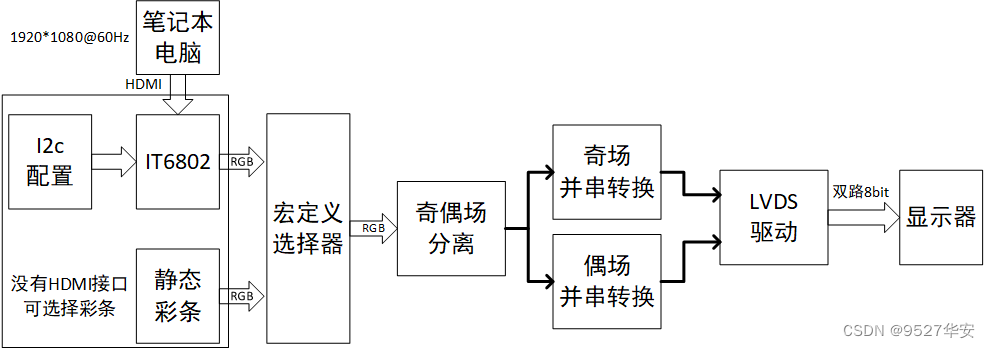

LVDS协议作为中等速率的差分信号,在笔记本电脑和手机等消费电子领域应用广泛,FPGA实现LVDS视频协议也有广泛应用,一般在军工和医疗领...

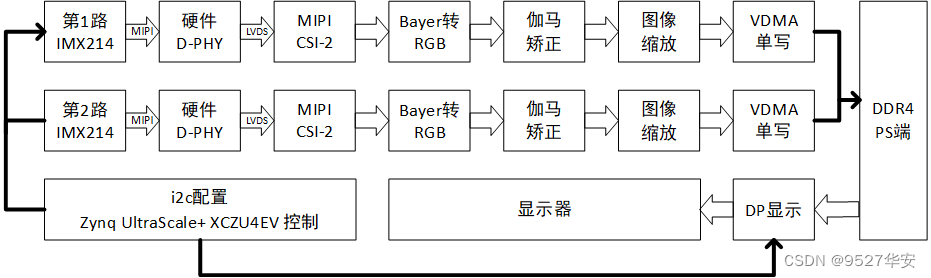

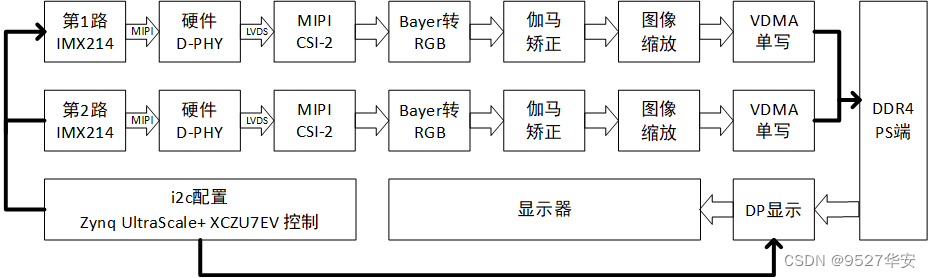

Zynq UltraScale+ XCZU7EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

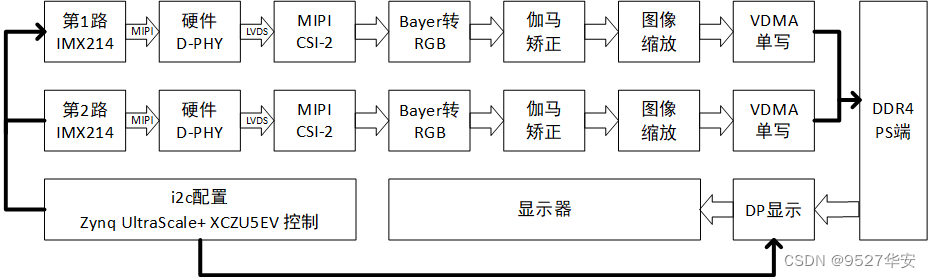

Zynq UltraScale+ XCZU5EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

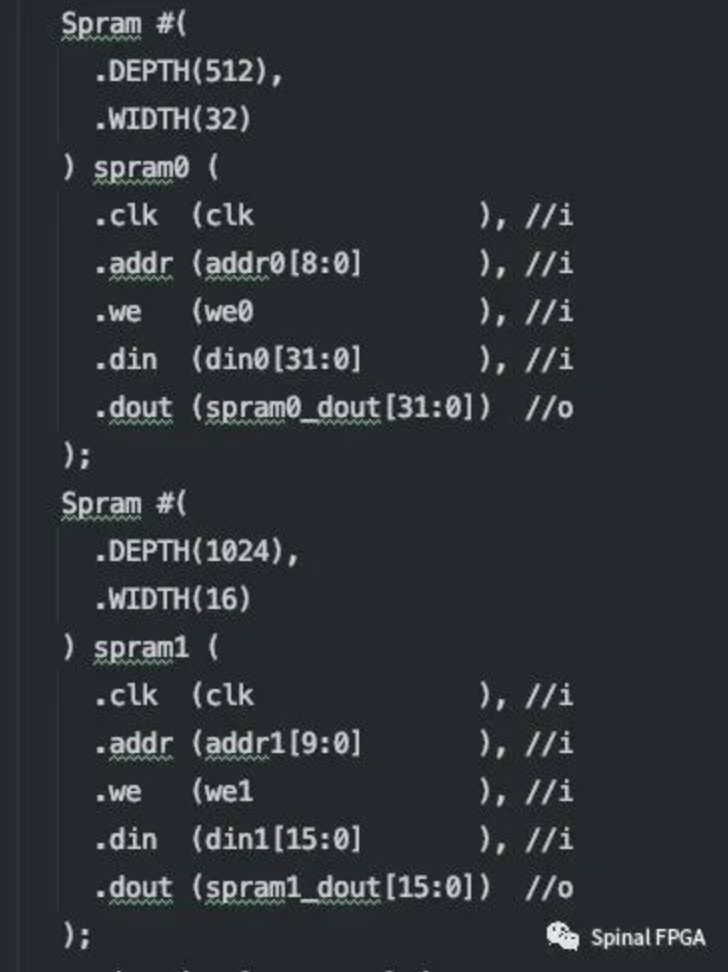

最近微信交流群里有小伙伴在讨论后端做memory时memory使用的大小不同例化时也需要使用不同的memory名称,这种情形往往采用BlackBox的形...

Zynq UltraScale+ XCZU4EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持