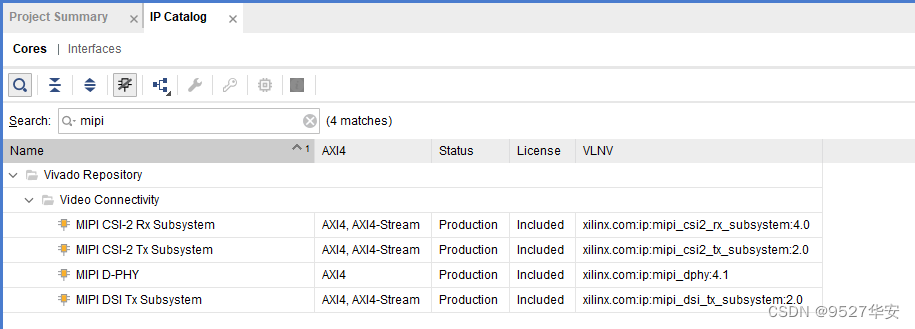

FPGA解码 4K MIPI 视频 纯vhdl实现 CSI2 RX 采集OV13850,提供工程源码和技术支持

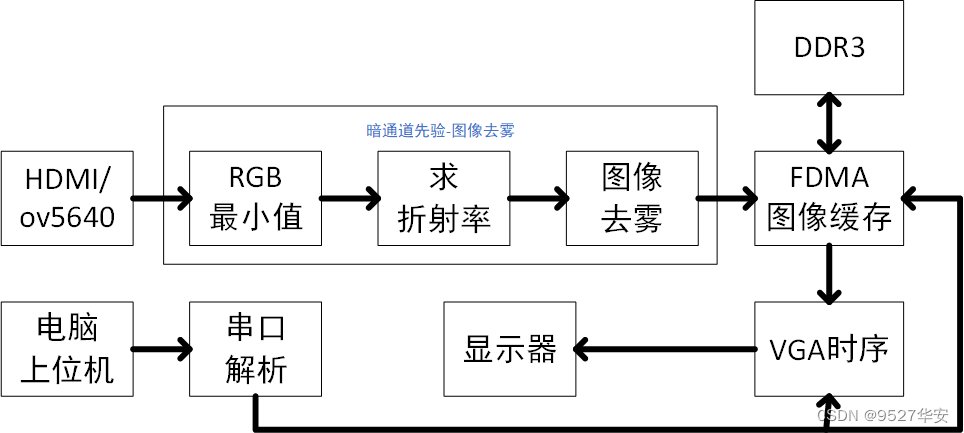

本文详细描述了FPGA实现图像去雾的实现设计方案,采用暗通道先验算法实现,并利用verilog并行执行的特点对算法进行了加速;本设计以HDMI...

Xilinx Artix7 系列FPGA纯verilog图像缩放,工程项目解决方案,提供4套工程源码和技术支持

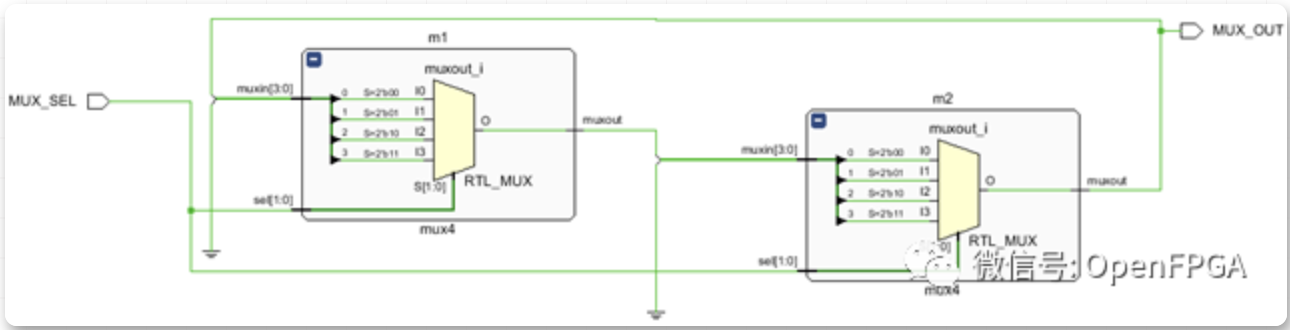

本文列出了FPGA设计中常见的十个错误。我们收集了 FPGA 工程师在其设计中犯的 10 个最常见错误,并提供了解决方案的建议和替代方案。本...

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景...

问题:近年来,不断增加的城市人口、更复杂的人口密集建筑以及与大流行病相关的问题增加了火灾侦查的难度。因此,为了增强消防人员对火...

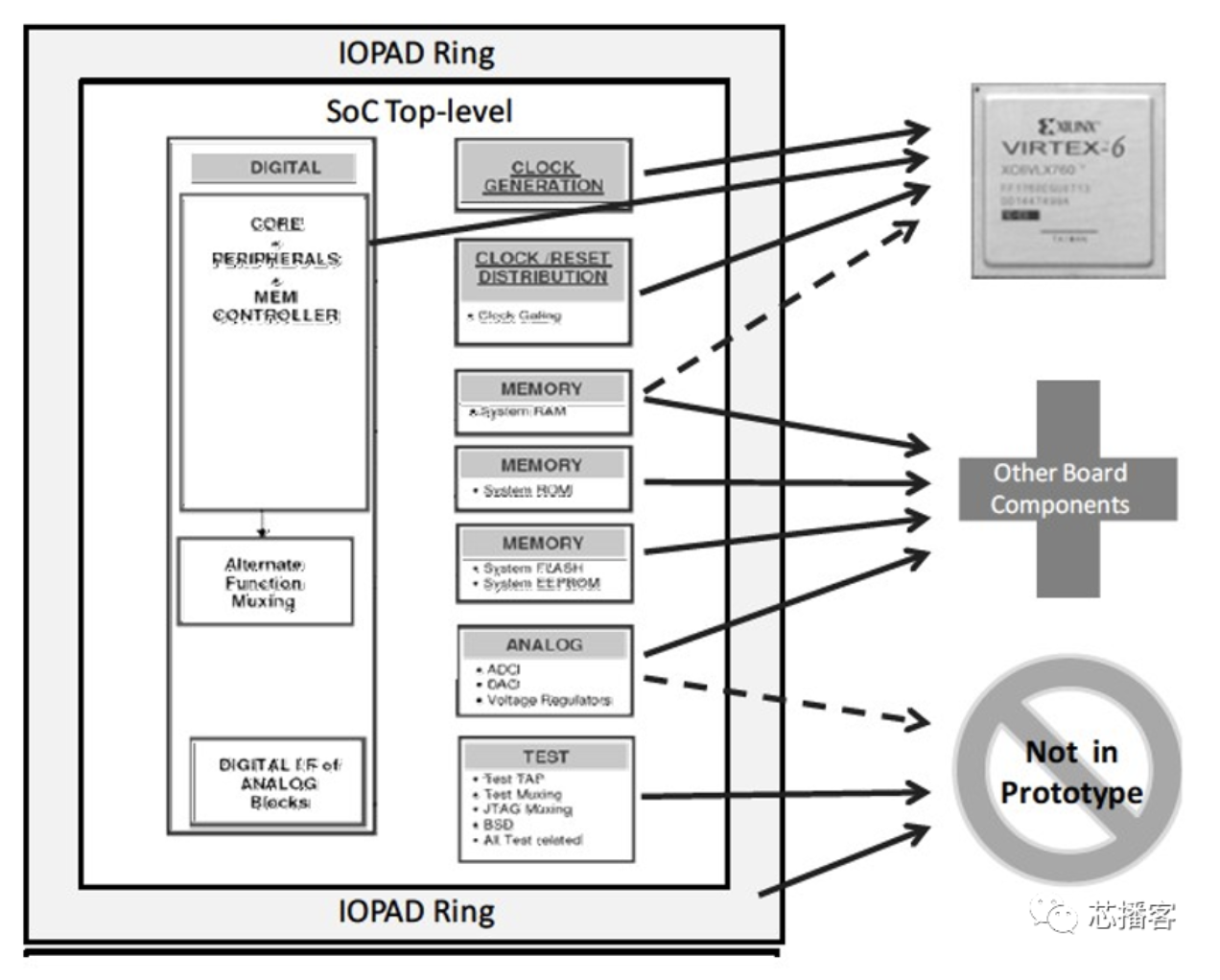

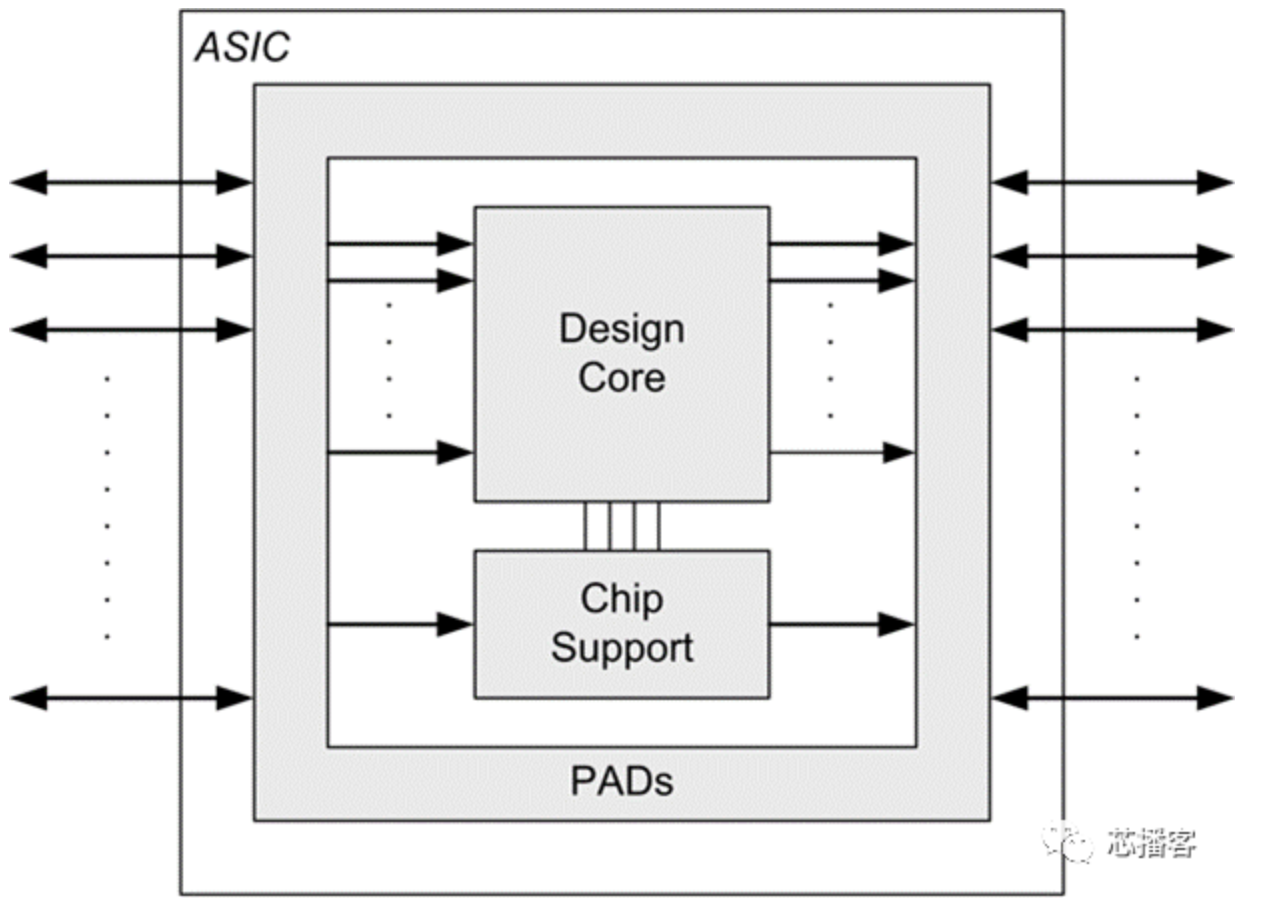

芯片设计流程中,验证是至关重要的,验证除了常规必备的Simulation还有非常重要的FPGA原型验证,但是,在对ASIC代码到FPGA移植过...

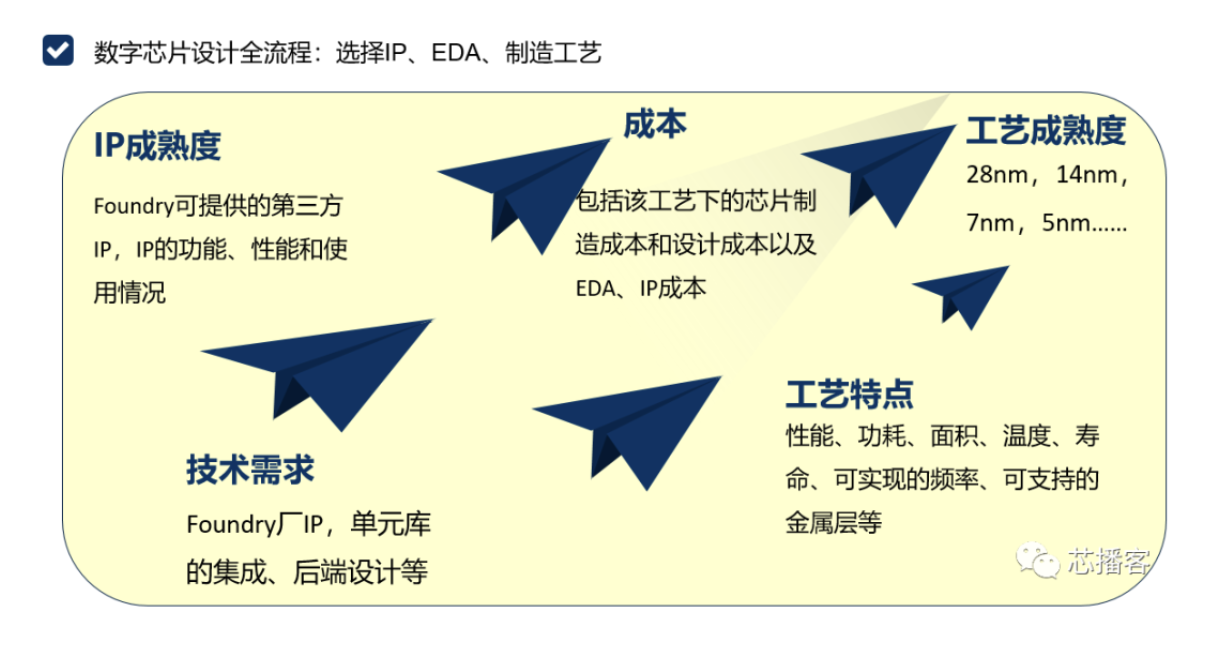

随着社会应用的不断丰富,芯片要满足日益增长的市场需求,那么芯片设计的选型就非常的关键,从制程、功耗、IP等方方面面的考虑,...

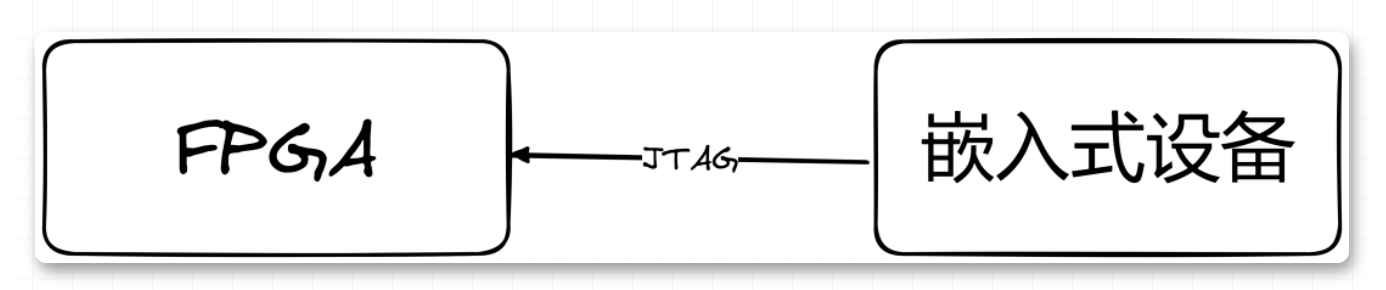

之前介绍过一种远程(无线)更新的方式,详见《起飞!通过无线WIFI下载调试FPGA》,这种方式缺点有两个:一是速度较慢;二是我们的设备...

当一个SoC芯片项目将要切入到FPGA原型验证阶段时,FPGA原型验证团队如何评估是否可以进入原型验证阶段进行新一个阶段的验证工作呢?

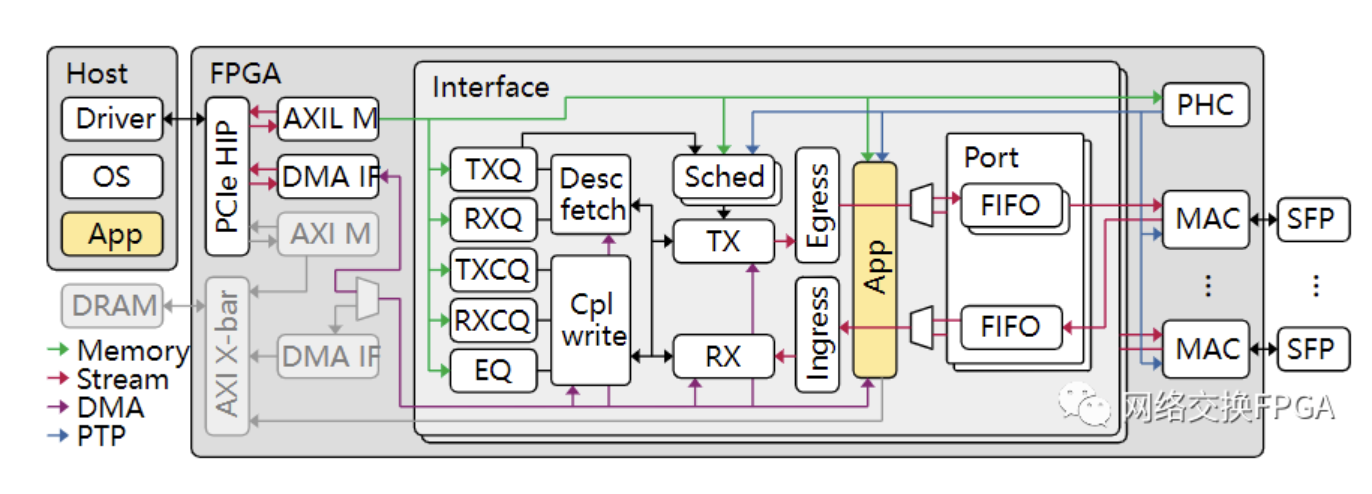

差不多整整三年前,即2020年5月12日时,我们分享了一篇有关100G开源网卡的文章《业界第一个真正意义上开源100 Gbps NIC Corundum介绍》...

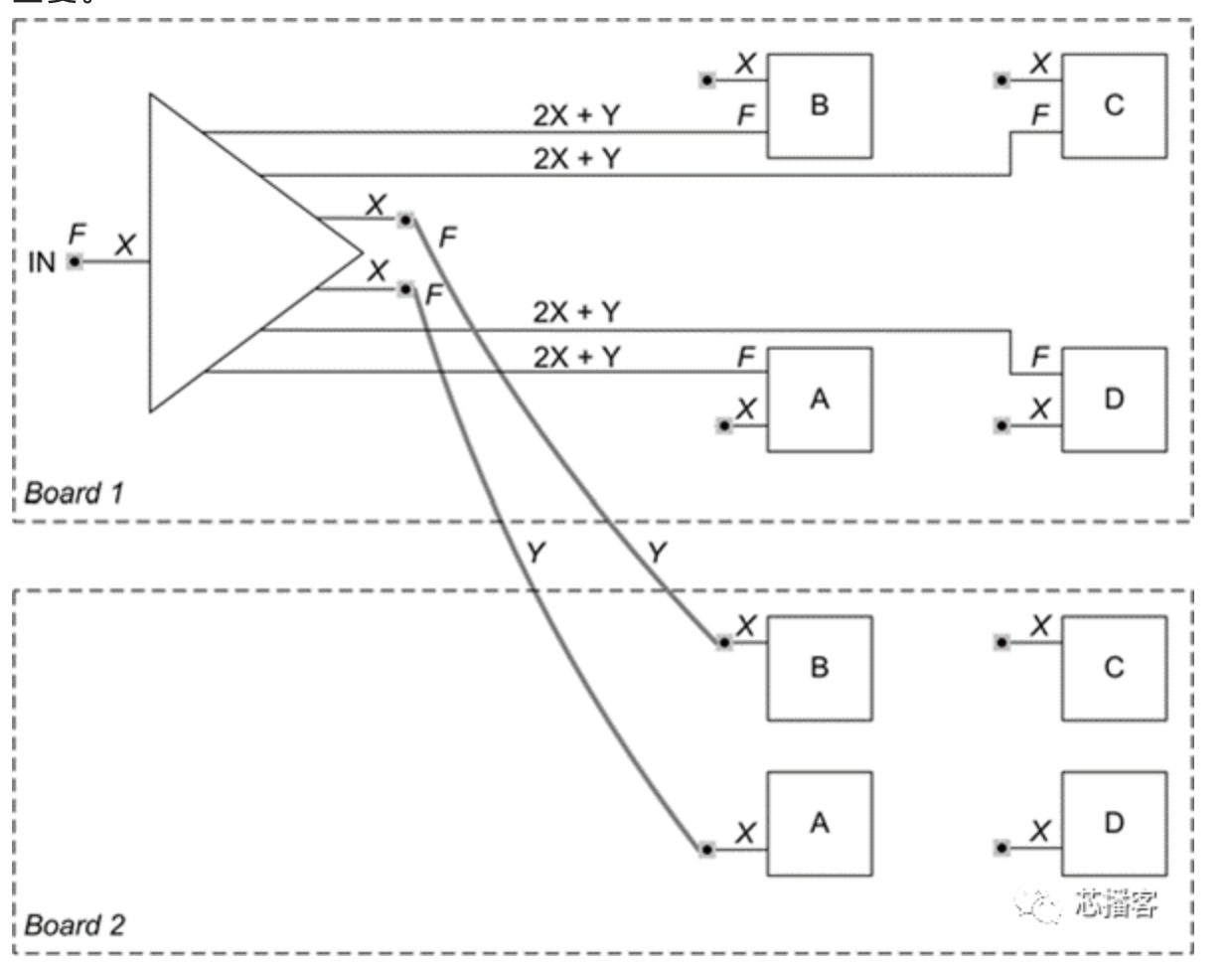

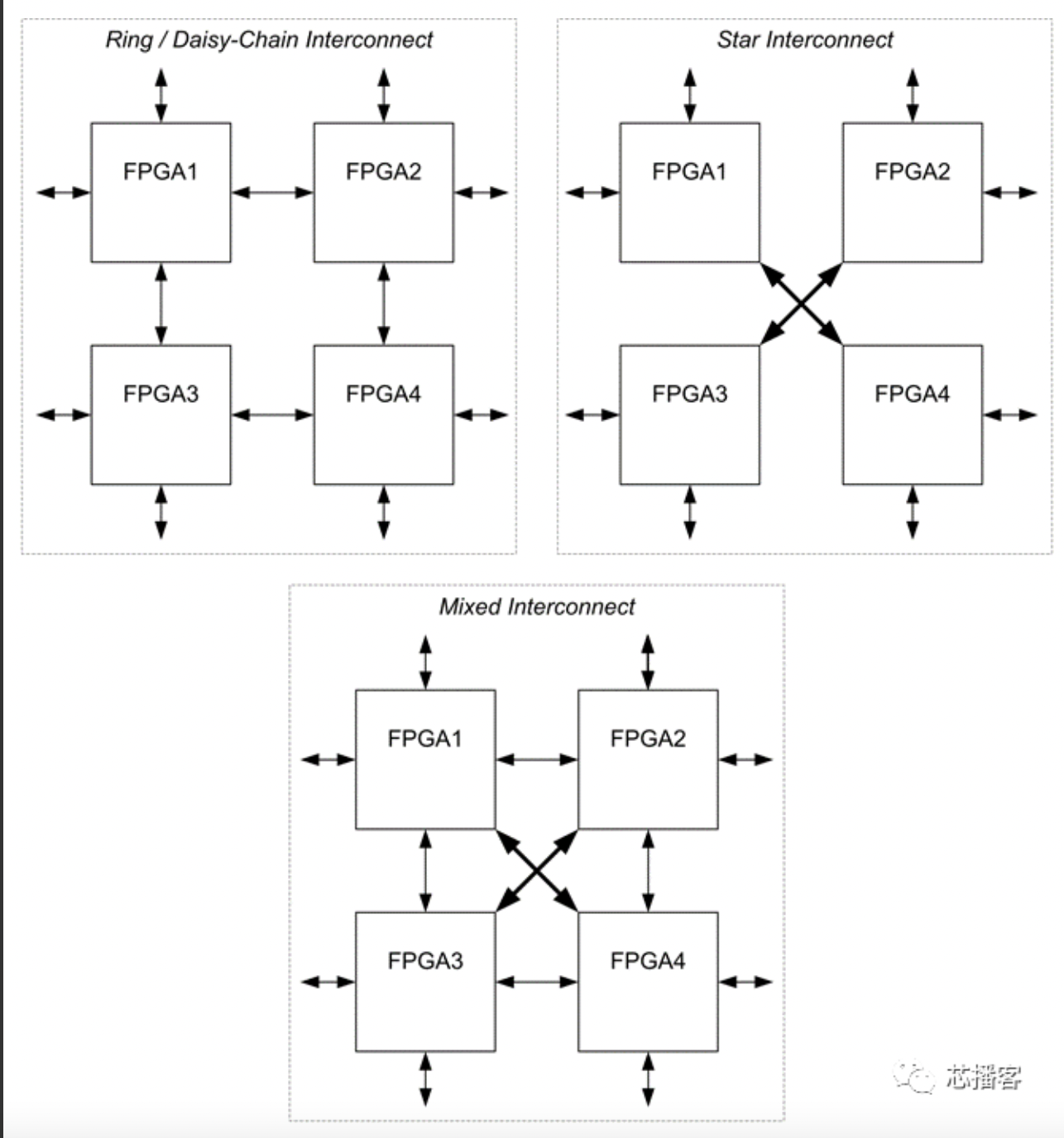

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。而多片FPGA系统的一个最重要的痛点就是...

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流,根据常用的FPGA工具...

如果SoC设计规模小,在单个FPGA内可以容纳,那么只要系统中的FPGA具有所SoC所设计需要时钟的数量,SoC时钟网络将由FPGA中的复杂时...

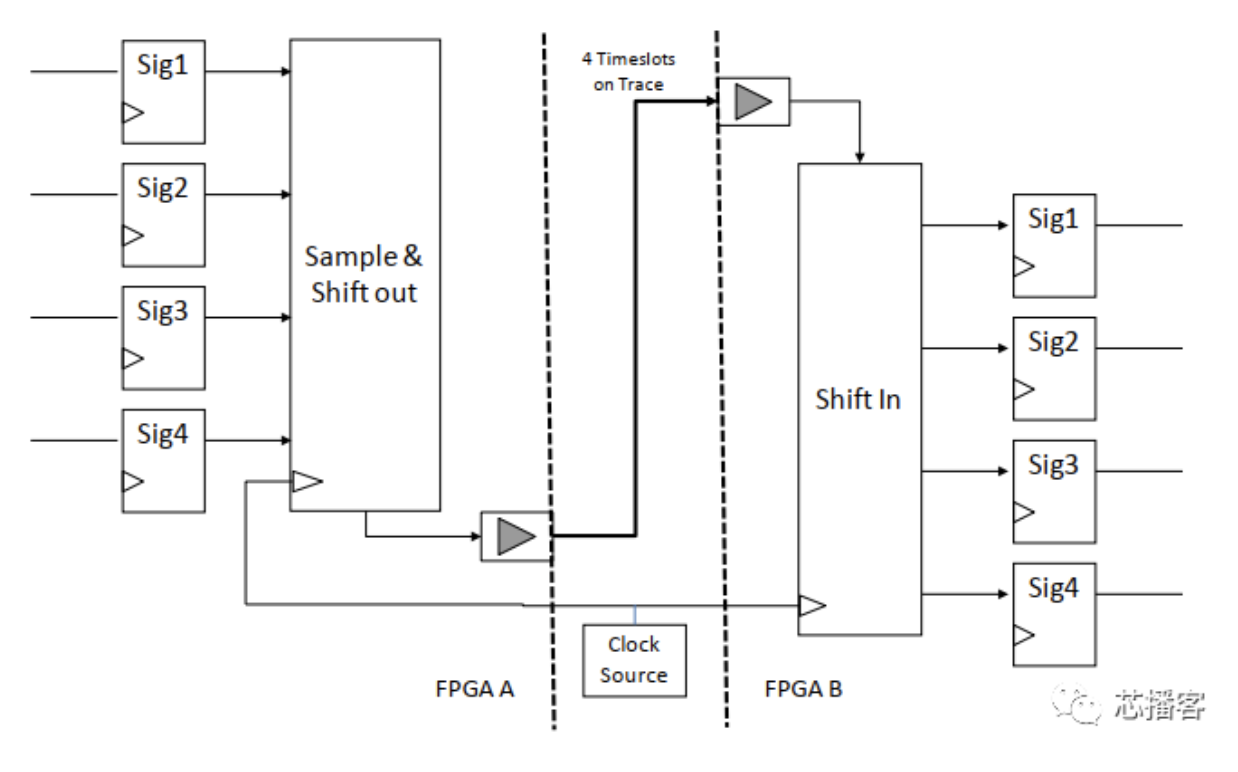

设计中两片FPGA分割边界的数据Sig1、Sig2、Sig3、Sig4……等一大波的信号被并行地加载到传输时钟的上升沿上的移位寄存器中,并用相...

FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。通常,许多SoC中设计的方式在FPGA中其实是不...

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1...

这是新的系列教程,在本教程中,我们将介绍使用 FPGA 实现深度学习的技术,深度学习是近年来人工智能领域的热门话题。

现代FPGA综合工具会自动执行门控时钟转换,而无需更改RTL代码中的设计,然而,我们可能需要适当地手动指导综合工具执行门控时钟...

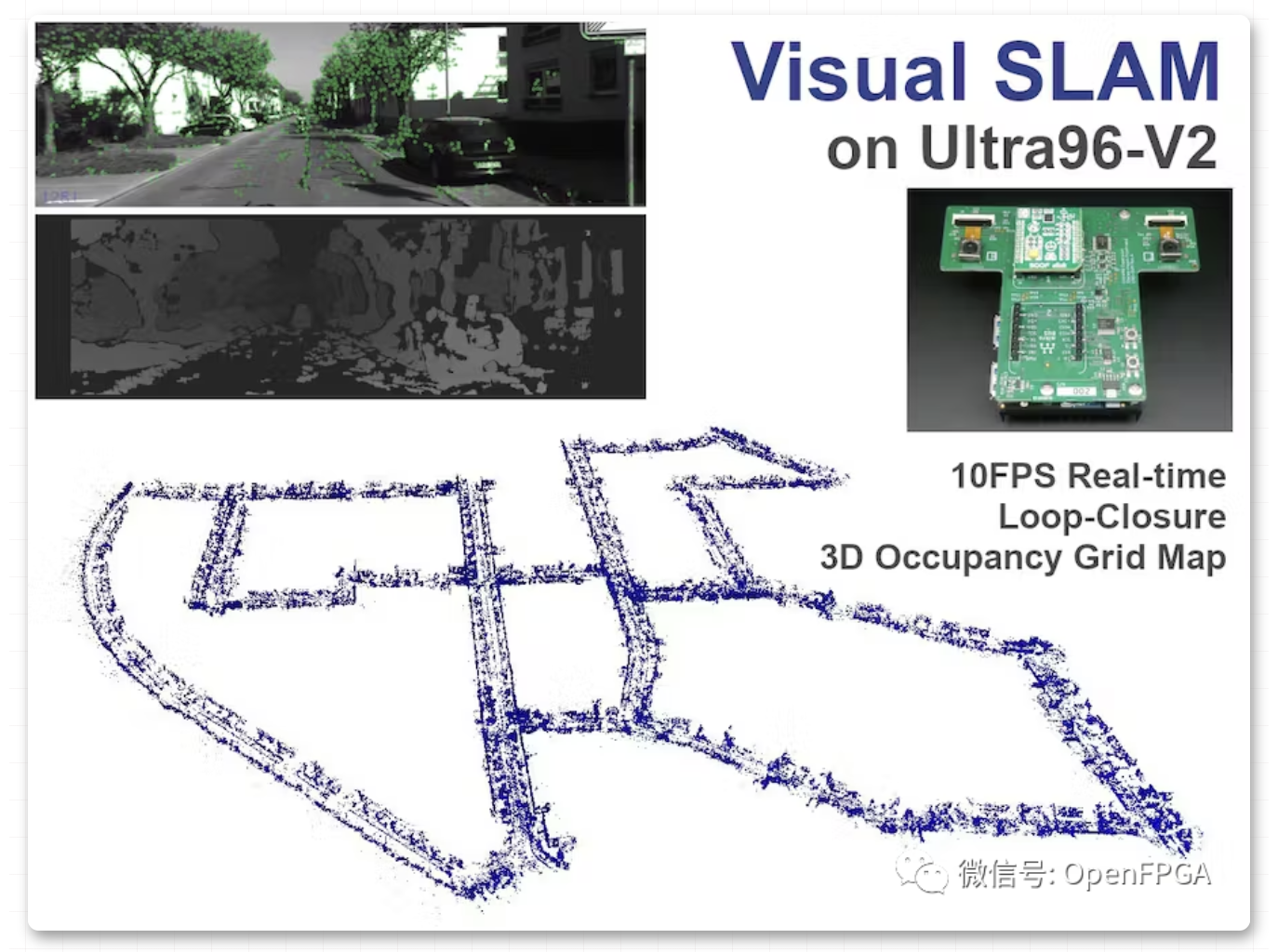

SLAM(同步定位和地图绘制)在自动驾驶、AGV 和无人机等各种应用中引起了人们的广泛关注。尽管目前有很多优秀的 SLAM 项目可以参考,但...