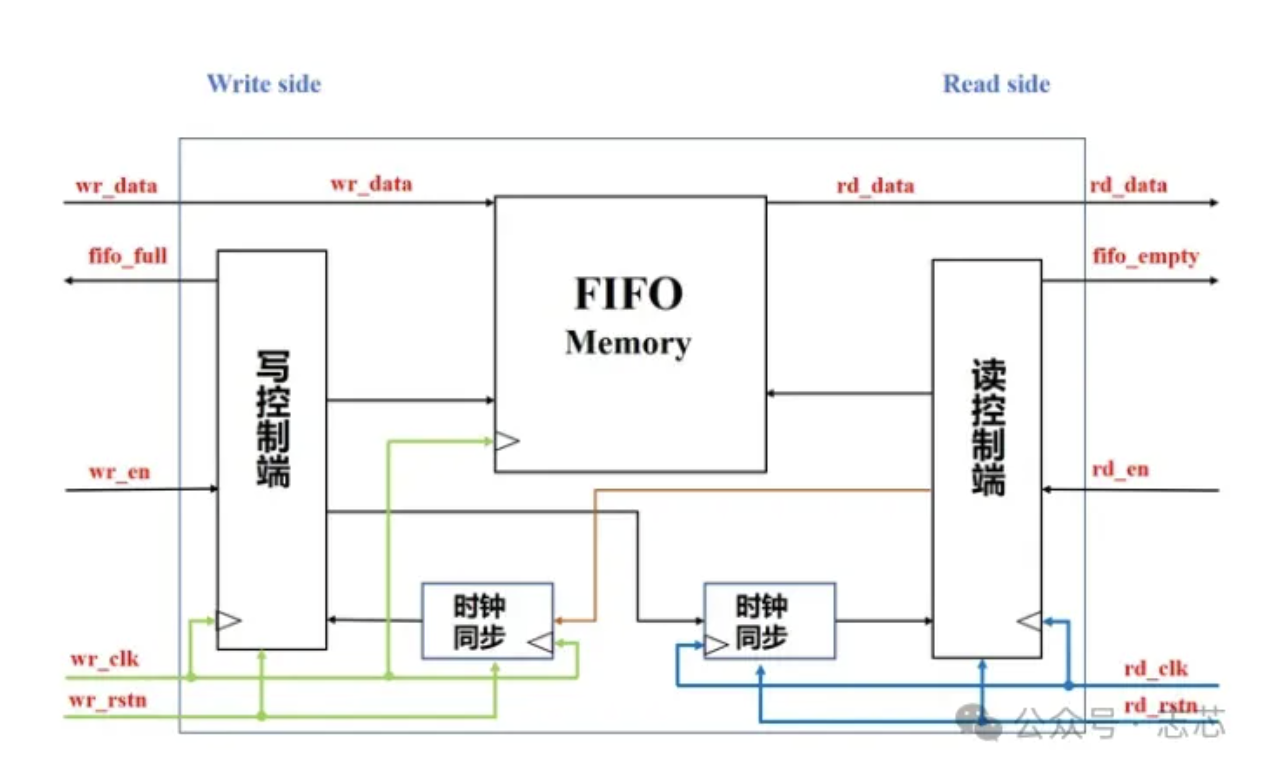

使用异步FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法。在异步FIFO中,读指针在读时钟域,写指针在写时钟域,所以不能...

其实呢,我们在代码全局搜索<font color=red size=4>itr_add</font>是能搜索到好多示例的我们以optee_os/core/arch/arm/pla...

我们可以看出,实际上有四组表,每组表有四个异常入口,分别对应同步异常,IRQ,FIQ和serror。

补充IRQ Domain介绍在linux kernel中,我们使用下面两个ID来标识一个来自外设的中断:1、IRQ number。CPU需要为每一个外设中断编号,我...

1、当一个irq/fiq正在执行时 ,是否可能会其它的irq/fiq打断呢?如果开启了中断优先级,则在irq/fiq进入的时候,也会再次enalbe irq/fiq...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、在linux中的异常向量表(1)、arm64的异常向量表-(irq,fiq,svc......)armv8-ar...

先说答案:NO,或者说定义了FIQ向量,但底层实现就是调用了panic。也就是说在Linux Kernel是无法注册和处理FIQ中断的

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈 我们知道实现中断下半部的机制有三种:软中断tasklet工作队列那么真的就只有这3...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈 目前有三种中断的三种机制:软中断tasklet工作队列1、软中断软中断是一组静态...

我们可以看出,实际上有四组表,每组表有四个异常入口,分别对应同步异常,IRQ,FIQ和serror。

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈★★★ 友情链接 : 个人博客导读首页---点击此处 ★★★在linux kernel中,是如何设置...

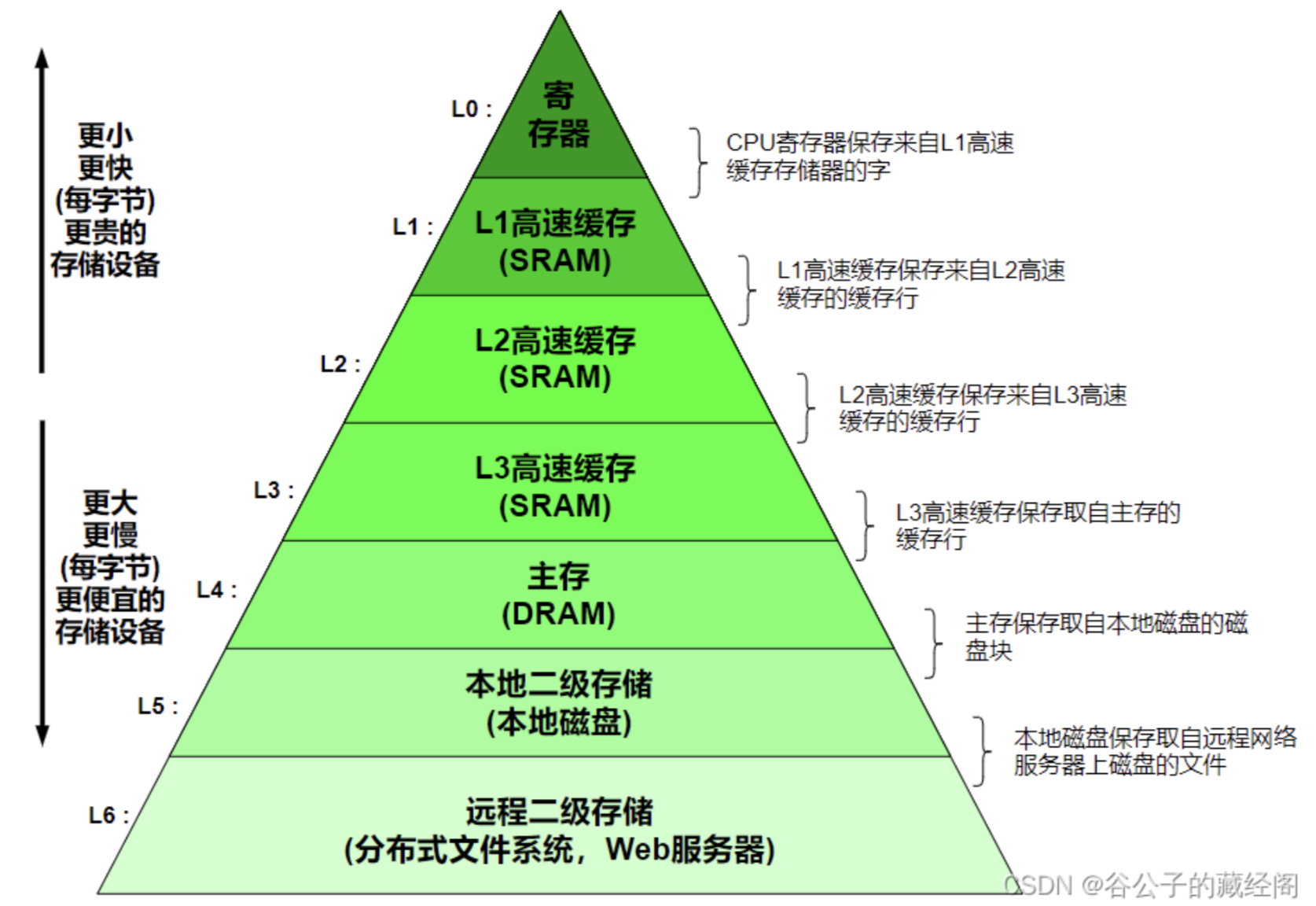

访问memory数据的速度相比core的运行速度来说,要花费更多的时钟周期,为了减轻这个差异引进了存储器层次结构,如图1所示。在层次结构中...

Serror(也称System Error),是异步异常的一种,一般是来自External aborts,当memory system访问时bus上产生的External aborts。例如

说明:在默认情况下,本文讲述的都是ARMV8-aarch64架构,gicv3, linux kernel 5.14

思考:啥是interrupt is asserted ?啥是interrupt is taken ?啥是PE Acknowledge this interrupt ?target 、routing又是什么意思? t...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈原理介绍:废话不多说,看图,看懂的给赞!内核没有提供指定SPIs中断到特定cpu...

具备以下3个行为的称之为同步异常:• The exception is generated as a result of direct execution or attempted execution of an inst...

官方文档原话 :In the Armv8-A architecture, asynchronous exceptions that are taken to AArch64 state are also known as interrupts.

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈当异常进来之后ARM CORE的硬件自动的行为(Exception entry)[for common]PE(即...

那么有三个基地址VBAR_EL1、VBAR_EL3、VBAR_EL1(secure),到底是使用哪一个呢?由Routing when both EL3 and EL2 are implemented 表来...