(AArch64 Exception and Interrupt Handling)异常是指需要特权软件(an exception handler))采取某些操作,以确保系统的平稳运行

如下图所示,左边是51单片机的管脚图,P3.0-P3.5是单片机对应的中断管教,当该管教电平发生变化时,触发cpu异常。当cpu来了一个异常时(...

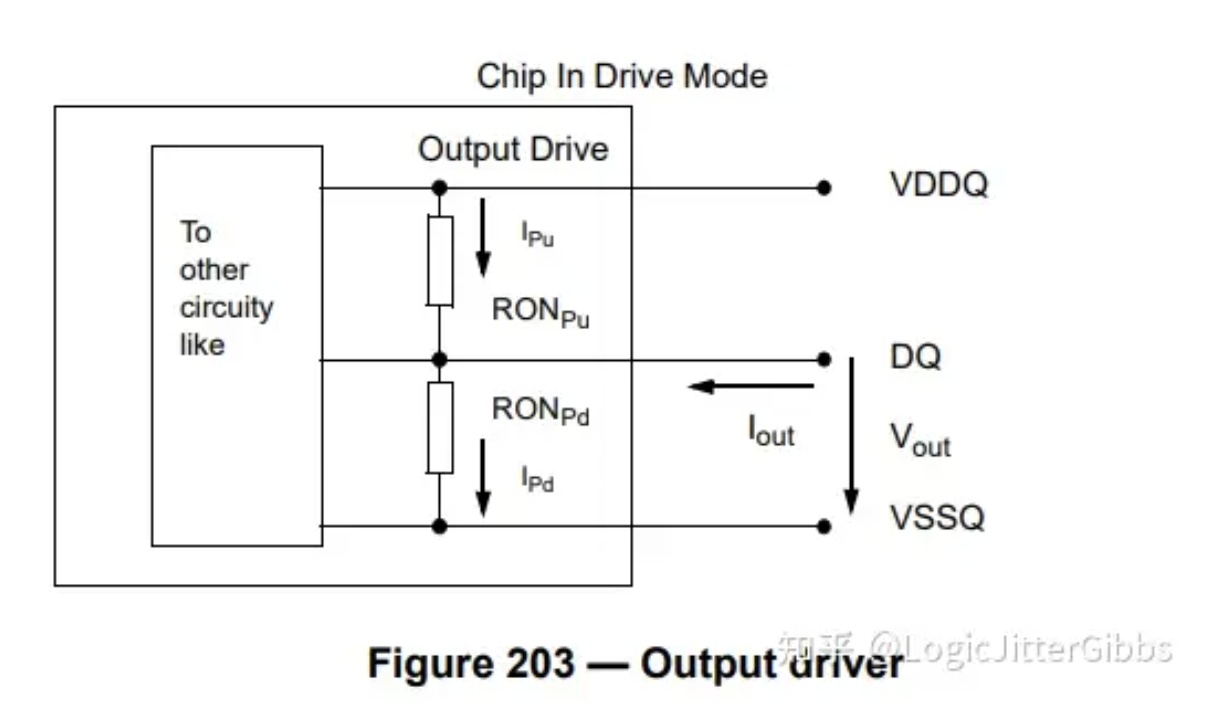

本期我们将基于 DDR4 讨论 DRAM 的 ZQ Calibration 的需求以及相应的 ZQCS/ZQCL 命令。

gicv3寄存器中的banked寄存器:banked by securitybanked by PE

Large numbers of cores on both single-chip implementations and multi-chip implementations

Bypass Indicates that the IRQ signal to the processor is driven by the legacy IRQ signal.

在SOC中,中断产生后,怎么讲信息发送给CPU的呢,如下图所示,画了一个简要说明:ARM CORE只有4根线用于接受中断,nIRQ、nFIQ、nvIRQ、n...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈关注"Arm精选"公众号,备注进ARM交流讨论区。

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、gic概念gic : general interrupt controller(1)、模型(2)、分类GIC中断控制...

背景:随着时代的发展、科技的进步,安全需求的趋势也越来越明显,ARM也一直在调整和更新其新架构,很多都是和安全相关的。如下列出了一...

在linux/optee双系统环境下, linux系统的SCR.IRQ=0、SCR.FIQ=1, optee系统的SCR.IRQ=0、SCR.FIQ=0

不考虑EL3的场景ia,在IMO=1的场景下(physical irq直接target到EL2了)。如果EL1想处理中断,那么必需是EL2转发过来,总之是要经过EL2...

引流关键词: Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU...

以下以GIC的icc_bpr0_el1寄存器为例,我们发现在S-EL1 Security State中无法去写该寄存器....解决方法:查阅该寄存器的伪代码发现,在期...

我们知道在ARM A-profile架构中(armv9.3之前)是不支持NMI中断的,但是操作系统对NMI类型中断又有强烈的需求,那都是怎么玩得呢? 如下便...

Arm A-profile 架构的有一个长期缺陷就是不支持不可屏蔽中断 (NMI) 。2021年,ARM宣布讲支持NMI,所谓支持其实就是看CPU是否支持?GIC是...

normal和secure的cpu_context初始化的时候,SCR_EL3.IRQ = 0, SCR_EL3.FIQ = 0

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、1020-1023号的中断的介绍在gic的文档中,理出了一些特殊的中断号,其中1020/...

在中断流程举例的章节中,图中第1步骤中,给REE的SCR.FIQ=1, 在normal EL0/EL1或EL3时来了一个secure group1的中断,该中断将会被标记为...

在中断流程举例的章节中,有小伙伴仔细读了该篇文章,并产生一些列问题。其中一个问题,一下子把我问到了:“在TEE侧时产生了FIQ,回到RE...