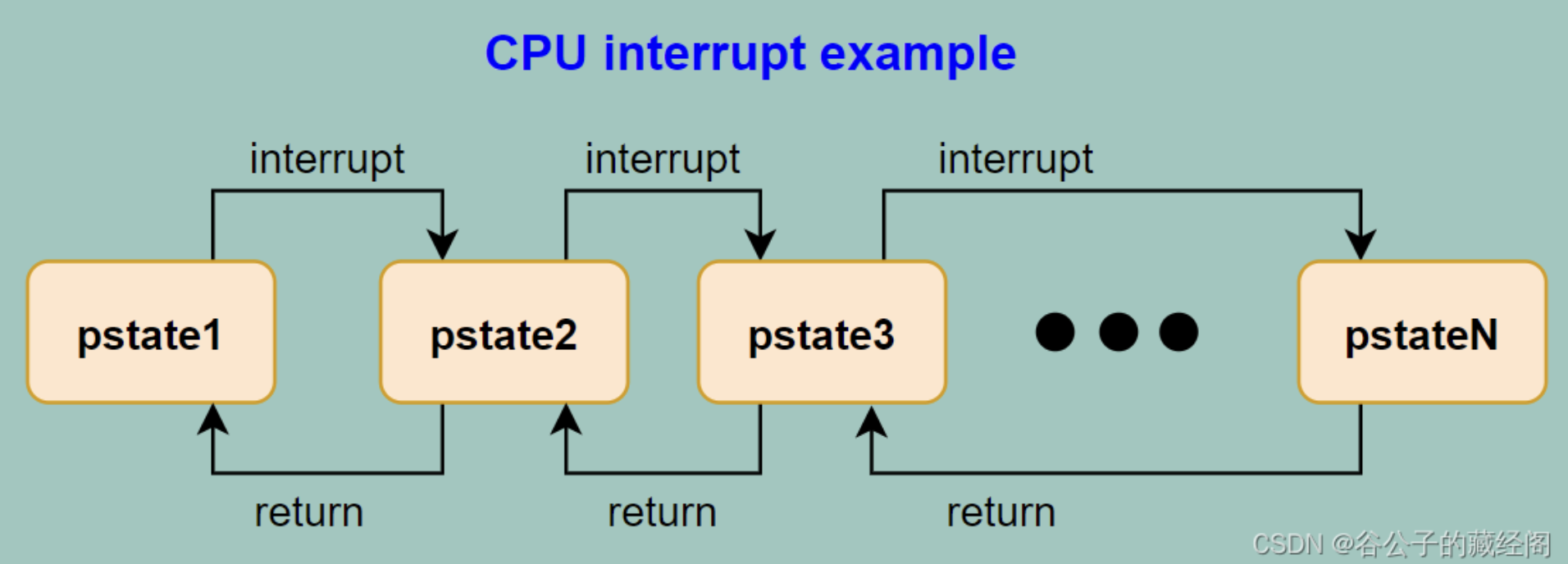

操作系统中可能存在多个任务, 内核调度器周期性地将执行从一项任务转移到另一项任务。在这个过程中,操作系统会保存上一个进程的执行状...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、TCR寄存器介绍在ARM Core中(aarch64),还有几个相关的系统寄存器:TCR_EL1TCR...

Log2 of the number of words in the smallest cache line of all the data caches and unified caches that are controlled by the PE.x

在armv8/armv9的aarch64架构下,软件的启动流程:BL1--->BL2--->BL31--->BL32--->BL33....

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈 (说明本文的介绍都是基于armv8-aarch64或armv9硬件架构)在mmu未开启阶段,PC操...

在学习MMU章节时,我们发现在页表的entry中,BIT[4:2]指向了MAIR寄存器,该寄存器描述了内存属性,其实就是cache的缓存策略属性(inner\...

责任链(Chain of Responsibility)是一种软件行为设计模式,它允许一个操作或命令由多个接收者处理。发送方不是将请求与所有接收方耦合,...

思考1、系统里有多少个MMU? MMU在哪里? 2、一个core里有多少个MMU?多少个Translation regime ? MMU和Translation regime有啥关系?

(Attribute fields in stage 1 VMSAv8-64 Block and Page descriptors)

2022 ARM引入了一种新的控制内存权限方法。 不再是直接在转换表条目 (TTE) 中编码权限,而是使用 TTE 中的字段来索引寄存器中指定的权限...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈TLB里都有什么TLB的查询过程匹配虚拟地址 :使用VA[48:N]去TLB中查询entry匹配t...

引流关键词: SMMU,mmu500,mmu600,mmu700,system mmu,Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee...

(1)、flat map : 一一映射,也就是虚拟地址=物理地址,官方说法是This means that the input virtual address and output physical addr...

本文介绍了 Armv8-A 中的内存模型。 它首先解释描述内存的属性来自哪里以及它们如何分配给内存区域。 然后介绍可用的不同属性并解释内存...

本文介绍了 Armv8-A 中的内存转换,这是内存管理的关键。 它解释了虚拟地址如何转换为物理地址、转换表格式以及软件如何管理Translation...

说明:在默认情况下,本文讲述的都是ARMV8-aarch64、armv9架构,linux kernel 5.10,optee3.14, TF-A 2.5

引流关键词: Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU...

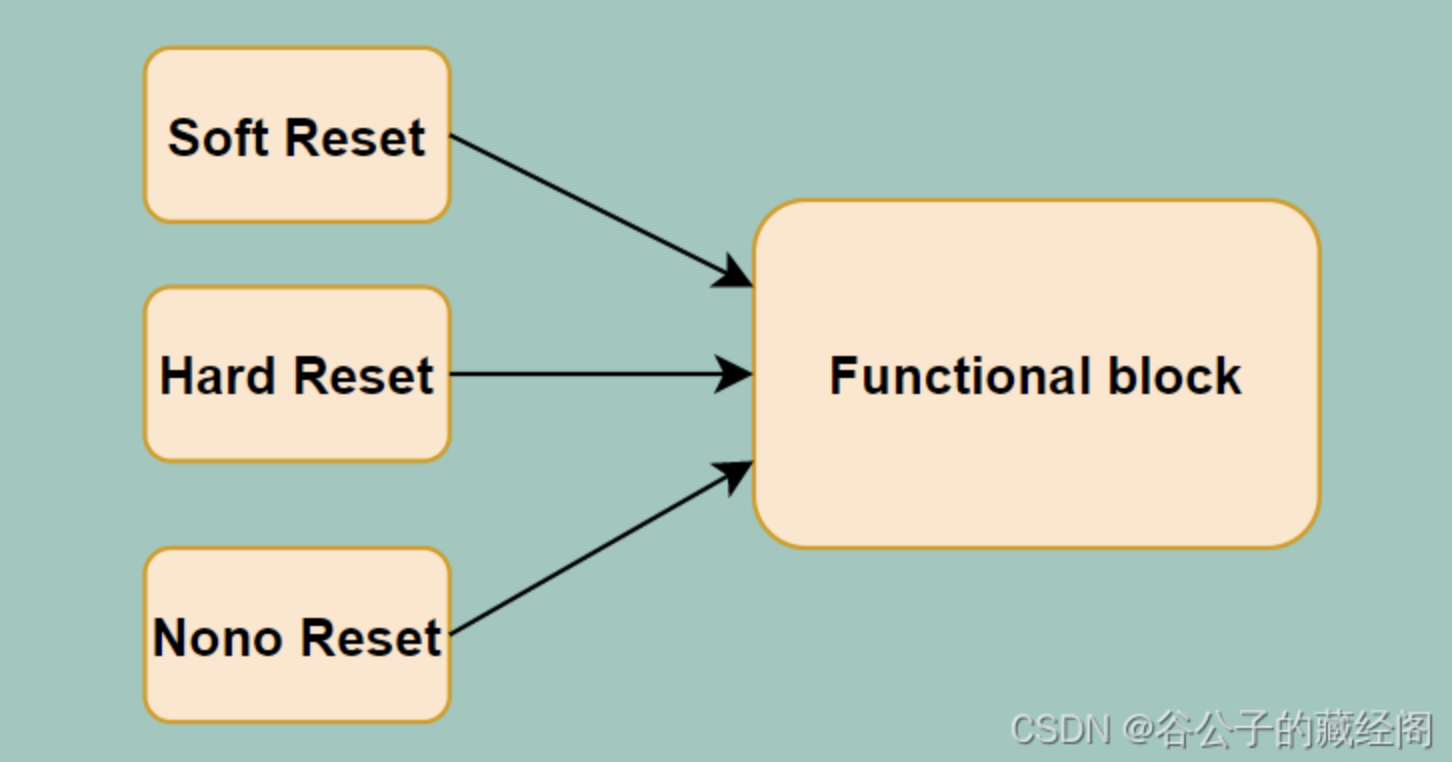

软件设计模式定义了一组类和它们之间的关系,它们相互作用用以解决软件开发过程中面临的常见问题。由于验证工程师所做工作的重要部分包...

引流关键词: 内存屏障, DSB,DMB,ISB,inner,outer,memory barrier,Non-cacheable,Cacheable, non-shareable,inner-shareable,outer-share...

关键词: Non-cacheable,,Cacheable, non-shareable,inner-shareable,outer-shareable, optee、ATF、TF-A、Trustzone、optee3.14、MMU、V...