今天写东西的时间有限,我是想跟大家分享一份来自OCP ODSA(Open Domain-Specific Architecture)的白皮书《BUSINESS ANALYSIS OF CHIPL...

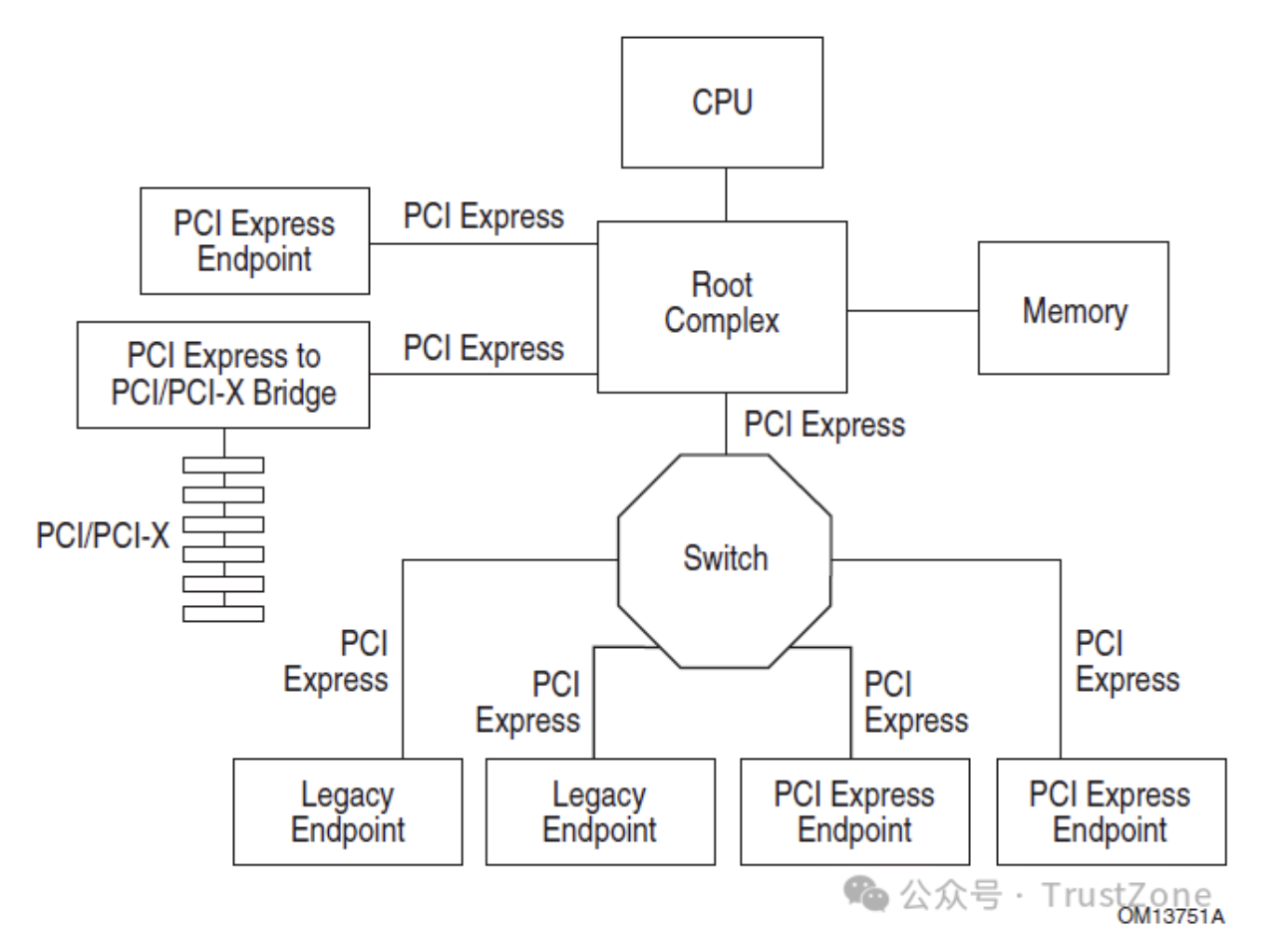

在上一篇中,我们简单的介绍了PCIe的总体架构,PCIe基础概念与设备树,并且了解了如何通过lspci命令和Windows下的设备管理器来查看PCIe...

导言本次更新完虚拟机后,下次更新估计得等到下一次了,应该不会是最近。「更新特点:」1、解决新版本软件启动慢的问题2、一改以往只安...

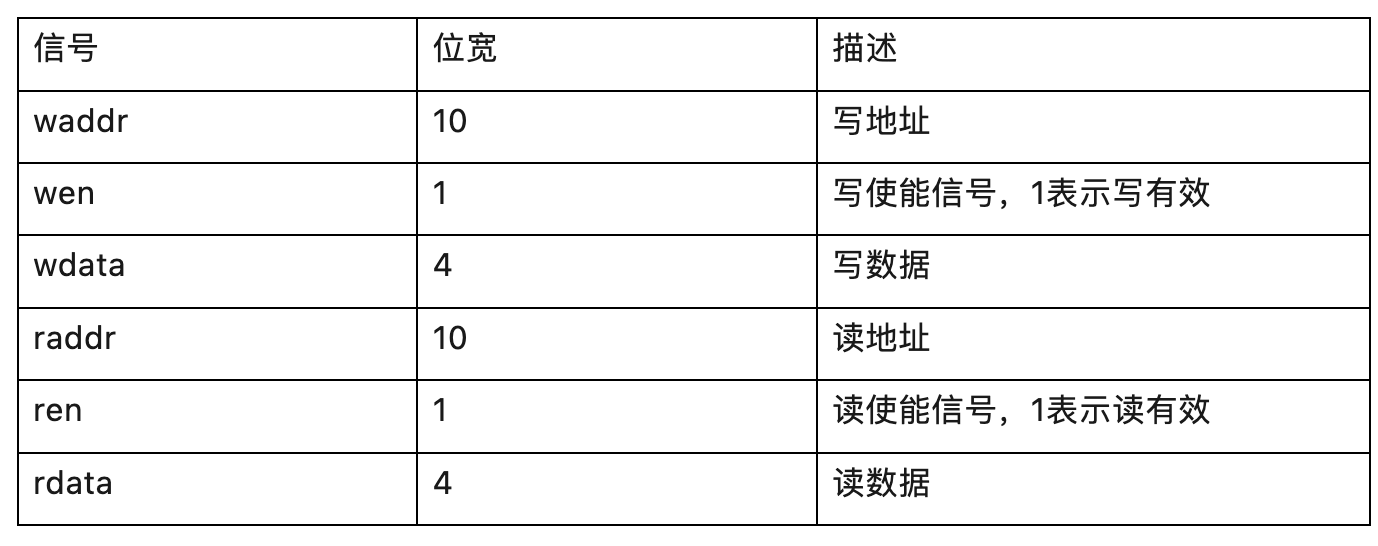

在IC设计中,我们有时会使用深度很大,位宽很小的ram。例如深度为1024,位宽为4bit的ram。此类的ram有个明显的缺点:形状狭长,不利于布...

PCIe的全称是Peripheral Component Interconnect Express,是一种用于连接外设的总线。

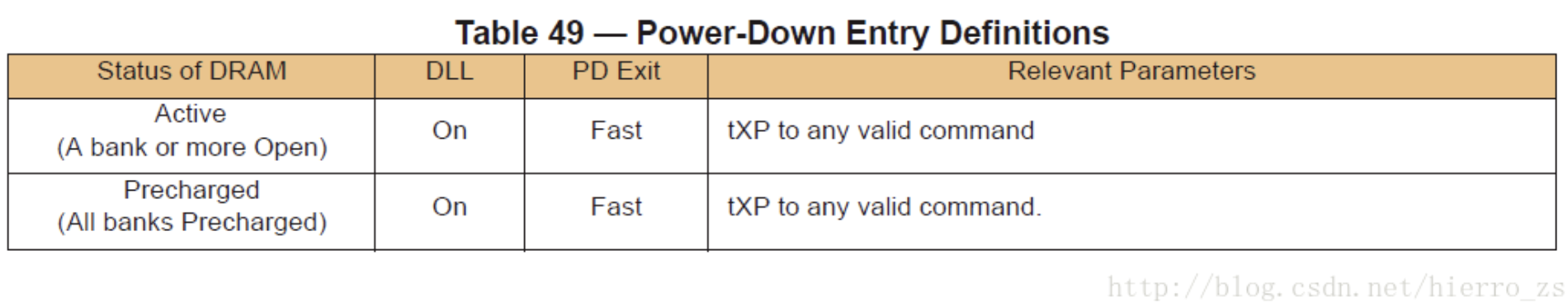

在DRAM执行DES命令时,若CKE为低电平,那么此时DRAM就会同步的进入断电(PD)模式。在MRS命令,PR操作,ZQCAL操作, DLL锁定中或读写操作...

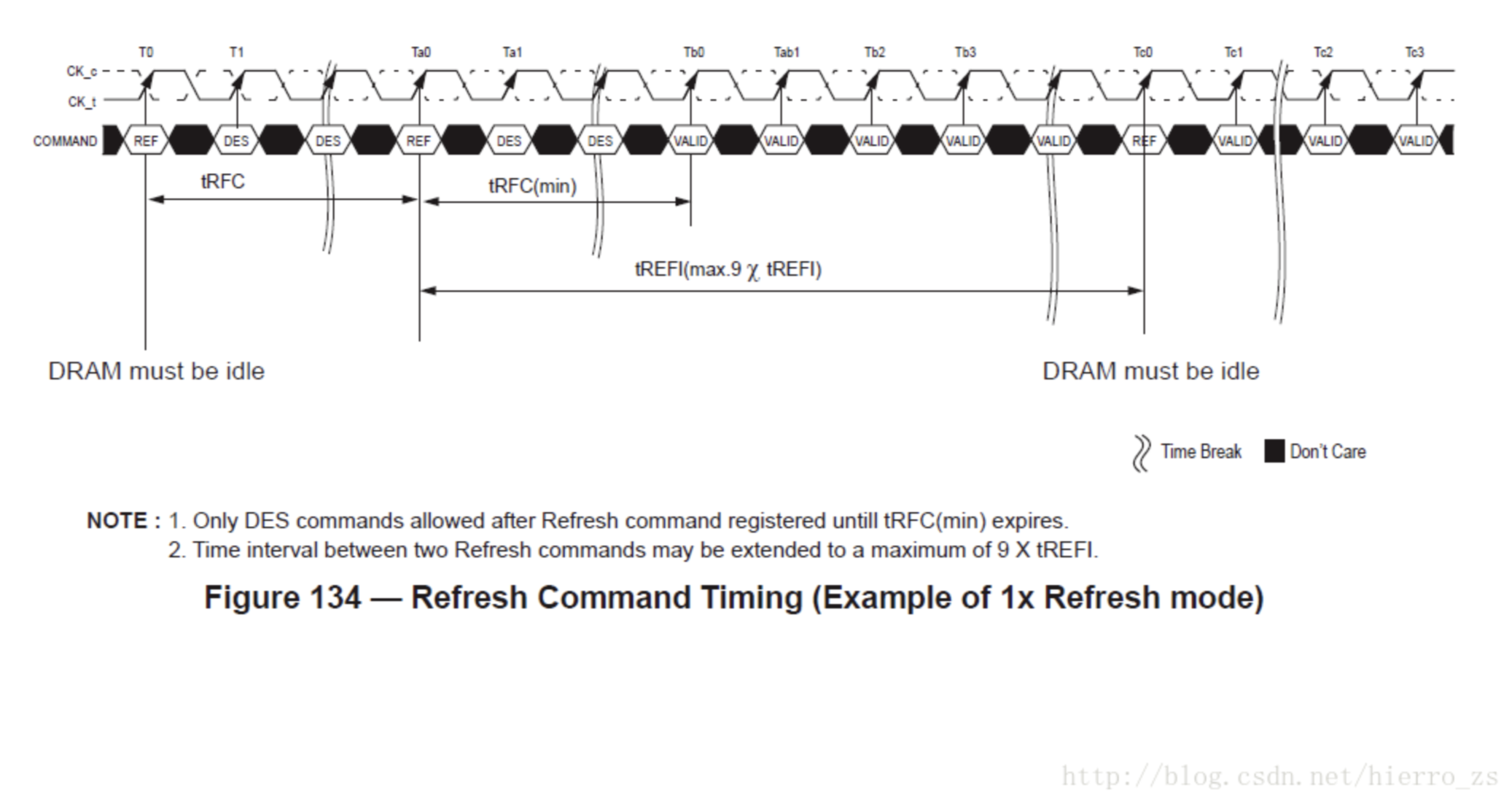

在DDR4 SDRAM中刷新命令是在不同的操作中使用的。此命令并不是一直持续的,因此控制器必须在需要刷新的时候向DRAM发送REF命令。DDR4 SDR...

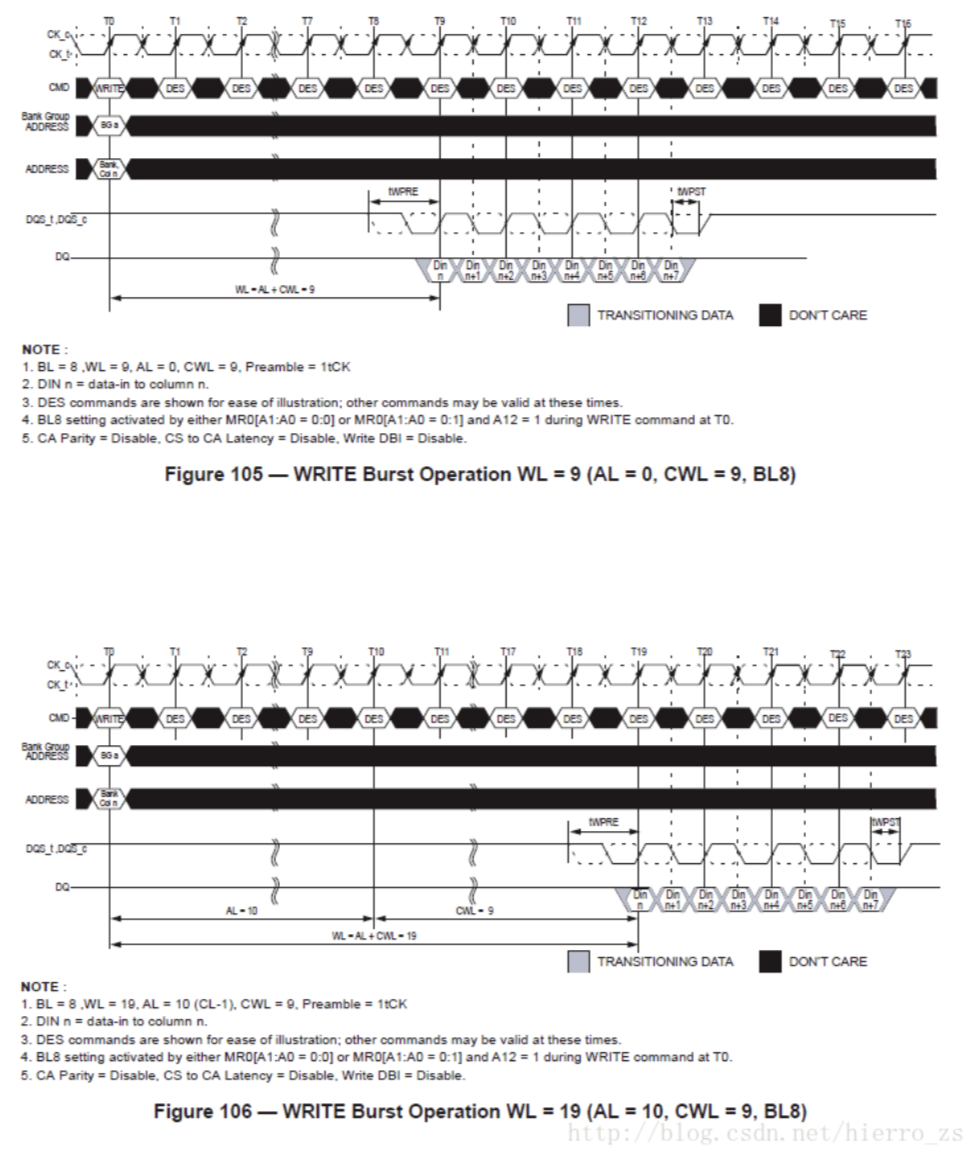

下面的例子仅为帮助理解写操作中各个参数的含义,每个参数的实际定义在后面文章中会有单独的描述。为了说明方便,在下图中,CK与DQS都是...

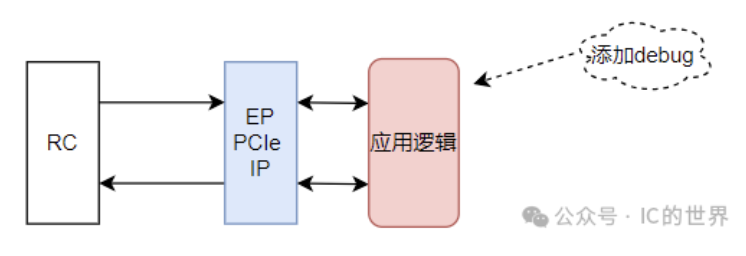

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相...

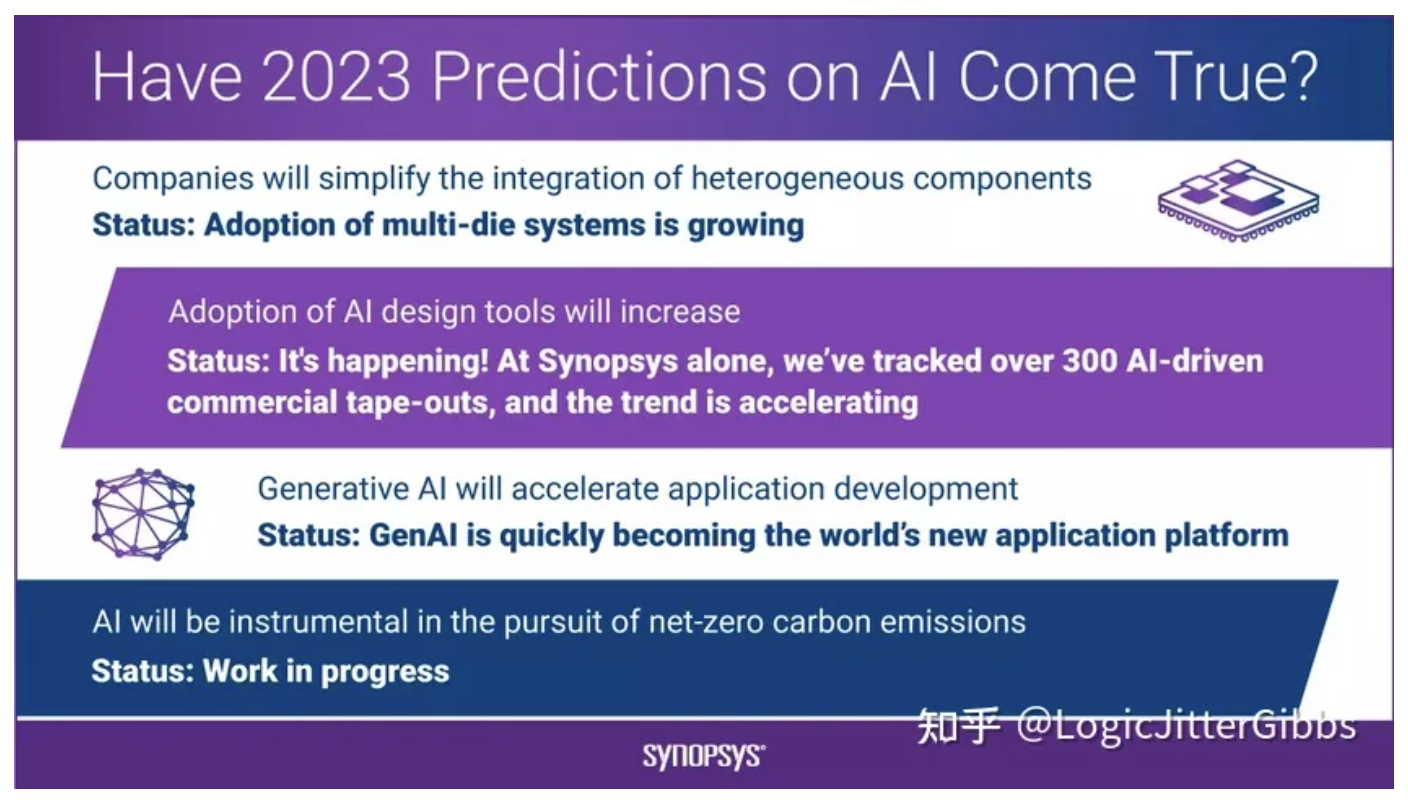

它已经正式确认!在不到一年的时间里,生成式人工智能(GenAI)已经以创纪录的速度达到了 Gartner’s Peak of Inflated Expectations。然...

本系列文章会搬运新思有关 DDR 相关技术白皮书与 IP 技术公告,这些文章有不错的主题和靠谱的内容,并且很多是翻译成中文的版本。

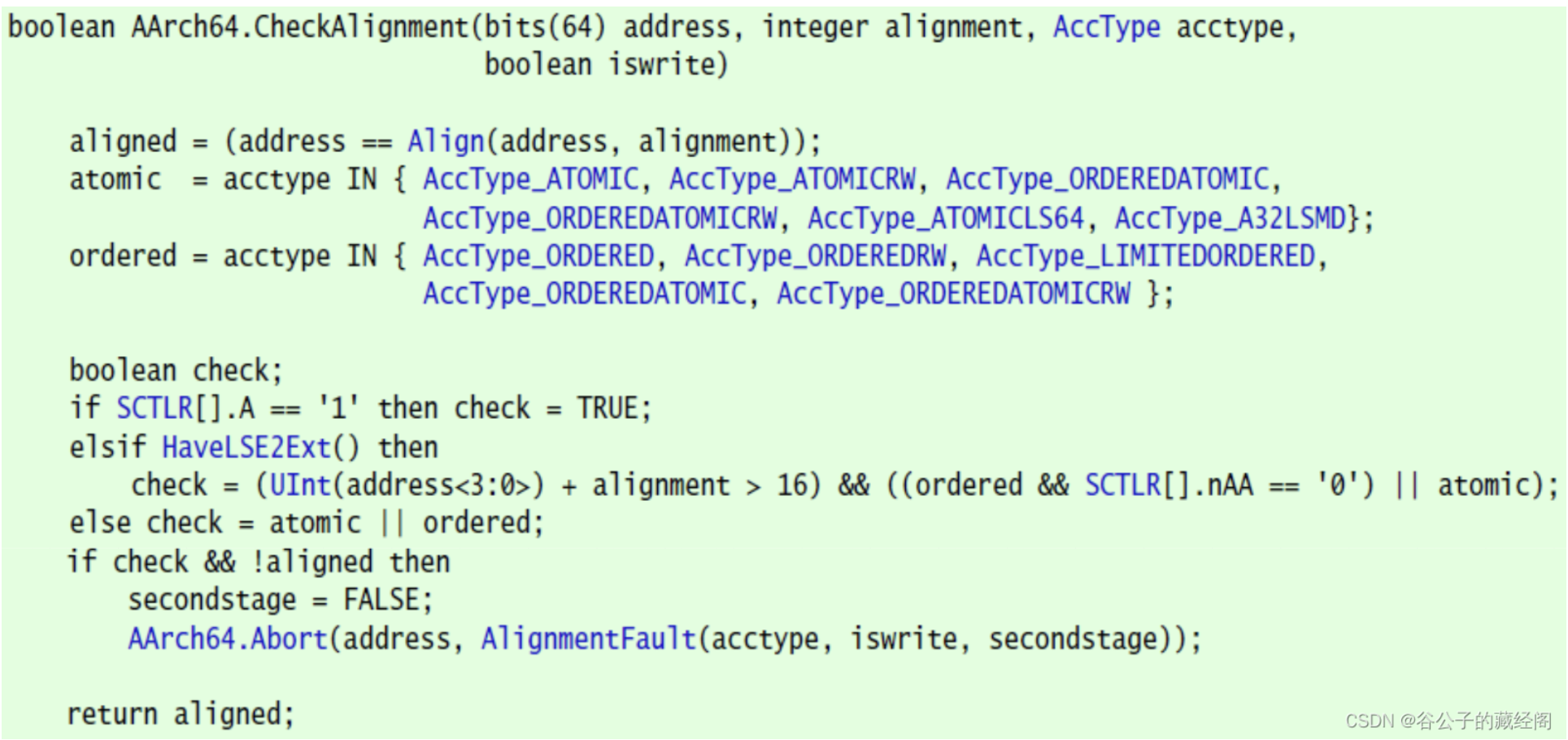

数据和指令必须与合适的边界保持对齐(alignment)。访问是否对齐会影响ARM核的性能,并且在将代码从早期的体系结构移植到ARMv8-A时可能会...

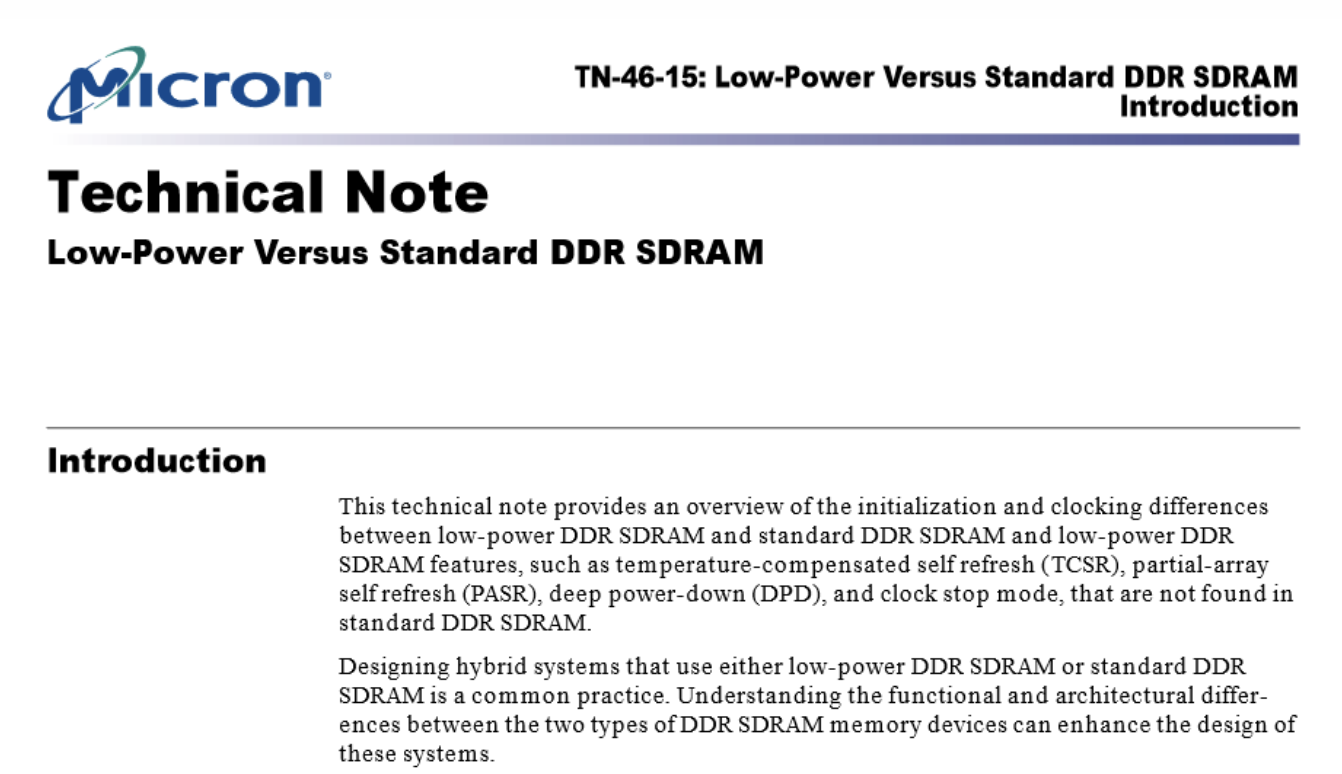

本期我们学习美光的一篇文章,关于低功耗 DDR,即 LPDDR 和标准 DDR 的对比介绍,本文是对这篇文章粗略翻译。

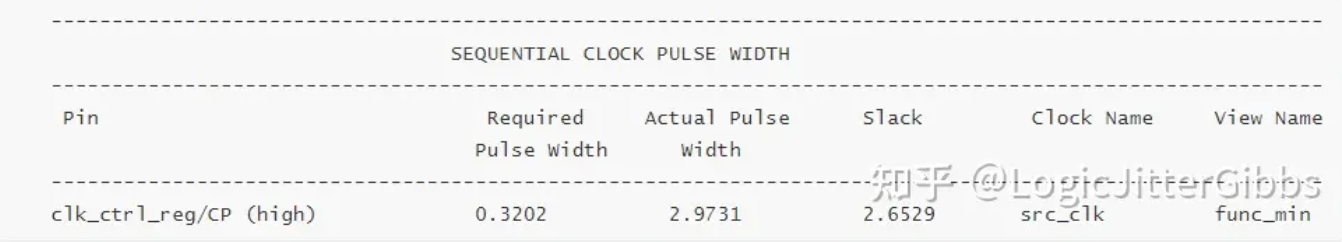

Minimum Pulse Width 最小脉冲宽度检查是为了确保时钟信号的脉冲宽度足够宽,使 cell 内部操作能够完成。也就是说,为了获得 cell 上稳...

本节基于 DFI 协议 4.9 节(协议 4.0 版本)讨论 DFI PHY 时钟频率与 DFI 时钟多倍频率比的架构、地址控制/写数据/读数据信号行为。

本文是由论坛网友在EETOP博客分享的模拟IC工作心得,感觉非常不错,现通过微信文章分享给大家。 博客地址:[链接]正文:在学校的时候,...

极术读书是极术社区推出的读书栏目。极术读书专栏定期推荐嵌入式,人工智能,物联网,云计算,安全,半导体等智能计算领域的图书及技术...

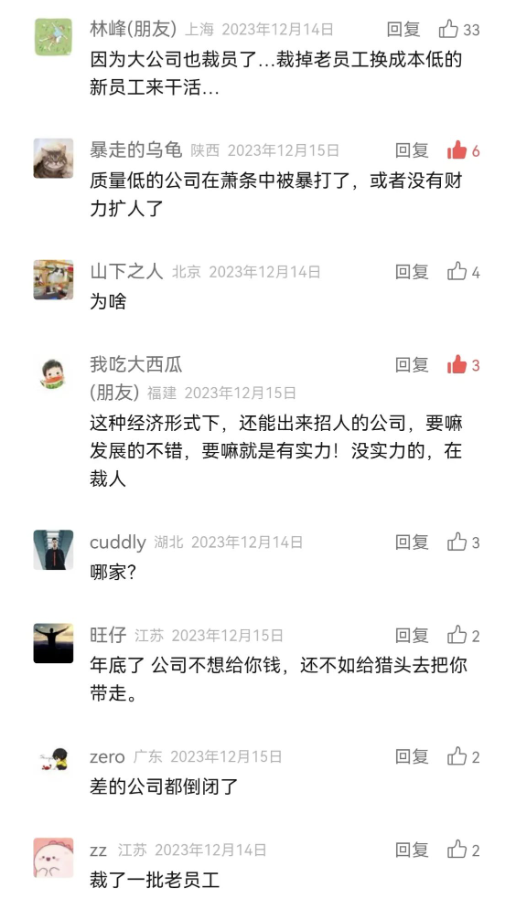

在2023年的12月,我注意到一个有趣的现象:猎头推荐的公司的质量明显提高了。这引起了我的好奇,于是我在社交媒体上发起了讨论,询问大...

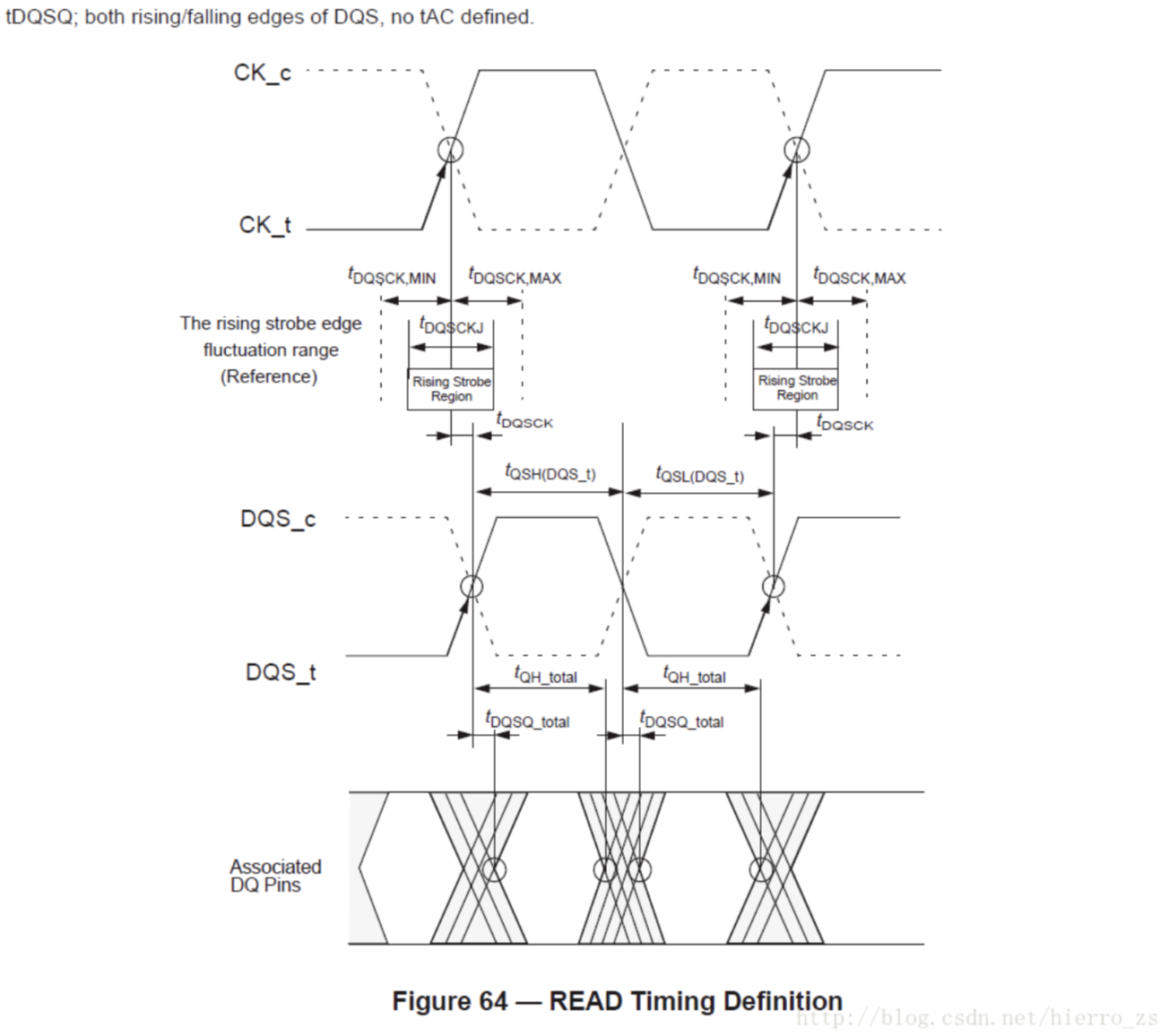

4.24 读操作4.24.1 读时序定义此章节中描述的读时序参数可在DLL锁定或未锁定的状态下使用。读选通信号上升沿参数:tDQSCK min/max描述了...

随着春节的脚步越来越近,许多身处四面八方的工程师们开始踏上归家的旅途,心中充满了对家人团聚的期待和对过去一年工作成就的回顾。在...