引流关键词:缓存,高速缓存,cache, CCI,CMN,CCI-550,CCI-500,DSU,SCU,L1,L2,L3,system cache, Non-cacheable,Cacheable, non-shareable,i...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1. 思考和质疑在一个大架构大系统中,有哪些一致性需要维护?我们先看如下一张...

高速缓存控制器(cache controller )是负责管理高速缓存内存的硬件块,其方式对程序来说在很大程度上是不可见的。它自动将代码或数据从主...

cache是多级的,在一个系统中你可能会看到L1、L2、L3, 当然越靠近core就越小,也是越昂贵。一般来说,对于big.LITTLE架构中,在L1是core...

ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然而...

带着问题去学习,关于cache的一些思考:1、L1/L2/L3 cache到底在哪里?L1/L2/L3 cache分别都是多大?2、L1/L2/L3 cache的组织形式都是怎...

ARMv8有31个通用寄存器X0-X30, 还有SP、PC、XZR等寄存器下面详细介绍写这些通用寄存器(general-purpose registers):

引流关键词: optee、ATF、TF-A、Trustzone、optee3.14、MMU、VMSA、cache、TLB、arm、armv8、armv9、TEE、安全、内存管理、页表…

想不想一夜暴富?拥有很多很多钱,买很多很多房,工作也不忙,无压力,不用亲自Coding和Debug,还有大把大把的时间在CSDN上挥霍...... ...

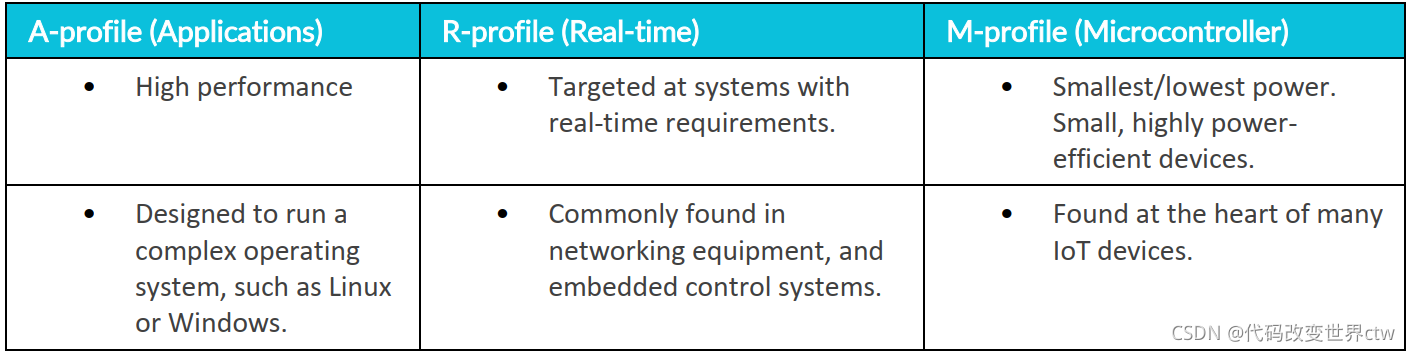

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录👈👈👈1、简介 & 概述ARMv8/ARMv9架构入门到精通-[前言] ---- 必看armv8/armv9的简介-...

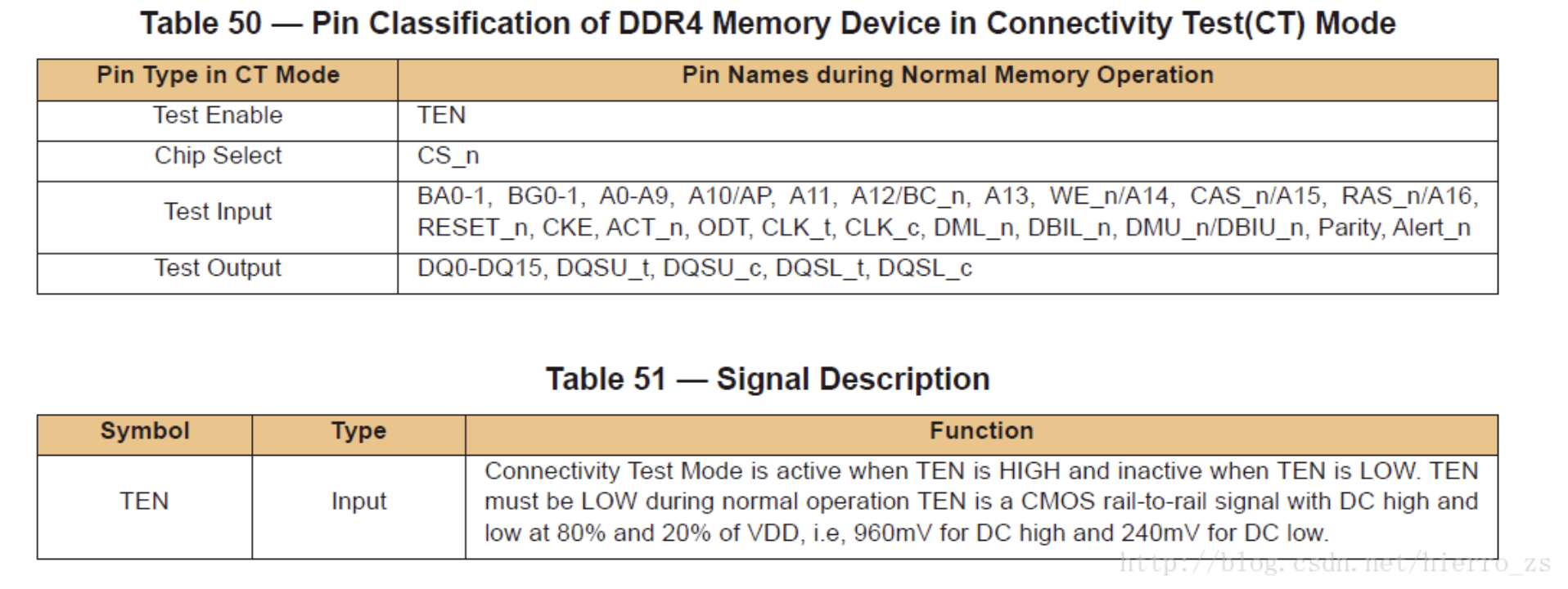

DDR4 SDRAM支持一种连接性测试模式(CT),此方法可大大提高测试PCB上SoC的DDR控制器与DRAM之间连线的电气连接性测试。此模式可与边界扫...

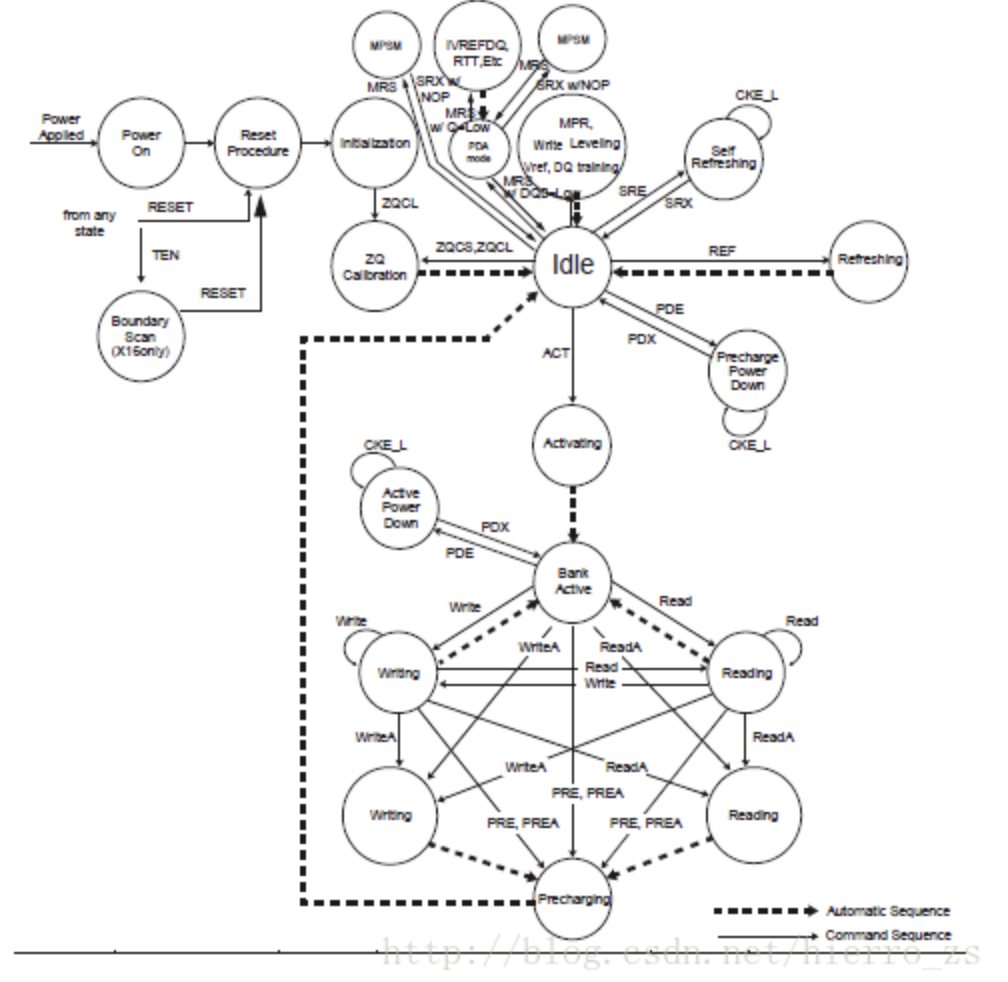

NOTE 此简化的状态机仅提供可能的状态转换与命令控制的概观。尤其,打开多bank与使能ODT等其他的操作的细节是没有包含进来的。

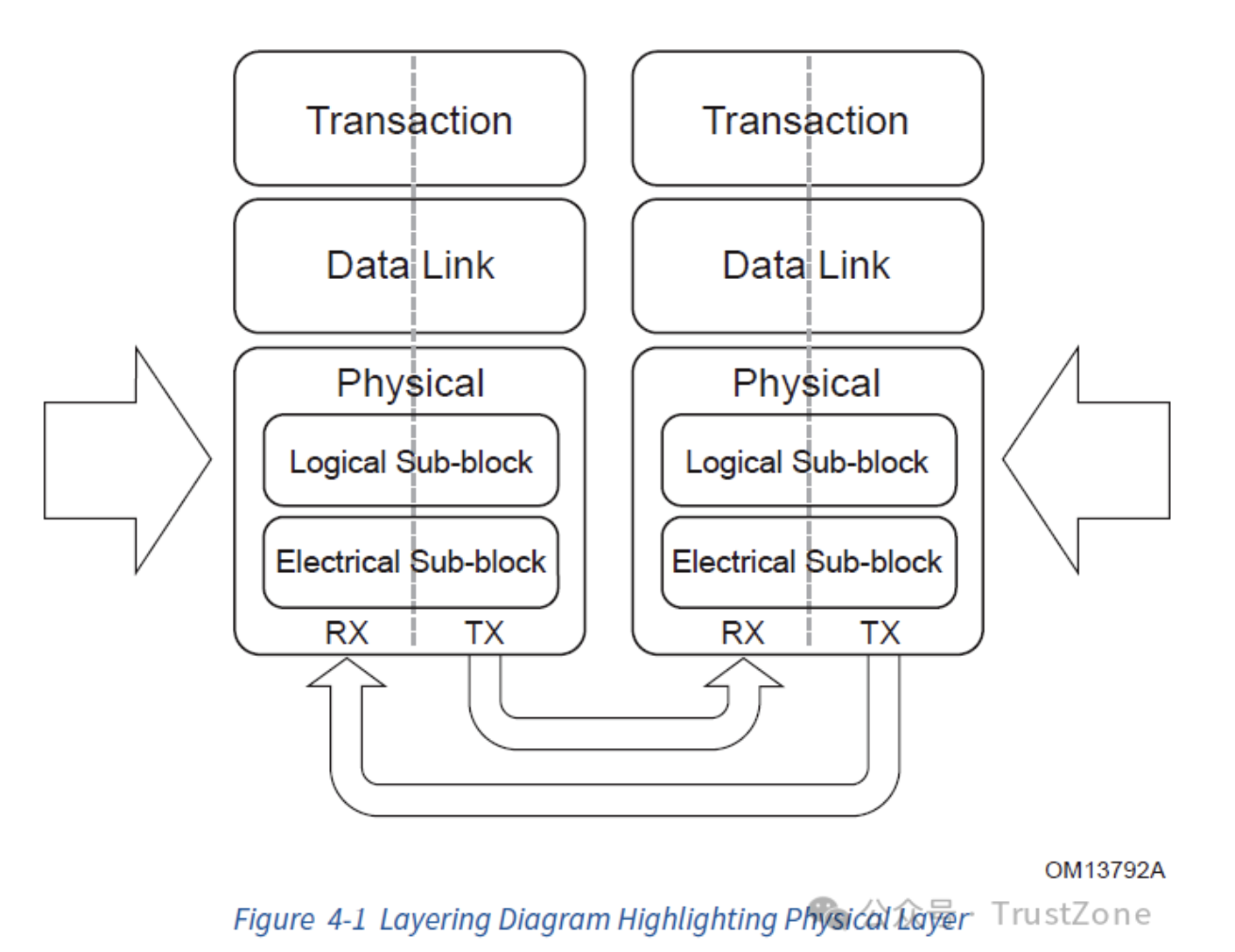

在上一篇中,我们介绍了PCIe设备的配置空间,及其设计的目的,最后我们说到了消息路由的设计。所以,这一篇我们就继续这个话题,来看看P...

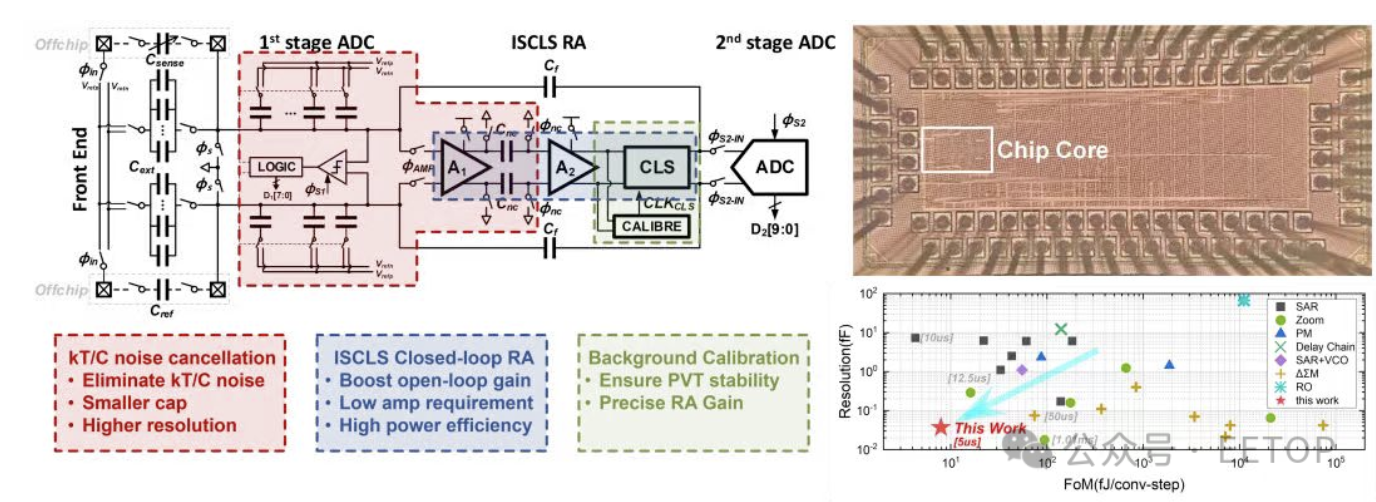

2月18日-22日,国际固态电路会议(ISSCC2024)召开。北京大学黄如院士-叶乐教授团队的论文(Jihang Gao, Linxiao Shen, Heyi Li, Siyuan...

SerDes,即Serializer(串行器)和Deserializer(解串器)的简称,是一种高速串行数据传输技术。

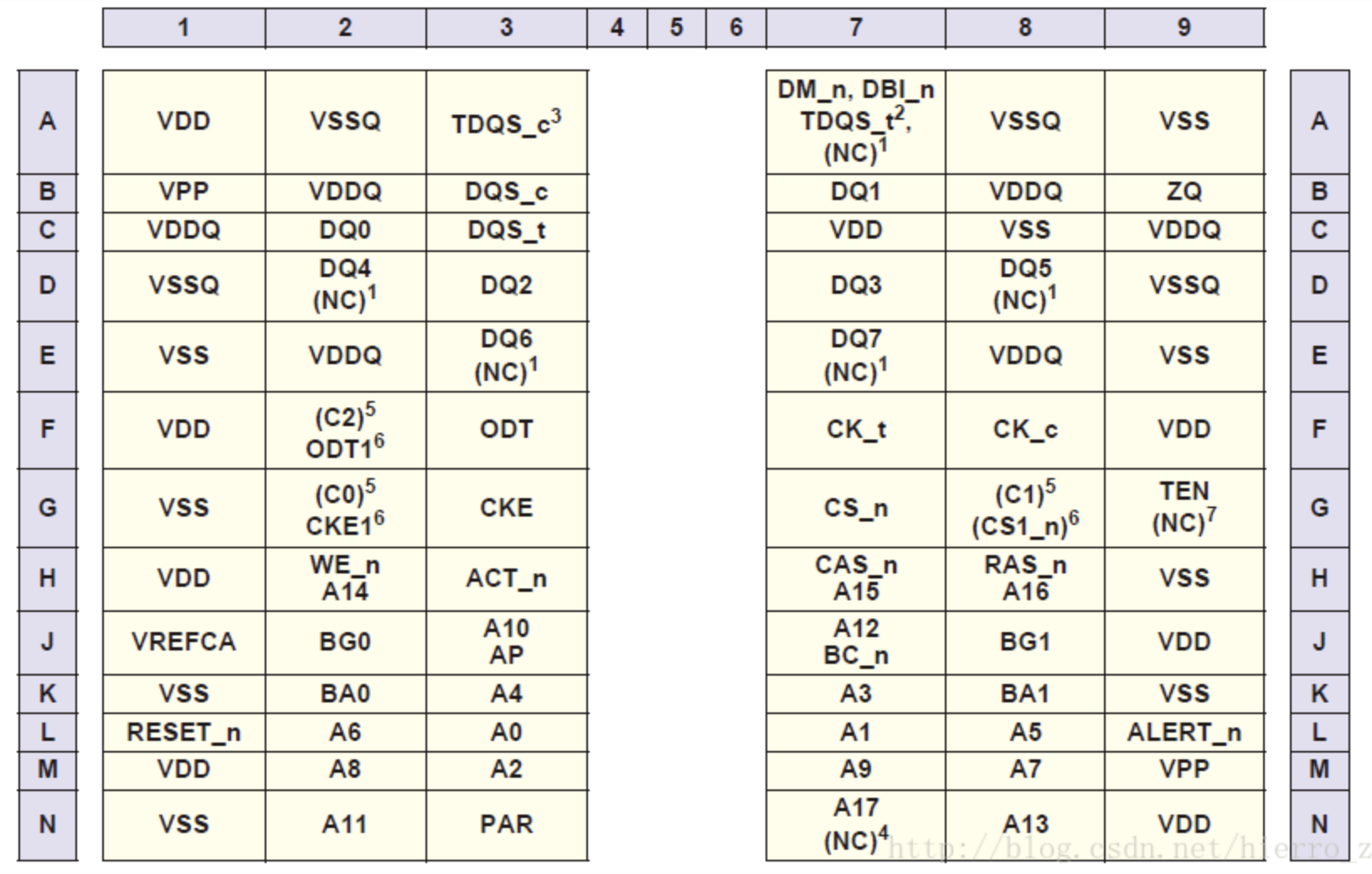

此文档为DDR4 SDRAM的使用说明书,包含了DDR4 SDRAM的特性、功能、AC与DC特性、封装与出球分布。此标准的目的为定义从2Gbit到16Gbit的x4...

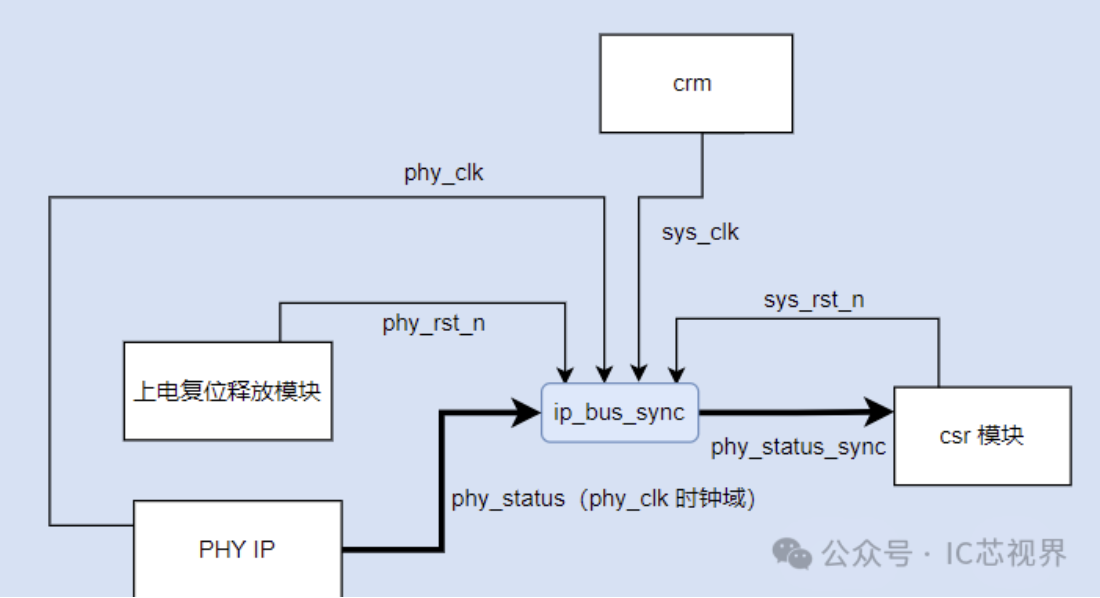

本文将介绍一个跨时钟错误的案例如图所示,phy_status作为一个多bit的phy_clk时钟域的信号,需要输入csr模块作为一个可读状态寄存器,目...

上周我分享了一份白皮书《基于Chiplet的商业分析-系统与技术》,其实是因为接下来还想发更多的资料。Chiplet Summit会议资料 (2024&2023...

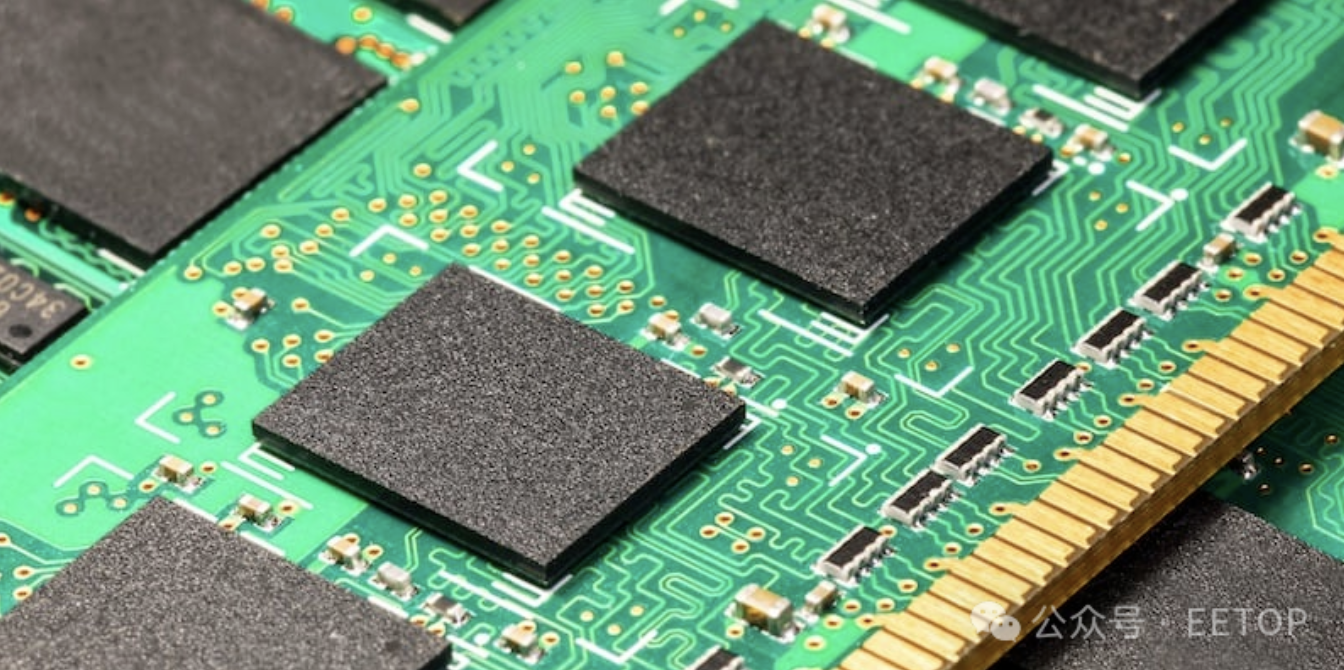

在最近的 IEEE 国际固态电路会议 ( ISSCC ) 上,三星科学家发表了一篇论文,继续推动 DDR5 性能的进步。

以下内容节选自《从拆解 Model3 看智能电动汽车发展趋势》报告中域控制器部分章节。这份报告是中信证券研究部TMT和汽车团队联手多家公司...