我们常用的debug UVM的方法是通过打印log实现。有没有办法像 debug RTL代码一样将 UVM 中变量拉到波形上看呢?答案是有的,下面让我们看...

前言本次讲一下UVM中的uvm_config_db,在UVM中提供了一个内部数据库,可以在其中存储给定名称下的值,之后可以由其它TB组件去检索。这样...

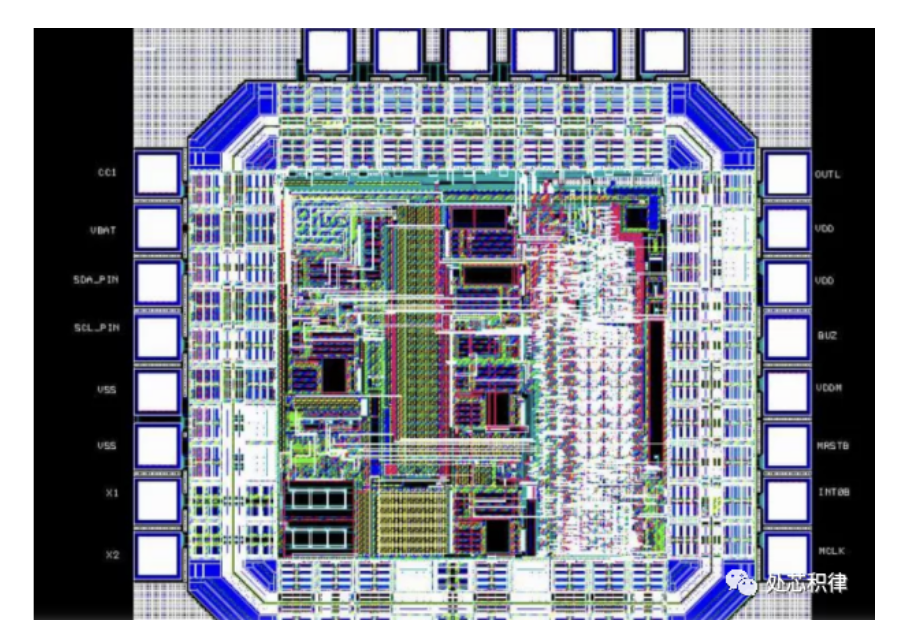

芯片产业是一个分工很细的产业。设计公司做完逻辑和物理设计,将最终设计结果交给芯片生产厂。芯片生产厂通过很多复杂的工序,在一块大...

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。理论上,采用F...

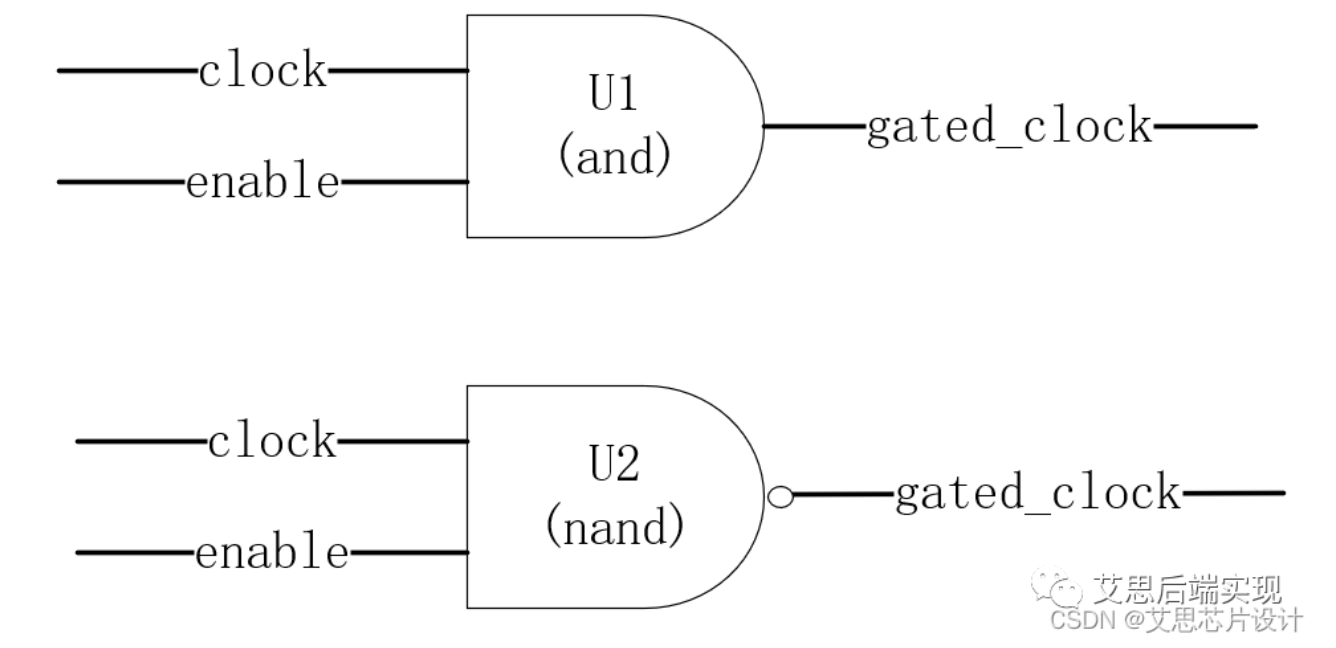

在笔者的一篇老文Clock Gating之浅见中,一起探讨过工具处理门控时钟的方法和门控时钟所带来的相关收益和面积代价。除此之外,门控时钟...

最近在折腾pulp,代码很优秀,强烈推荐。想在公司环境中跑起来,但鉴于公司eda服务器无法连外网,需要从外部导入数据。

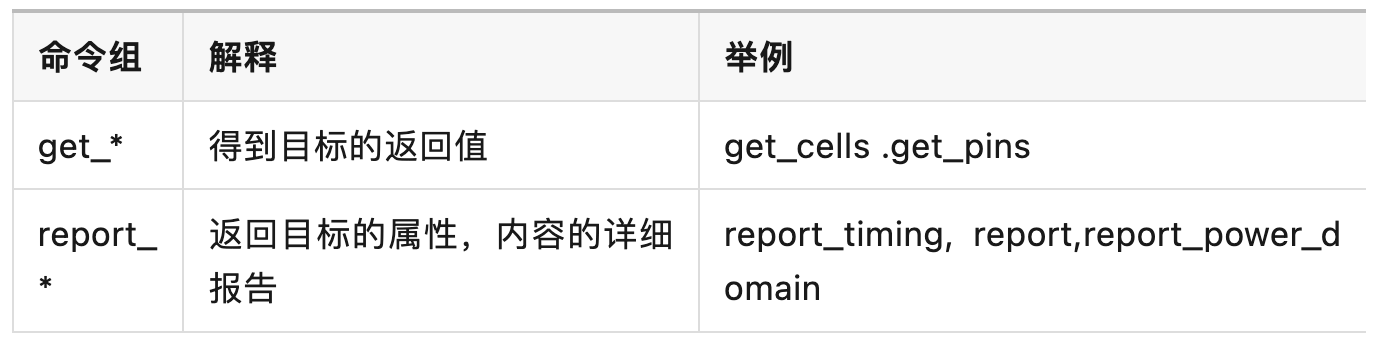

在S家的后端设计工具里,包括DC、ICC、ICC2、PT , 大体的命令都是相通的。并且主要命令的命名和分类都是有一定的相似性的(_但是要注意...

在整个R2G的流程里边,寄生参数抽取(StarRC)是比较没有存在感的。大部分的时间,工程师们只是用这个工具来刷SPEF。并不会关注太多。这...

在现代的芯片设计里边,工程师在优化功耗和面积上无所不有其极,这里讨论的multi-bit FF 就是其中的一种方法或者称之为一种流程。

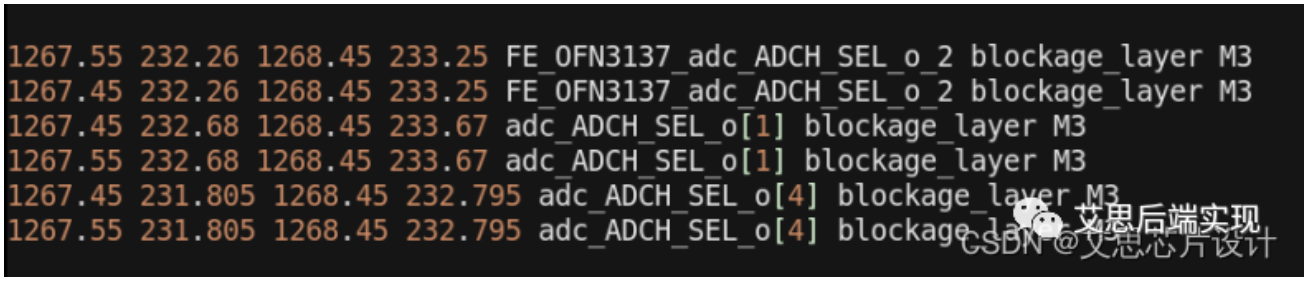

innovus里边有不少physical DRC检查工具,其中的verifyConnectivity 别有一番有趣的用法,借此机会,一起来看看其中的一个亮点。

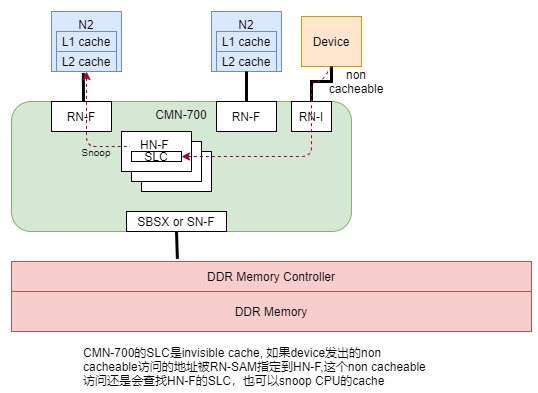

DC IVAC/ DC CIVAC指令用于将一个虚拟地址对应的cache line从data cache或是unified cache失效或清除失效到PoC点。N2 core硬件默认会将D...

在如今智能化的时代,芯片技术已经被广泛应用于各个领域,并且成为了整个智能产业链的核心。然而,传统基于CPU的处理器已经不能满足各项...

IC设计中通常基于设计时间线/业务线分为前端设计和后端实现,这个也是大家通常所能理解和接受的。类似下图

物联世界,智感未来!2023国际AIoT生态发展大会将于6月8日在深圳南山科兴科学园国际会议中心三楼举办。

就像小孩过满月,亲朋好友欢聚一堂,举杯同庆,为新生儿送上期许和祝福。在芯片的设计初期,也需邀请市场、客户和产品等多方专家共聚一...

分享一个coverage merge小技巧,在群里经常看到有小伙伴问改了代码之后coverage能不能merge。今天带大家来看看这个问题。

众所周知,在prePlace阶段打完Power后,需要使用APR工具把网表中存在的例化完的instance来全 局放置在core内,这个布局阶段(place)会暴...

在systemverilog代码运行中,EDA工具会先给1个随机种子值(seed),所有代码里的随机数都是根据这个初始种子衍生出来的。因此,通常来说,...

在现代SoC芯片验证过程中,不可避免的都会使用FPGA原型验证,或许原型验证一词对你而言非常新鲜,但是FPGA上板验证应该是非常熟悉的场景...

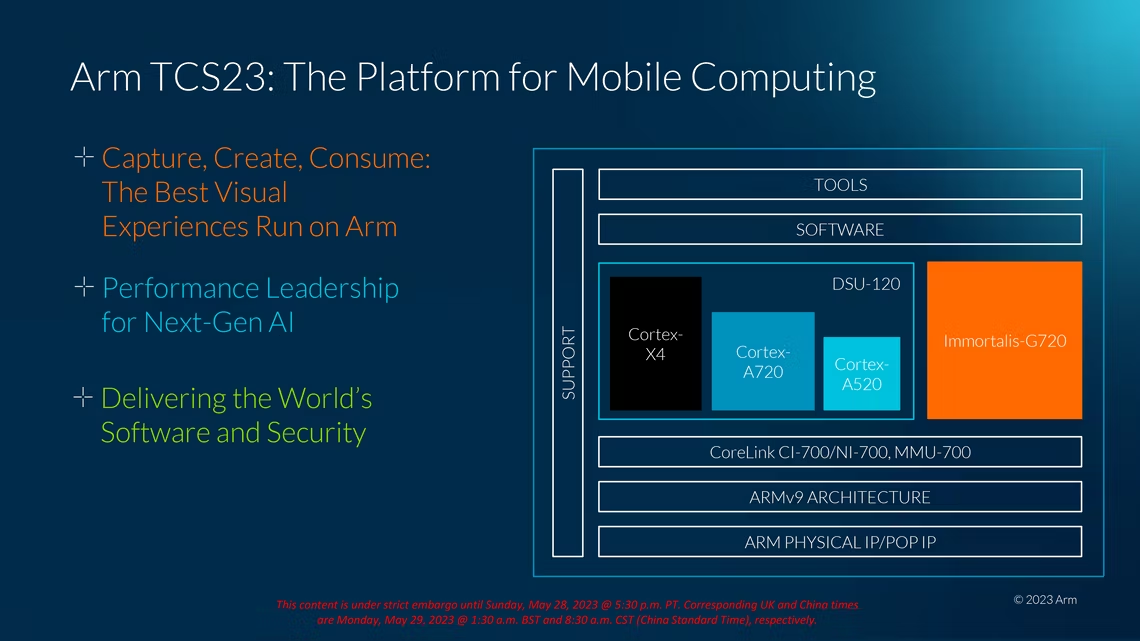

Arm 是一家设计智能手机的CPU内核的公司,并且每年它都会进行新的迭代,这些迭代随后将集成进芯片SOC,例如当年的旗舰 Snapdragon 、 Me...