本文是 how to define Synthesis timing constraint 系列文章的第四篇。

前 言芯片的功能安全曾是非常小众的领域,只有少数汽车、工业、航空航天和其他类似市场的芯片与系统开发商关注。然而,随着汽车行业过...

错误的地方:在时钟上升沿处处理复位信号,但未同步复位信号到时钟域,可能导致复位信号的抖动或同步问题。

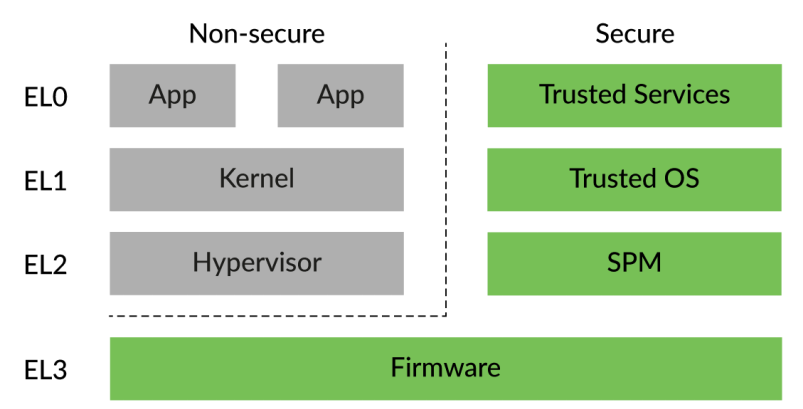

本文引入了Arm V9-A架构的扩展——Realm Management Extension(RME)。

Zephyr RTOS 对无线网络功能的支持一样非常齐全,那么没有自带 WIFI&BLE 硬件的AI芯片上,如何利用外接通道芯片 Soc 实现无线功能呢?这...

现在的深亚纳米工艺的设计中,低功耗已经是一个日渐总要的主题了,尤其是移动市场蓬勃发展起来之后,功耗的要求越来越严格,据传,在高...

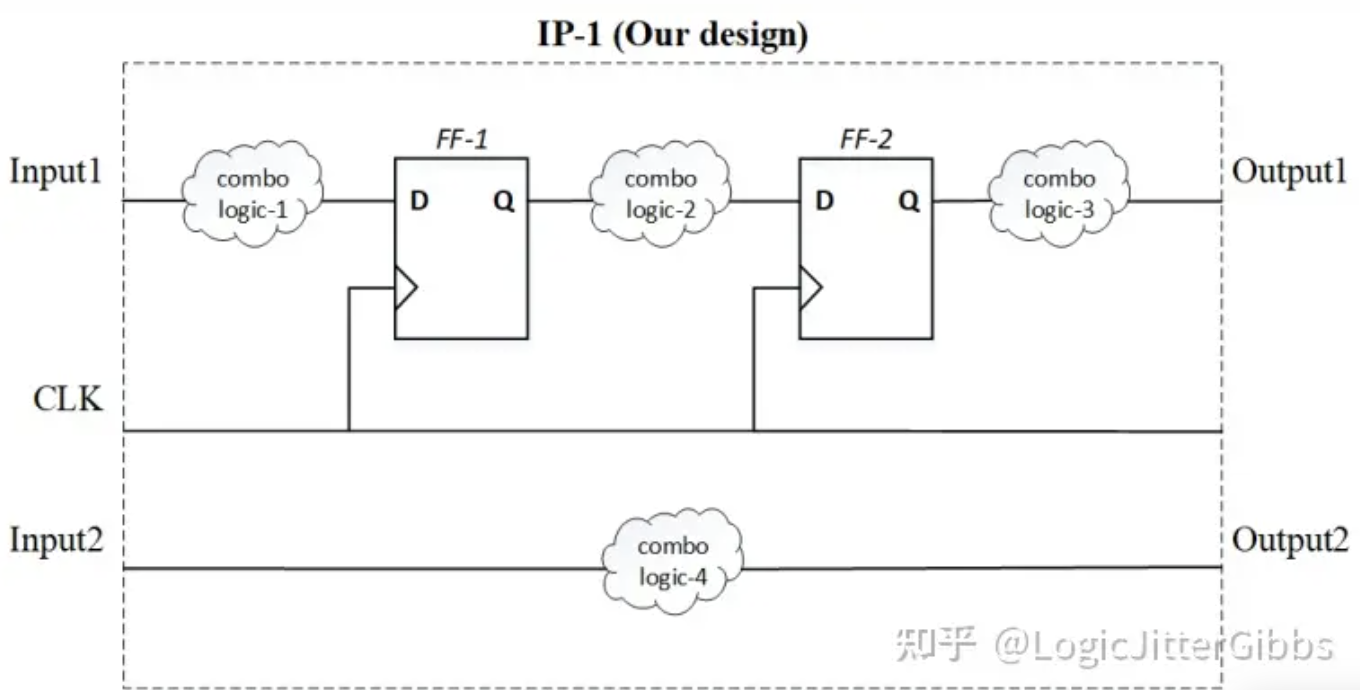

在数字电路设计中,RTL(Register Transfer Level)设计是一种抽象级别,用于描述电路的功能和行为。它在硬件设计中起着关键作用,因为...

本文介绍了数字IC设计中重要的概念,包括时钟树,复位树,以及在综合期间重要的SDC约束命令。在数字IC设计中,重要的ASIC设计约束分为两...

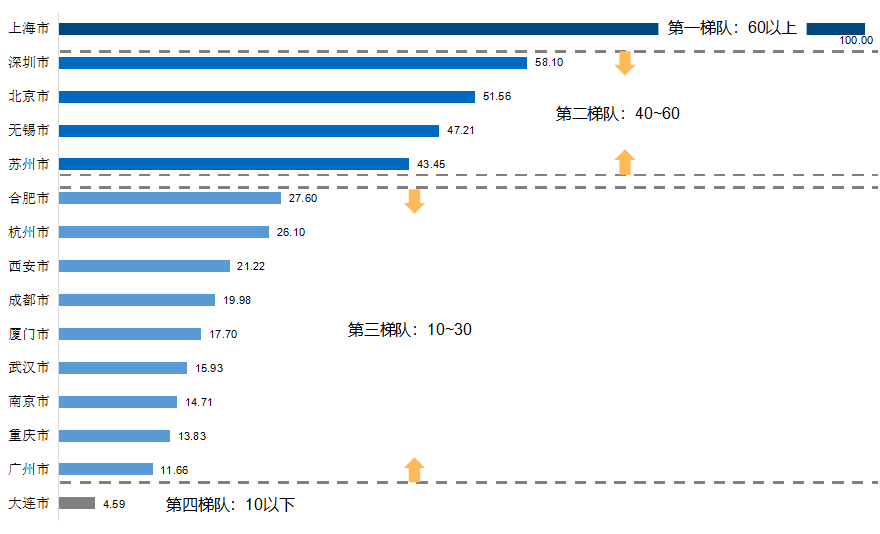

7月10日,雨前顾问与安谋科技(中国)有限公司联合发布《2023年中国大陆集成电路产业人才供需报告》。报告全面研判了中国大陆集成电路人...

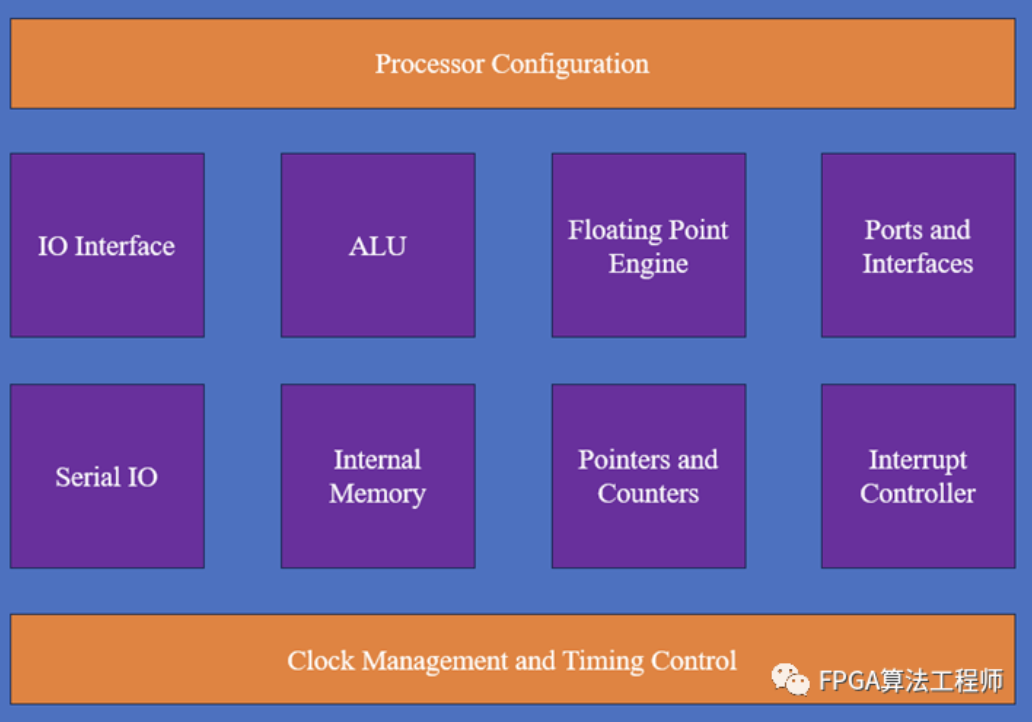

LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

全志(Allwiner)A523是一款八核Cortex-A55处理器,时钟高达1.4/1.8GHz,采用big.LITTLE(DynamIQ)配置,主要为具有多个显示接口的平板...

本文是 how to define Synthesis timing constraint 系列文章的第三篇。

本文是 how to define Synthesis timing constraint 系列文章的第一篇。

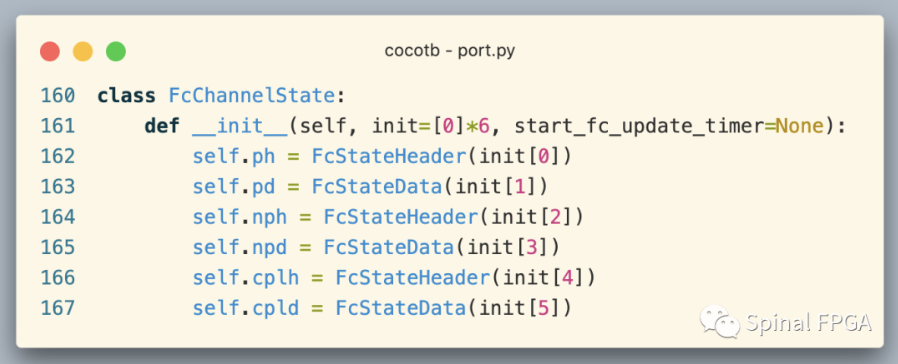

在处理TLP报文时,根据Fmt字段以及Type字段可以将TLP报文分为二十多种,当TLP报文送至数据链路层时,数据链路层在进行流量控制处理时则...

在使用UVM搭建环境时,遇到问题时,调试方式有千千万万,但很有必要了解下UVM库提供了哪些内建的调试手段,可以少走弯路,大大提升效率...

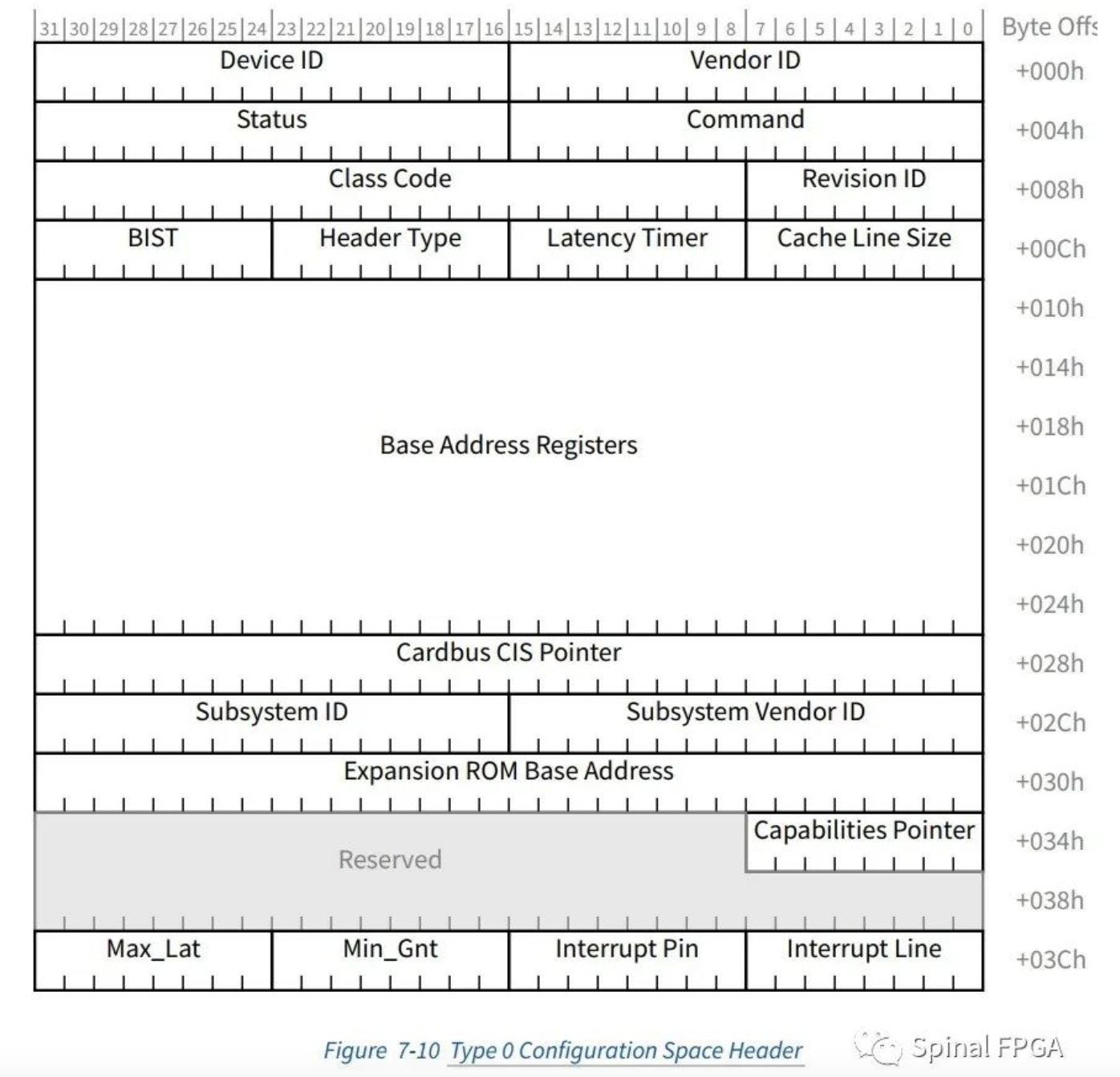

最近在研究cocotbext-pcie的实现,对于学习PCIe还是挺有帮助的,陆陆续续做个总结,有时间也会在SpinalHDL下实现类似的方针功能。

作为一名芯片工程师,从毕业出到步入公司的第一天开始,需要完成一次明显的转变,随着工作的日益开展和项目推进,个人能力的也得到了潜...

在项目中,一个TB通常是很多人一起开发的,大家或多或少都会往log中打印一些信息(message),方便自己debug。但是如果log里信息太多,会...

Bluespec SystemVerilog (BSV) 是由Arvind 开发的 Bluespec 语言,这是一种高级功能 硬件 描述编程语言,本质上是Haskell(Haskell ( / ...

在一组二进制编码中,若任意两个相邻的数值还有1位二进制数不同,则称这种编码为格雷码,由于最大数和最小数之间也仅1位数不同,即”首尾...