大家好,最近在学习Soc,对于mailbox,这个东西其实看到了很多次,但是一直不知道是啥。这里大概看了一下,知道了为甚有这个玩意儿,以...

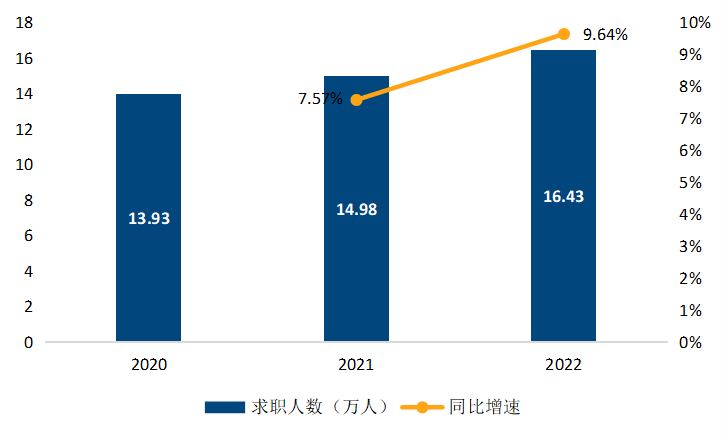

集微网报道 (文/陈炳欣)伴随新一波人工智能浪潮向汽车领域渗透,汽车智能化趋势愈发明显,汽车芯片市场需求旺盛。据统计,2022年全球...

不少从事IC行业的朋友,平时比较忙跟同行交流比较少,可能不清楚自家公司研发水平怎么样。今天小编从研发自动化这个角度说说好的公司做...

前面我们学习了8259A,但8259A 只适合单 CPU 的情况,为了充分挖掘 SMP 体系结构的并行性,能够把中断传递给系统中的每个 CPU 至关重要...

PCI Express(PCIe)总线诞生的年代,个人电脑中的扩展插槽数量与 CPU 时钟速度或系统 RAM 数量同等重要。从那时起,PCIe 总线就从一组...

在数字芯片设计领域,持续学习和不断进步是至关重要的。作为一名芯片设计工程师,毕业后若停滞不前,将会面临严峻的竞争和技术淘汰的风...

前面是借助8088这个基础的中断控制器,让我们对中断的硬件电路有了基础的认知,这里我们来看两个当下非常常用和流行的中断。

之前BMS AFE盘点的文章有段时间了,发现BMS这个赛道还是火热,目前摩拳擦掌面向储能研发的公司还不少,今天做一个更新。

移动电话技术的进步不断挑战极限,要求SoC在提供不断提升的性能的同时,还能保持较长的电池续航时间。为了满足这些需求,业界正在逐步采...

集成电路产业是信息产业的核心,更是支撑经济社会发展和保障国家安全的战略性、基础性和先导性产业。中国大陆集成电路产业处于构筑核心...

昨天有个朋友在问多核启动,于是今天就整理一篇多核启动的文章,内容大多数参考与网上前辈们的优秀博客,感激。

集微网消息,随着云计算、物联网等人工智能技术的发展,传统表计行业也在不断的发生变化,逐渐往智能表计方向转型,智能表计迎来了高速...

Arm 推出全新 Arm IP Explorer 平台,该平台是一套由 Arm 提供的云平台服务,旨在为基于 Arm 架构设计系统的硬件工程师与 SoC 架构师,...

英尚微简单介绍EB5REB1低功耗蓝牙SOC芯片(BLE5.0)的片上系统,并为客户提供足够多的能将SOC集成到产品中的信息。

以下是 EETOP网友在论坛职业版块发表的疑问:我本科硕士是在国内读的,毕业后进入一家海外公司工作,到现在刚好是足足11个年头,一直在...

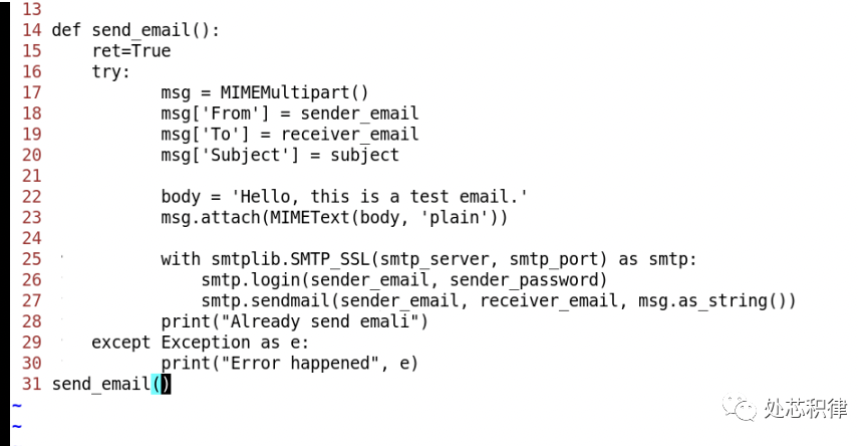

在创建一个linux系统的时候,安装完gvim,系统默认的gvim的模式是白色背景,黑色字体,无语法亮亮。打开一个python脚本大概是下面这种效...

今天与同事聊起了IC工程师的修养等问题,结合不久前的一个想法,总结成文,抛砖引玉,欢迎讨论和补充,转载请注明EETOP。

JTGA这个东西IC和嵌入式靓仔们肯定是有用过的,但是对于JTAG内部的东西,以及实现如果不了解的,可以看看这篇文章。

本文是 how to define Synthesis timing constraint 系列文章的目录篇。

我觉得称时钟树为芯片的大动脉一点也不夸张,因为所有flipflop 翻转都要受到它的控制。而时钟树的设计到实现是一个很复杂的过程,从流程...