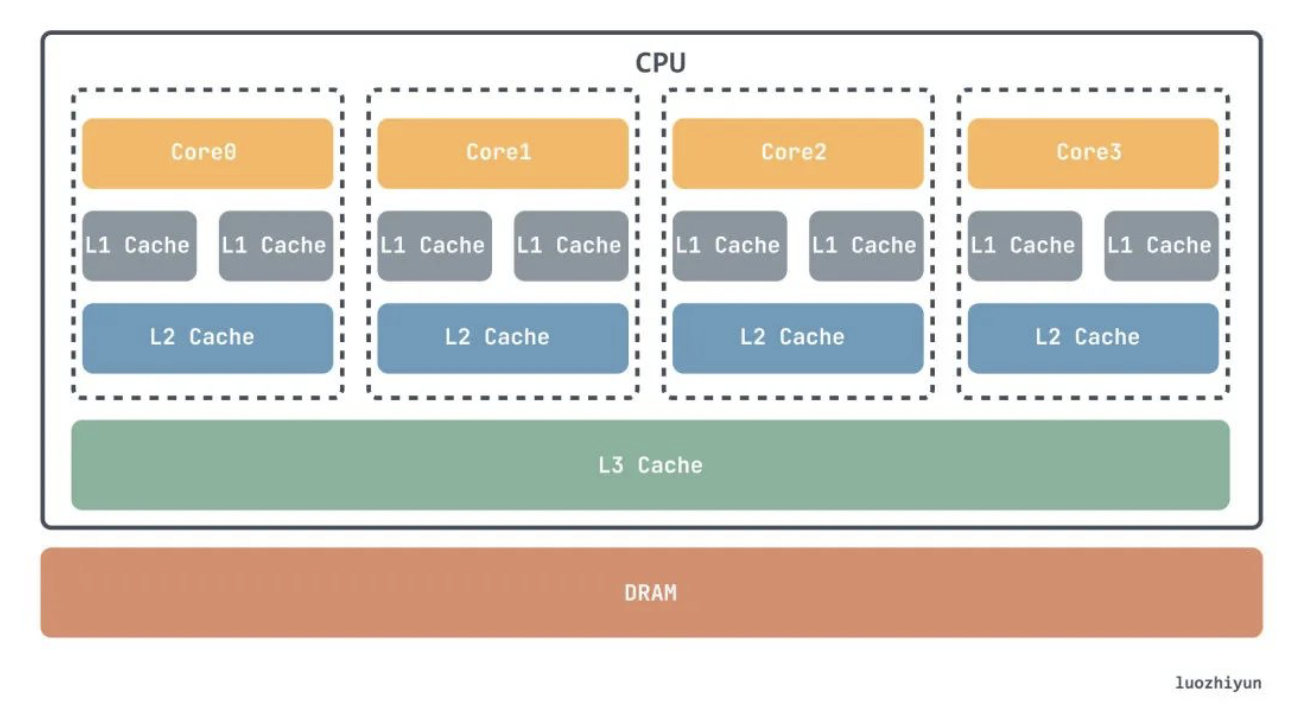

这篇文章主要整理了一下计算机中的内存结构,以及 CPU 是如何读写内存中的数据的,如何维护 CPU 缓存中的数据一致性。什么是虚拟内存,...

根据 Newzoo[1] 的报告显示,在 2021 年高达 1,756 亿美元的数字游戏消费中,移动游戏占比首次超过一半 (907 亿美元)。此外,在全球 30 ...

最近看到一篇绝佳的文献《Processor Microarchitecture: An Implementation Perspective》,刚好能回答这个问题。

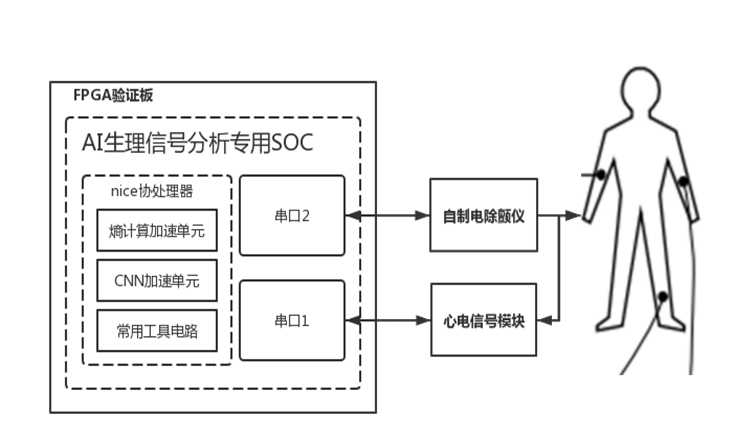

本篇文章是2022年第六届全国大学生集成电路创新创业大赛芯来RISC-V杯三等奖作品分享,参加极术社区的【有奖征集】分享你的2022集创赛作...

最近看到一篇绝佳的文献《Processor Microarchitecture: An Implementation Perspective》,该文献对微架构中的缓存、取指、解码、寄存...

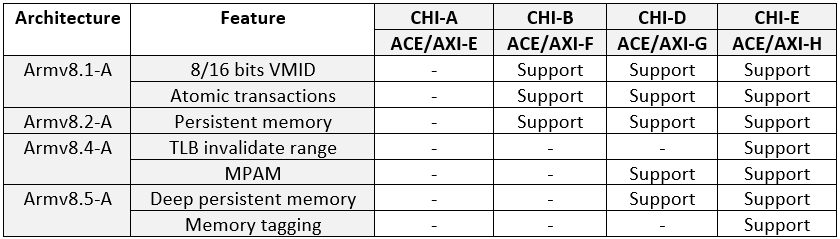

Arm构架功能持续演进,有些只需要CPU核本身的支持(如SVE/SVE2, PAC,BTI等),有些功能(如MTE,Armv8.1-A LSE Atomic, MPAM等)则需要...

在 Armv9 发布一个月之后,Neoverse 系列数据中心和服务器级处理器平台新增了两个核心 IP:基于 Armv8.x 的性能巅峰之作 Neoverse V1,...

今年6月24日,龙芯中科在科创板挂牌上市,公司主营自研LoongArch架构的CPU,首日涨幅接近50%,市值曾一度超过400亿元。

根据惯例,在临近发布会的几天里,媒体工作者已经收到了来自各种渠道的预测和曝光消息。在正式开启会议报道之前,就跟随着这篇汇总,一...

虚拟地址的出现可以追朔到上世纪六十年代的Atlas计算系统。在当时Atlas计算系统是一个庞然大物,但也只有96K字节的内部存储器和576K字节...

孙大圣大闹天宫也要借助金箍棒。做一件事,充分发挥工具的作用将会起到事半功倍的效果!尤其这几年,智能基础设施显示出独特的价值,以...

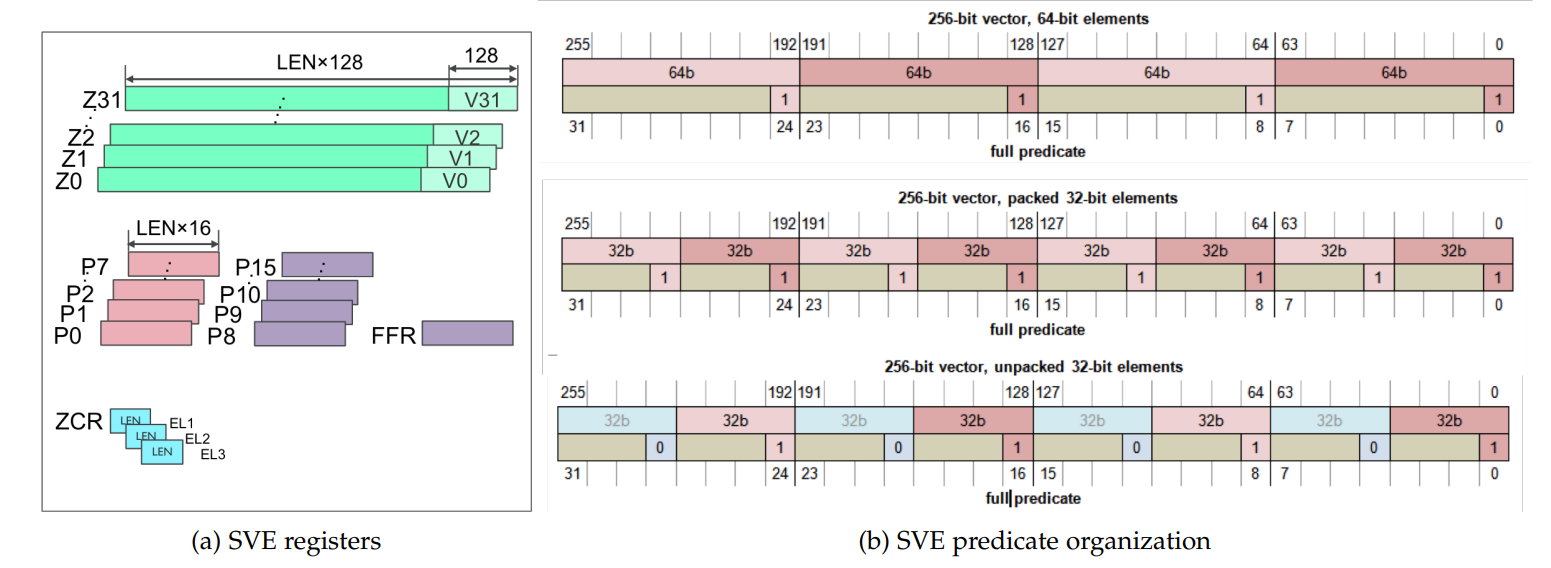

在这篇文章中我们介绍Arm可伸缩性向量扩展(Arm Scalable Vector Extension,SVE)。设计这个扩展的目标有几个:

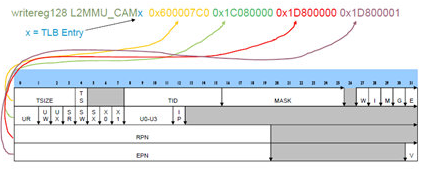

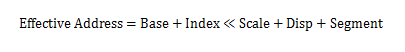

在一个CPU中,读写指令在进入Pipeline之前,首先被分解为两个微步骤或者是两个微指令,这并不是x86处理器所特有的,许多为了提高存储指...

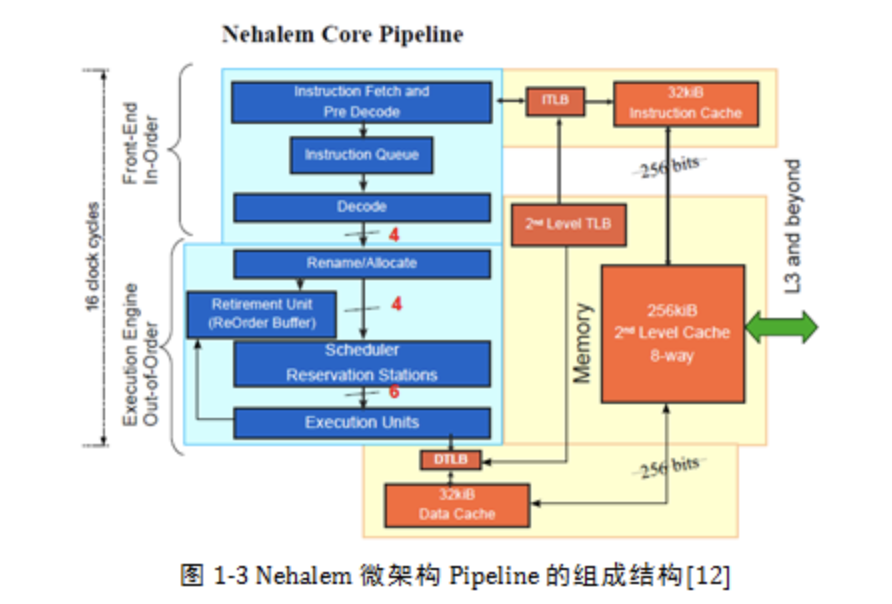

Superscalar与OOO(Out-of-order)的引入极大促进了现代处理器微架构的发展。已知的高性能处理器,如Nehalem,Sandy Bridge,Opteron,Pow...

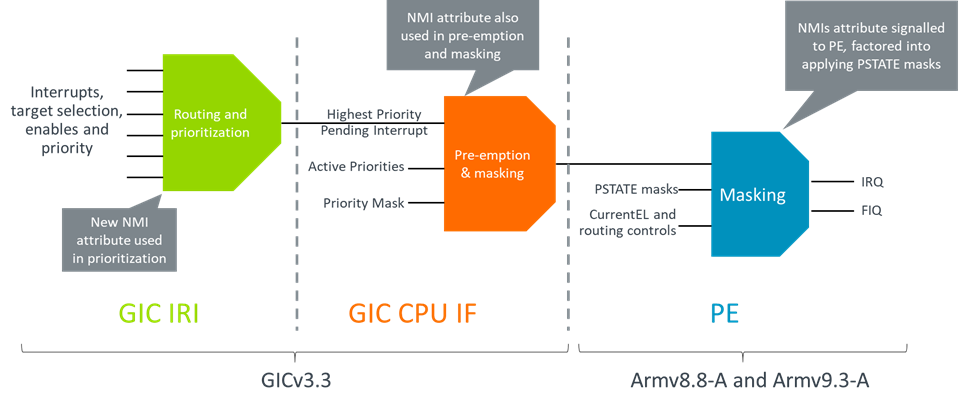

Arm A-profile构架一个长久以来的局限性是:缺乏对non-maskable interrupt (NMI, 不能屏蔽的中断)的支持。但是,随着Arm A-profile 构架...

Arm与arm构架授权公司及生态伙伴一起,持续进行构架演化,开发满足现有和新市场产品需求的新构架特性。

用户空间支持当CONFIG_ARM64_MTE使能而且CPU硬件也支持MTE时,Linux通过HWCAP2_MTE属性告诉Usersapce kernel支持MTE功能。

如前所述,支持heap tagging需要修改Linux kernel和C库里面的malloc相关实现。支持stack tagging需要使用一个编译选项重新编译代码。下...

MTE设计用来检测内存安全漏洞,增加对抗攻击的鲁棒性。在动态链接系统中,老的代码不用重新编译就可以在heap分配中用MTE。在Stack中使用...

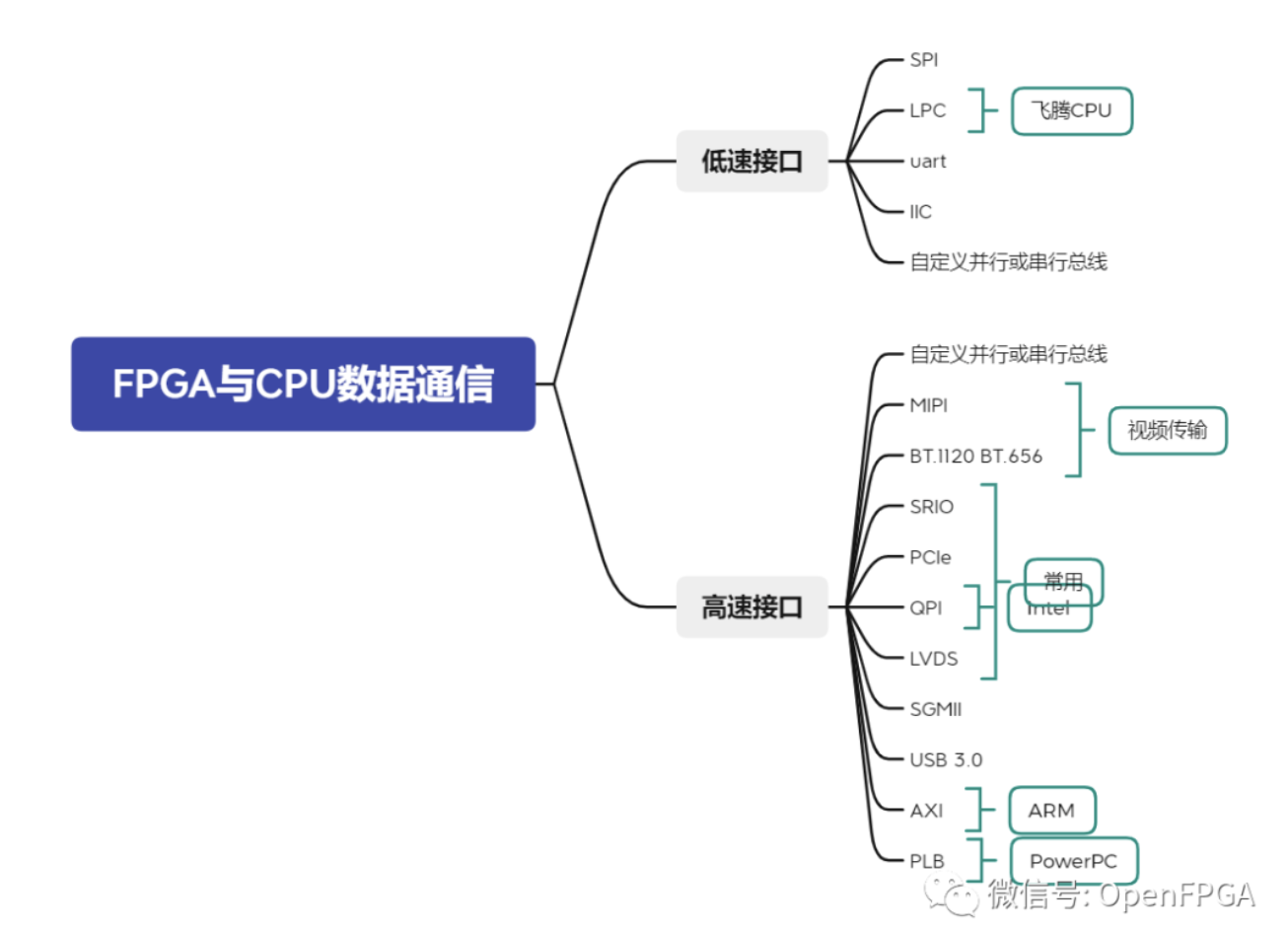

在进行FPGA设计时候,除了一些算法\验证等应用,其他情况下都需要FPGA和控制器进行数据交互(通信)。