目录1、基础概念2、启动流程3、ATF(TF-A)代码的剖析5、软件如何判断当前是cold reset/warm reset/primary boot/senondary boot5.1 cold ...

拥有 12 年手机安全、汽车安全、芯片安全开发经验,擅长 Trustzone/TEE/ 安全的设计与开发,对 ARM 架构的安全领域有着深入的研究和丰富...

编 者 按 对于那些喜欢先写代码再写文档的小伙吧,寄希望于直接把仿真的波形直接贴到文档上作为接口时序图,又嫌弃波形文件太丑的小...

对于使用第三方来源进行 SoC 设计的团队来说,半导体知识产权(IP)的质量是一个主要问题。对于高度可配置的 IP 类型来说,质量更加重要...

跨时钟域(CDC)的主要问题是,当目标时钟域采样时,跨时钟域信号可能出现的 setup 和 hold violation 然后出现亚稳态,其中亚稳态可以...

今年7月31日,IDC发布最新预测称,2024年全球GenAI智能手机的出货量将同比增长363.6%,达到2.342亿部,占2024年整个智能手机市场的19%。...

Modelsim 仿真工具是 Model 公司开发的。它支持 Verilog、VHDL 以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程...

“SPI转CAN-FD”是嵌入式开发领域的常用方法,它极大地促进了不同通信接口之间的无缝连接,并显著降低了系统设计的复杂性。飞凌嵌入式依托...

作为本土领先的通用32位MCU产品及解决方案供应商,灵动基于安谋科技自研业务产品与Arm技术方案,自主研发软硬件产品并打造了完善的MCU生...

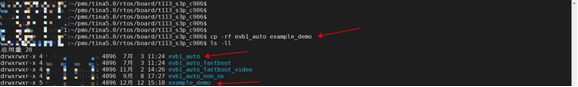

此处以在t113_s3p_c906 芯片下创建一个example_demo方案为例,帮助客户快速创建定制方案。第一步:进入rtos/board/t113_s3p_c906目录,...

DRAM 不再缩放。在辉煌的年代,内存密度每 18 个月翻一番——甚至超过了逻辑。这相当于每十年密度增加 100 多倍。但在过去的十年里,缩放...

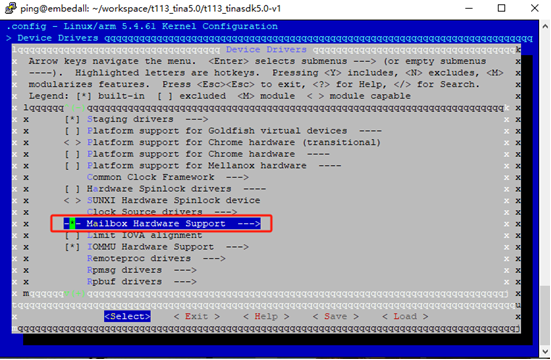

本章节以SBC-T113S4主板的TinaLinux为例,介绍异构双核通信的实现。该方法也同样适用于T113i平台。

小编最近在做逻辑综合时,总在 Verilog HDL 以及 SDC 内见到 SERDES 时钟以及相关约束,为了揭开 电串行器/解串器 Serdes 的神秘面纱,...

做硬件设计,在做设计文档时总少不了接口时序图的绘制,之前曾写过两篇文章《VSCode:WaveForm在手,时序我有》、《Markdown时序图绘制与...

在linux系统中进行芯片调试定位时,我们经常需要读取寄存器的数值,有些时候可能手动读取就可以了,当读取频率高且数据量较大的场景时,...

在芯片开发工程中,通常为了知道工程目录下发生了哪些改动,或者两份源码文件之间有什么不同,会需要用到文件和文件夹的比对工具。使用...

英尚微代理基于自研射频技术和基带算法提供蓝牙MCU。蓝牙MCU配套成熟的网络协议栈和丰富的示例代码及多平台APP工具。部分芯片型号无需二...

CDC是Clock Domain Crossing的缩写,当芯片中有多个异步时钟域,信号从一个时钟域到另一个时钟域时,这是数字IC设计中最关键的问题之一。

版权声明:本文作者:烓围玮未。主要从事ISP/MIPI/SOC/车规芯片设计/SOC架构设计首发于知乎专栏:芯片设计进阶之路微信公众号:芯片设计...

本期我们将讨论 DDR4 的 Gear-down mode (直译:降档) 特性,他是一种提高 DDR 系统兼容性、稳定性的特性