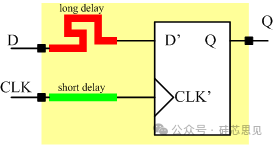

现代 SoC 设计通常采用多个时钟,并包含多个时钟域。当数据从一个时钟域跨越到另一个时钟域时,由于异步时钟域交叉(CDC),会出现亚稳态...

今天和大家分享一下 DDR 内存设计中一个重要的技术 - 写平衡(Write Leveling)。这项技术对于高速 DDR 内存的正常工作至关重要。

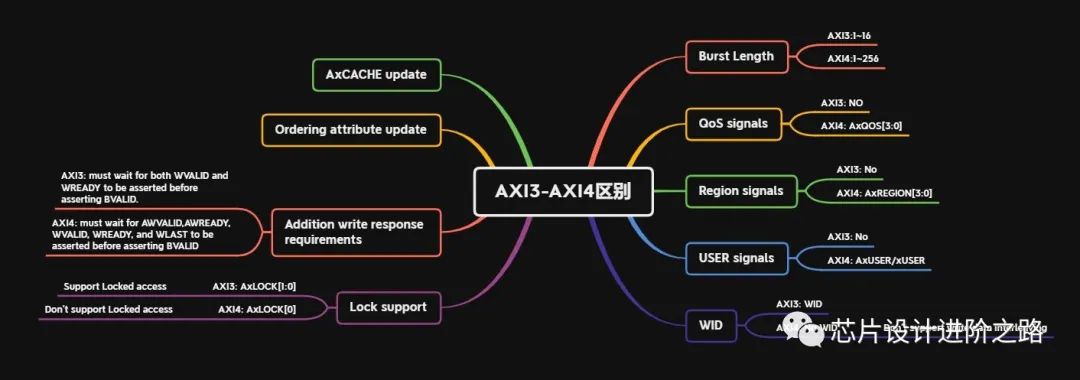

在 SOC 各种总线中,AXI 是最重要的总线,没有之一。不管是在工作中,还是在面试中,AXI 协议是一个必须精通的知识点。ARM 从 AMBA1 到 ...

全球电动工具市场规模近年来保持稳定增长,2023年市场规模已达288.5亿美元,预计2024年将突破304.9亿美元,年复合增长率达6.9%。中国市...

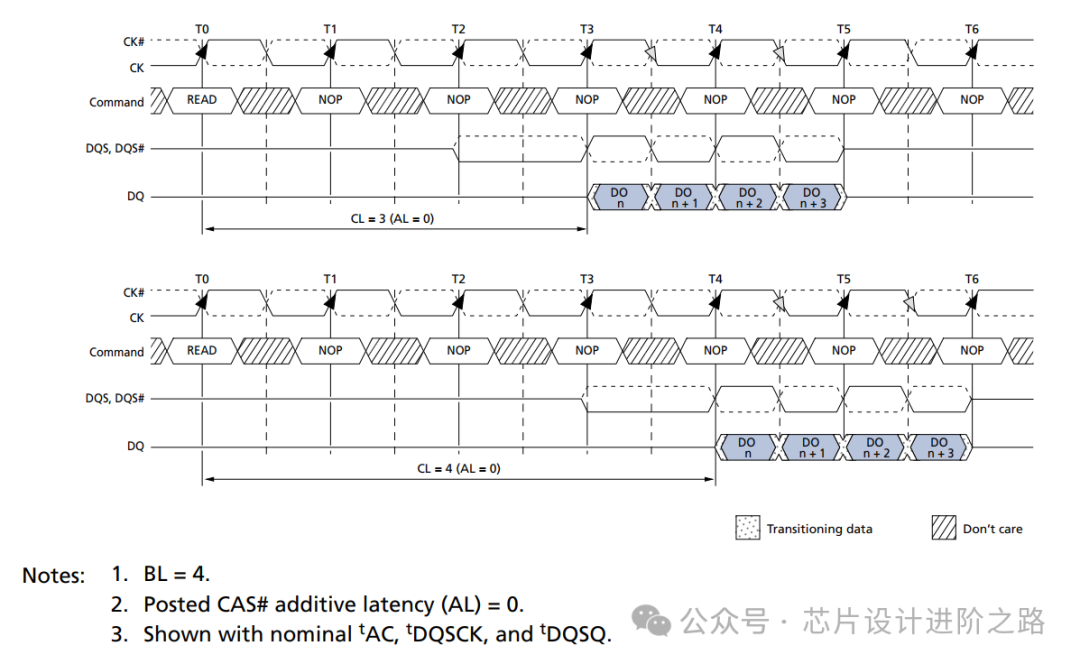

在当今这个数据驱动的时代,内存子系统的性能对各种计算系统的表现起着至关重要的作用。DDR(Double Data Rate)内存技术自 2000 年推出...

在进行后仿真时,经常会看到工具反标时提示存在负延迟,并且这些负延迟经常出现在 SETUP、HOLD、INTERCONNECT 和 IOPATH 中。出现负延迟...

VHDL 的 英 文 全 名 是 Very-High-Speed Integrated Circuit Hardware DescriptionLanguage,诞生于 1982 年。

“每天用手机刷视频、打游戏、扫码支付的你,可能从未意识到:掌心里的这块‘玻璃板’中,藏着一座堪比北京地铁网的超级迷宫——它就是手机芯...

在使用静态时序分析工具的时候,通常会遇到 case analysis 的情形,但是由于时序分析工具的静态分析属性,工具会自动传播 case value,...

Chiplets 技术将大型集成系统级芯片(System-on-Chips, SoC)分解为更小的功能模块,有望为半导体行业带来革命性变革。通过允许不同公司设...

在智能汽车和电动汽车日益普及的今天,汽车 SoC(系统级芯片)成为了推动汽车行业变革的关键技术。作为汽车的大脑,SoC 芯片不仅影响着...

在现代生活中,无论是住宅、商业场所还是工业环境,良好的通风换气都至关重要。随着科技的不断进步,智能排风扇逐渐走进大众视野,而基...

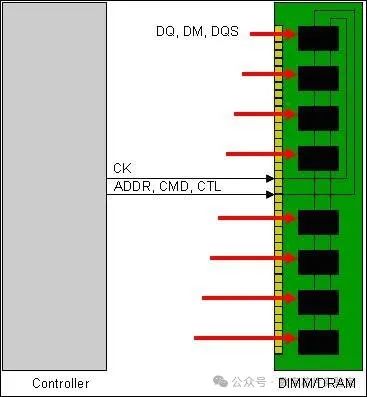

目前,许多嵌入式 SoC 的 DDR 规格从 DDR4 升级到 DDR5。本系列设计须知文章是笔者参与一个 DDR5 SoC 项目时,总结的一些 DDR4 升级到 D...

在 SoC 验证中,checklist是很重要的一步,要审视下有没有无意间漏掉的检查或者做出的假设。大部分情况下,checklist 总能发现一些 RTL ...

亚稳态是触发器或锁存器输出端发生的不可预测行为,其输出在特定时间段内呈现 0 到 1 之间的非特定值。

在数字电路设计中,加法器与减法器是最基本且应用带有场景的运算模块。addsub模块是一个适用于广泛场景的加减法实现,支持加法和减法操...

在进行 PCIe 调试过程中我们时常需要执行 retrain 操作。retrain 命令是让 PCIe 链路先退出 Link 状态(ltssm==L0),ltssm 会进入 reco...

课程介绍课程大纲01-Trustzone简介什么是TEE?TEE基础科普TEE的生态介绍?有哪些TEE厂商?各有什么特点?02-TEE技术简介什么是TEE?TEE...

通过总线将各个 IP 通过总线连接起来的 SoC 芯片是未来的大趋势,也是缩短芯片开发周期,抢先进入市场的常用方法。如何确保各个 IP 是否...

UCIE 协议主要包括 protocol 层,Adapter 层和 PHY 层。Protocol 层复用 CXL,PCIE 或自定义的 stream 流格式。