在20nm 以下的工艺中,由于相邻 metal wire 的间距太小,使得光刻过程中,相邻的光线间距过小,相互之间发生干涉,导致metal wire 边缘...

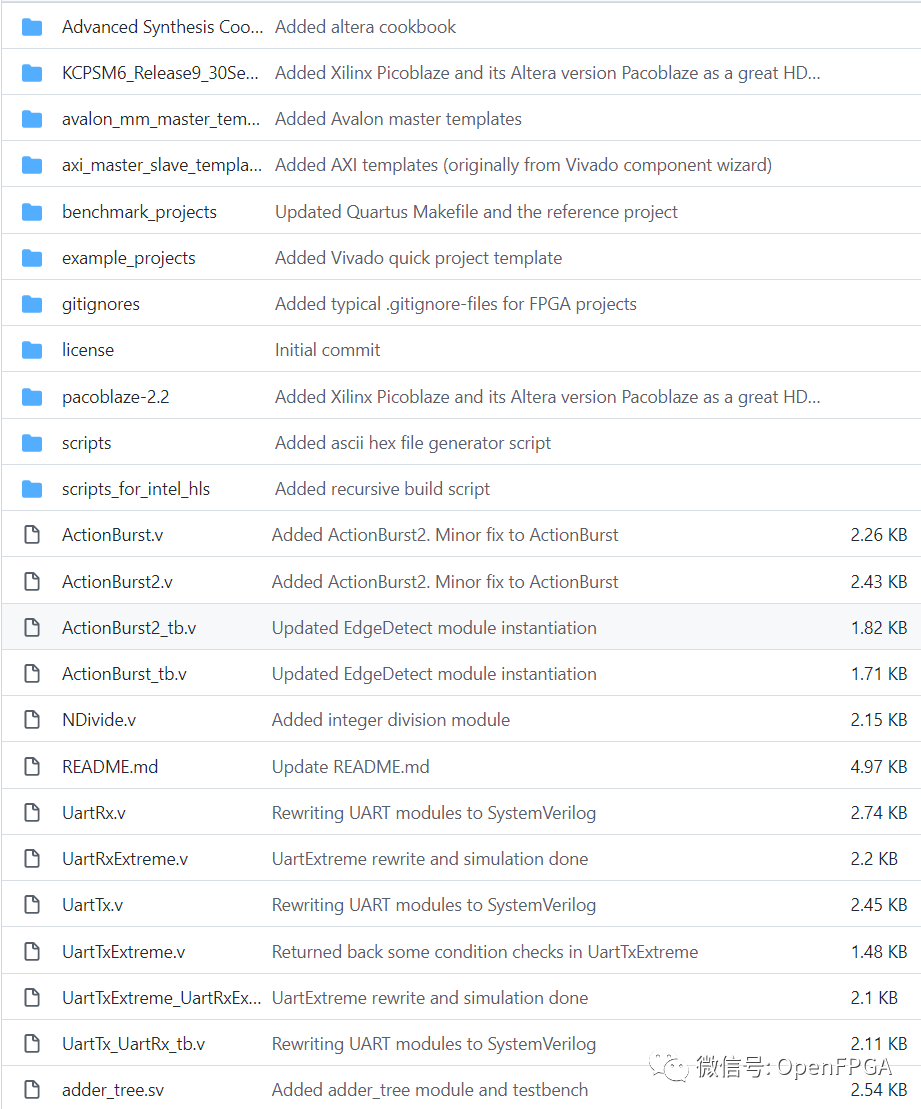

想拥有自己的Verilog IP库吗?设计时一个快捷键就能集成到自己的设计,酷炫的设计你也可以拥有!

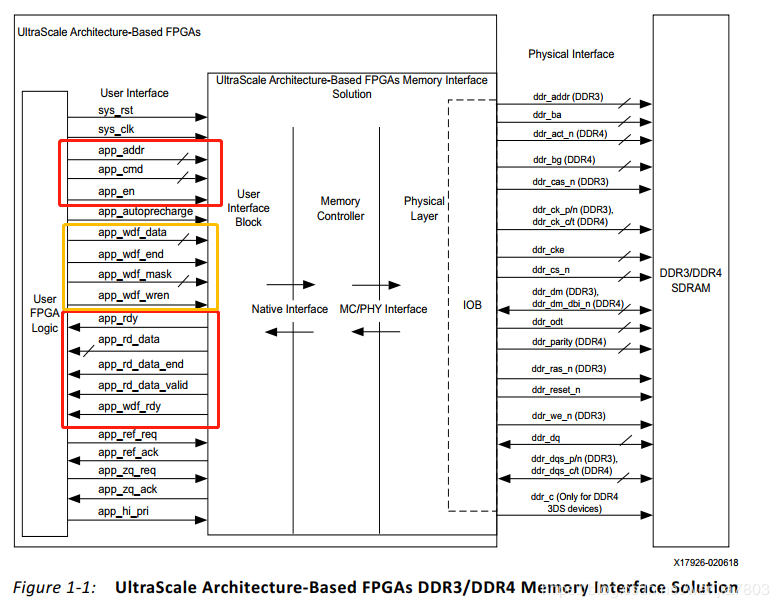

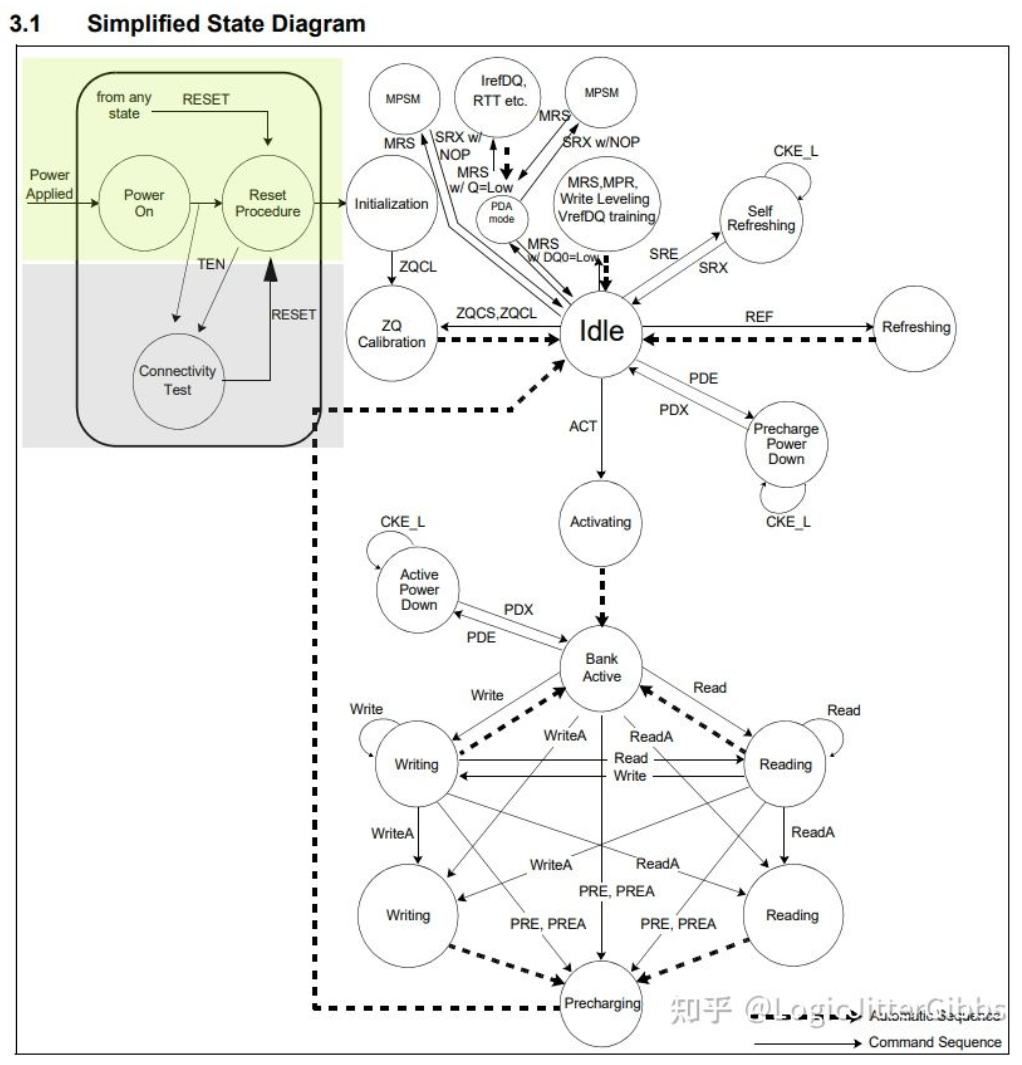

根据官方提供的资料,IP核主要划分为三个部分,分别是用户接口,内存控制器以及物理层接口。对于用户来说,我们需要研究清楚的是用户接...

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

在实际项目中经常用到串口接收一些不定长的数据,此时必须面对一个问题:怎么判断这一帧数据接收完成了呢?通常使用UART非空中断配合简...

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

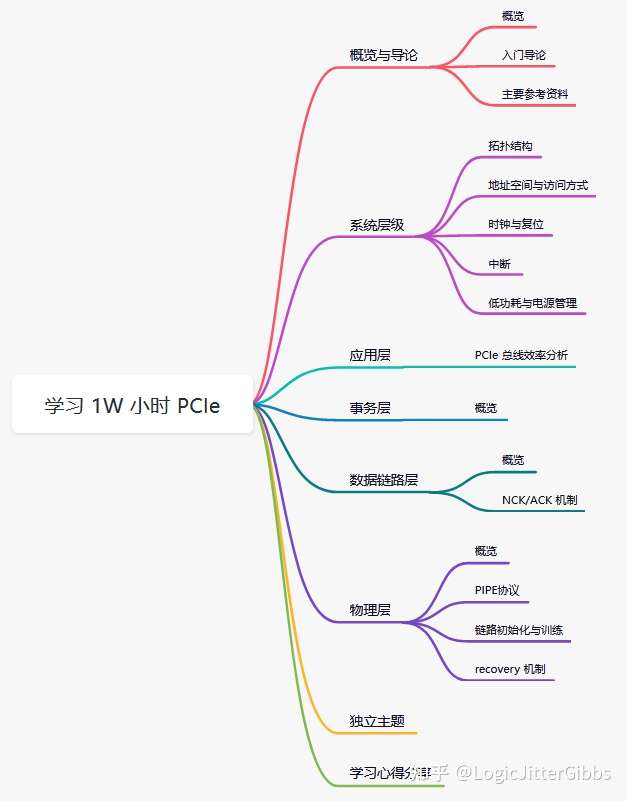

本文整理了若干 PCIe 在线学习资料,笔者基本都是看过的。资料以 PCIe 的若干个层级划分,包括系统层级、应用层、事务层、数据链路层以...

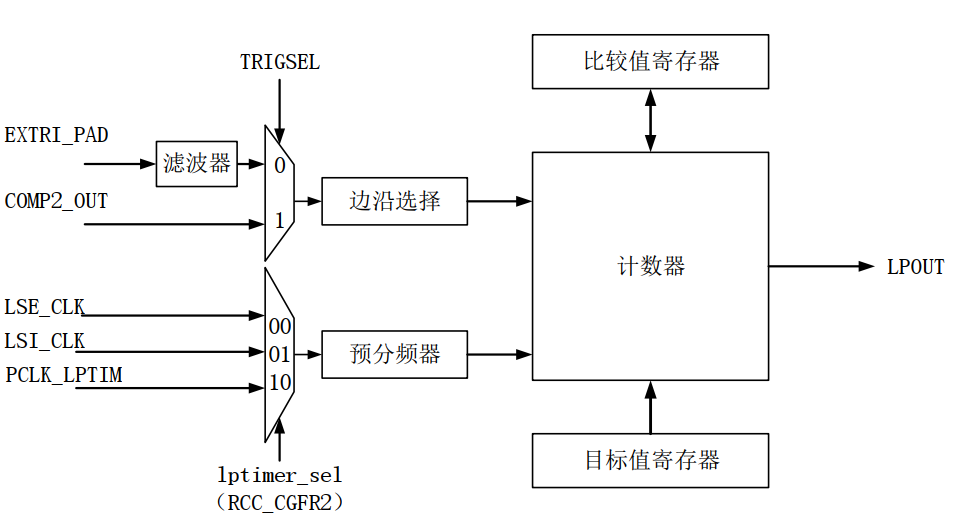

在许多的工业与消费类应用中,越来越多的需要使用低功耗功能,使用定时唤醒,停机减低功耗。灵动微电子推出的MM32F0270系列,支持多种灵...

没有任何寄存器逻辑,RTL设计是不完整的。RTL是寄存器传输级或逻辑,用于描述依赖于当前输入和过去输出的数字逻辑。

去年 Google 在 I/O 大会上宣布全新的操作系统 WearOS 3 后,行业即传出希望高通 Wear 4100 系列对其支持的强烈呼声。

公路、海洋、农场,镜头从高空俯视,缓慢推进,并依次切换。广袤而平坦的地面,被渲染了一层阴暗的色调,一直延伸到天际。

MM32F3270系列的ADC支持注入通道功能,每个ADC模块具有4个注入通道。每个注入通道具有独立的数据寄存器,注入通道具有比规则通道更高的...

瑞芯微电子股份有限公司(以下简称“瑞芯微”)正式发布新一代机器视觉方案RV1106及RV1103,两颗芯片在NPU、ISP、视频编码、音频处理等性...

今天给大家介绍几个自动集成的方法。 方法一: 使用verilog-mode定制,其官方网站为:[链接] 优点:功能非常强大。有专门的学习网站...

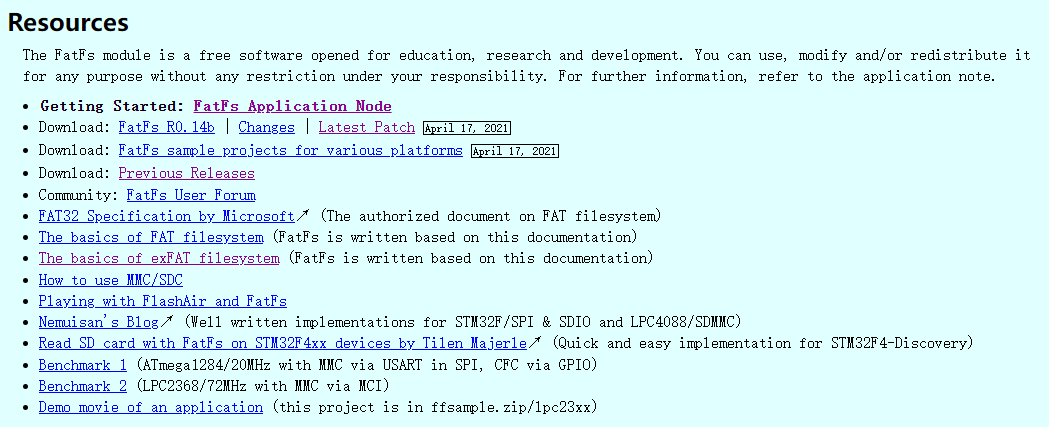

在前面章节中介绍了使用MM32F3270的SDIO外设驱动SD卡,对SD卡识别和简单的数据读写验证,不过像这样直接操作SD卡存储单元,在实际应用中...

片上网络 (NoC) 是一种用于组织位于同一芯片上的操作模块之间的通信的方案。它旨在结合各种用途的计算核心(执行、图形、物理等)、设备...

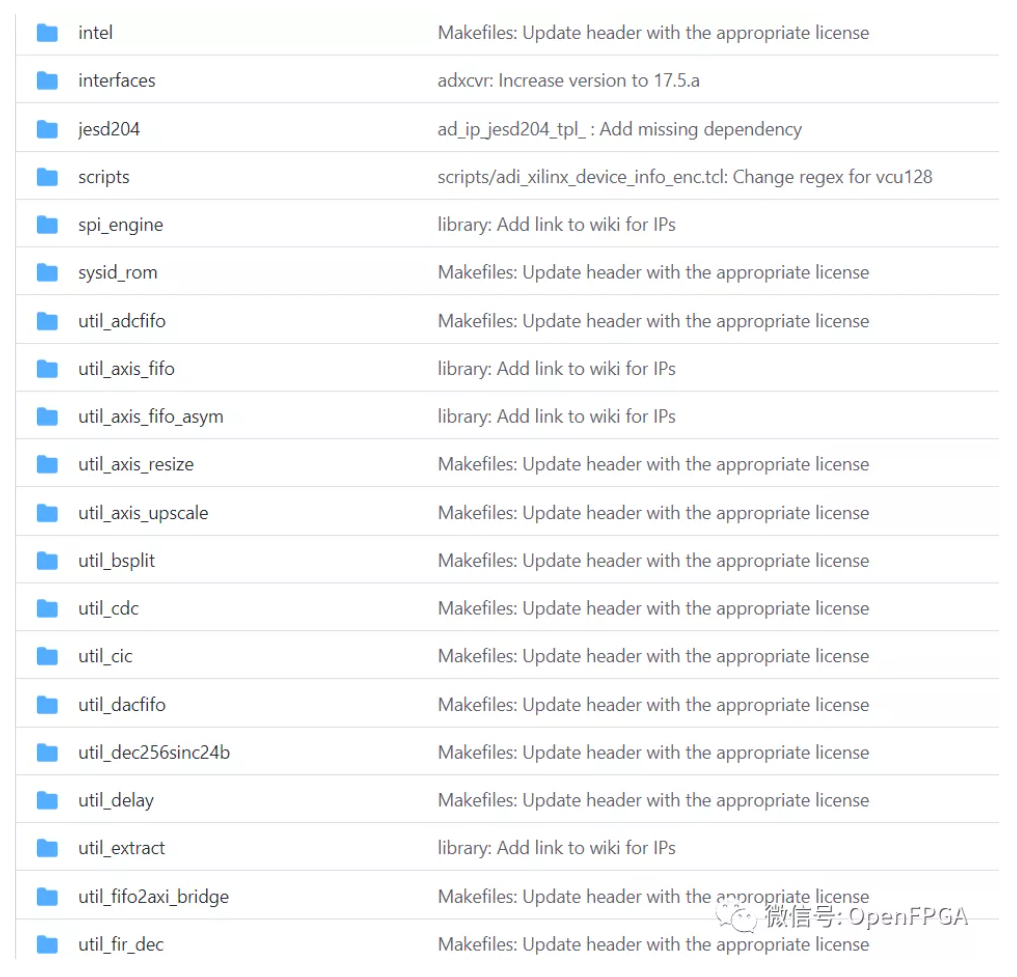

官网[链接]github[链接]HDL 参考设计Analog Devices Inc.用于各种参考设计和原型系统的 HDL 库和项目。该存储库包含 HDL 代码(Verilog ...

近日,AMD 已经完成了对 Xilinx 的收购,由于过去一年半时间里 AMD 的股价上涨,最终成本接近 490 亿美元,而不是最初在 2020 年 10 月...

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

最近加的群里面有些萌新在进行讨论FIFO的深度的时候,觉得FIFO的深度计算比较难以理解。所以特出漫谈FIFO系列,会涉及到FIFO的深度计算...