截止目前(2024年4月),“最强单片机”还得算Cortex-M85内核单片机(Cortex-M85是目前最强的Cortex-M内核)。

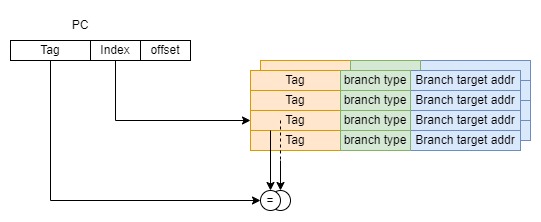

现代CPU须在指令预取pipeline stage具备性能良好的分支预测器,以给pipeline后端供应充足有效的指令。大多数CPU会使用 BTB(Branch Targ...

Defacto SoC Compiler 是用于片上系统集成的领先工具,允许用户根据相关约束条件将各种 IP 块(如 CPU 内核和互连结构)组合在一起,并...

Arm 每年发布两次最新版本的 Arm Compiler for Linux。 这包括一个完整的用户空间编译工具链,适用于基于 Linux 环境的 C、C++ 和 Fortr...

一位客户要求澄清 Eigen gemm 基准的执行情况。特别是当 L1D_CACHE_WR 的 PMU 值低于 L2D_CACHE_WR 时。在这种情况下,L1 数据高速缓存...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

LLVM 18.1.0 于 2024 年 3 月 6 日发布 。 在多项新功能和改进中,Arm 提供了对最新 Armv9.5-A 架构的支持,以及大量性能和安全增强功能...

随着存储介质在 I/O 性能方面不断演进,存储软件占用的总事务时间百分比变得越来越大。提高存储软件栈的性能和效率至关重要。存储性能开...

直流无刷电机用途广泛,具有高效节能、使用寿命长、运行可靠无电火花、结构简单易维护等性能优势,在办公设备、智能家居、消费家电、工...

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

今天Arm正式发布了MDK6,除了此前大家在Community Edition 中已经熟悉的内容外,最大的惊喜莫过于原本收费的MDK Middleware 实现了免费。

语法DBG{cond} {#option}DMB{cond} {option}DSB{cond} {option}ISB{cond} {option}cond : 是一个可选的条件代码(请参阅条件执行)。opti...

说明在默认情况下,本文讲述的都是ARMV8-aarch64架构,linux kernel 5.14, optee3.14

说明:本文虽然以spinlock函数为例,但并不会深度解读spinlock函数。本文重点解读exclusive机制。

WFE : Wait for Event : 如果Event Register=0则立即存入low-power standby state,否则Event Register清0.

各位大佬好,如下是关于中断唤醒系统的一个流程上的总结,由于这方面知识过于复杂,又牵扯到SOC厂商的设计,而且我也没有做过这方面工作...

Configuration signals是SOC给ARM Core的信号,这里的CN应该是Configuration Number的意思. 如果8个Core,那么CN就是7. 也就是有8根AA64...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈 关注"Arm精选"公众号,备注进ARM交流讨论区。

思考:1、 SOC一上电,只有一个核启动,还是所有核都启动?2、如果SOC一上电,如果只有一个核启动,那么从核启动的时候,从核的入口是哪...

最近在群里,一些小伙伴在讨论code reset和warm reset,疑问很多,总是有很多不能理解的地方,可能和SOC的设计关联较大,每一家的设计可...

aarch64boot address 是允许设置的,软件可配,根据信号RVBARADDR 具体设计而定

物理旁路攻击涉及观察目标的物理属性(例如电力消耗和电磁泄漏)以推断出秘密。典型的目标包括在硬件和软件中实现的加密算法。传统上,...

(1)、故障是改变电路正确预期行为的物理干扰(2)、它可以是电压或温度的变化,也可以是激光或电磁脉冲… 都有不同的效果(3)、影响可能是永...

最传统的一种攻击方式是栈溢出(stack smashing)。 有很多类型的栈溢出。 栈溢出的基本形式涉及恶意软件将新的操作码写入内存,然后尝试...

Linux 系统中,为了防御栈溢出漏洞的利用,通常会部署 Canary 漏洞缓解措施.下面简单描述下 Canary 的原理。对于栈溢出漏洞的利用,最简...

ShadowCallStack 是一个检测通道,目前只为 aarch64 实现,它可以保护程序免受返回地址覆盖(例如堆栈缓冲区溢出 : stack buffer overf...

(1)、部署 Canary 漏洞缓解措施GCC编译器默认开启该机制,可加-fno-stack-protector 关闭该机制原理: 其实就是在ebp之前(aarch64应该叫F...

• 机密计算的定义• 描述一个复杂的系统信任链• 了解 Realm 是 Arm CCA 引入的受保护执行环境• 解释如何在 Arm CCA 的实施中创建、管理和...

十多年来,TrustZone 一直在基于 Arm 的设备上成功保护媒体pipelines 。 在此期间,这些设备的要求随着比特率、分辨率、帧率、图像质量...