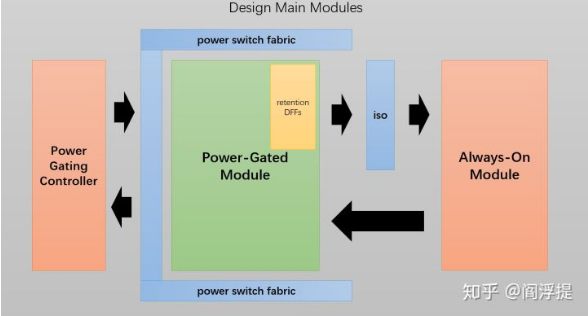

在低功耗设计领域,最有效的降低功耗的手段莫过于电源关断了。其原因在于不论多低的电压,多小的电流,多慢的速度抑或多小的leakage,都...

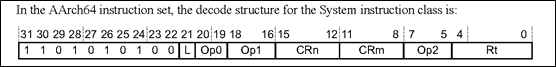

system指令,也就是sys,sysl指令,的编码如下所示:L: 传输方向 {代码...} op0:系统指令类型 {代码...} op1: 最低访问权限的EL {代...

Arm中国创新教育中心(Arm Innovation Education Center China ,AIECC)是Arm中国和江北新区研创园共同打造,由安芯教育运营,为南京江...

systemverilog中,如果一个函数的参数为数组,那么在外部调用这个函数时,可以向这个数组参数,传递一个真正的数组,也可以通过 '{}方式...

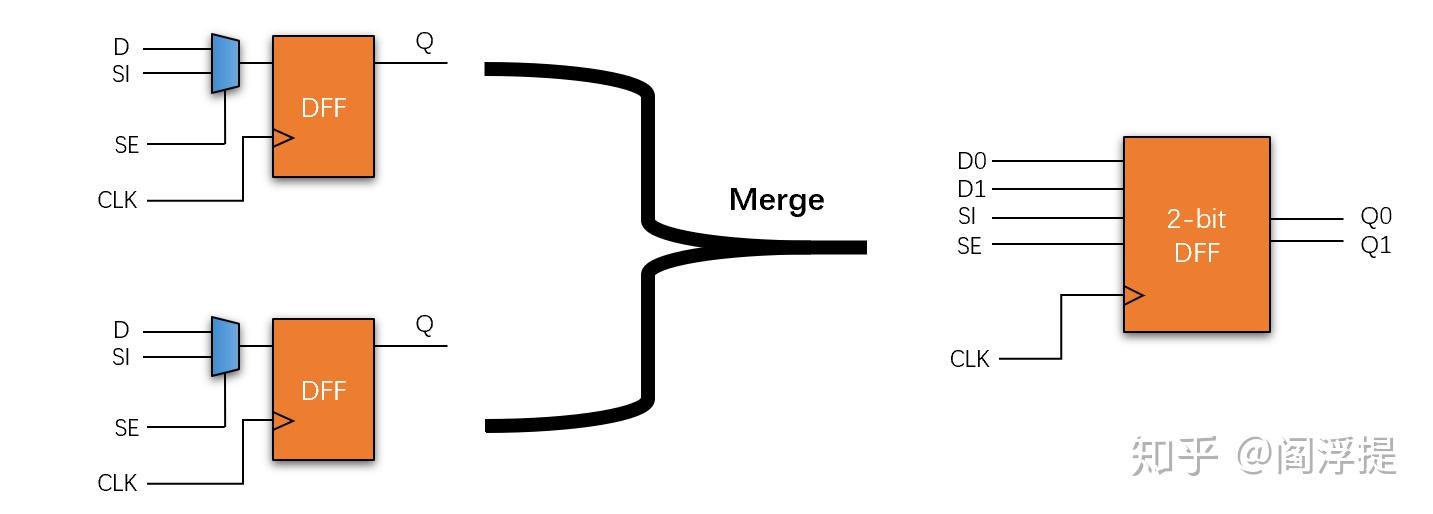

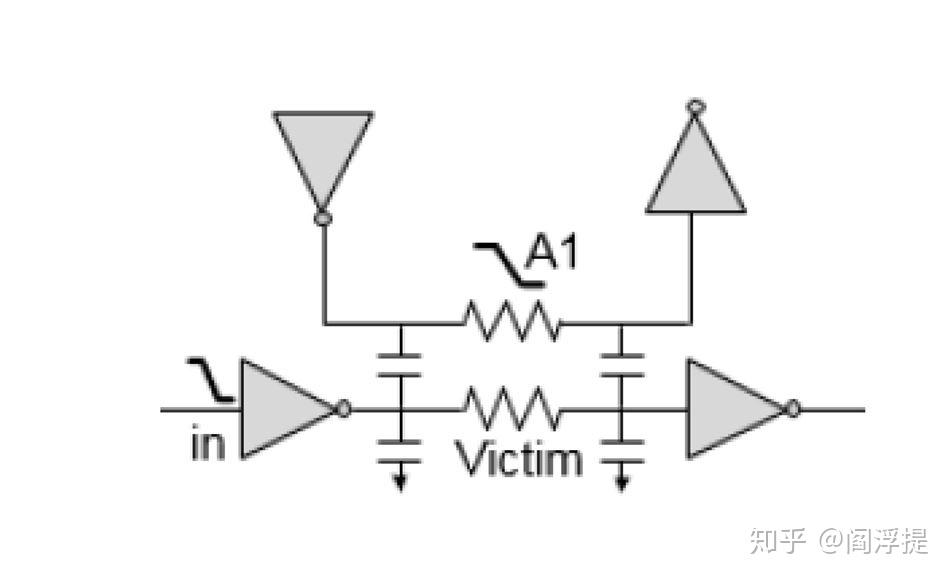

Multi-bit cells作为一种控制功耗的手段已经广泛应用于大量的芯片设计中,各种EDA工具中也提供了广泛而完善的支持。今天我们将对这种cel...

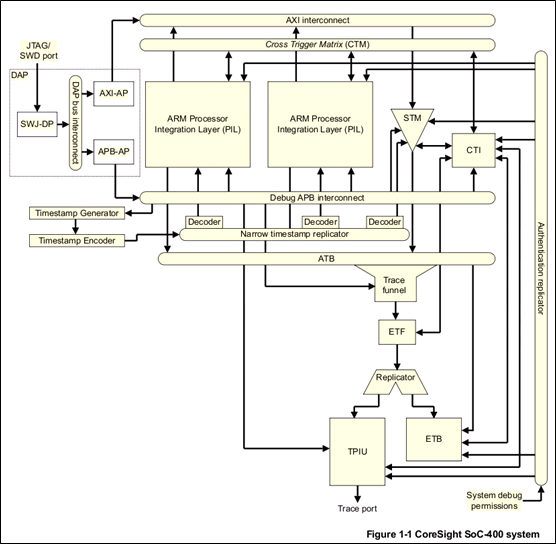

因为coresight属于ARM制定的标准,因此ARM针对coresight,设计出来soc-400套件。设计人员可以利用这个套件,快速的生成coresight系统,...

Arm推出了Arm Mobile Studio 2020.1,这是一款调试和优化Android游戏及其渲染工作负载的开发者工具工作室的更新版本。这个版本除了包括...

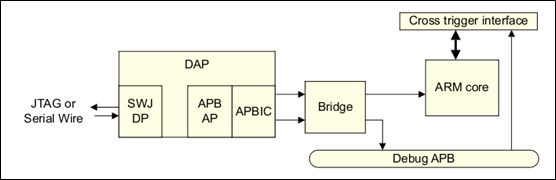

一个DAP,加上一个AP和APBIC。外部对DP访问,DAP将DP访问,转化为AP访问,AP通过APBIC,生成AP总线,通过bridge,对ARM core中的debug资...

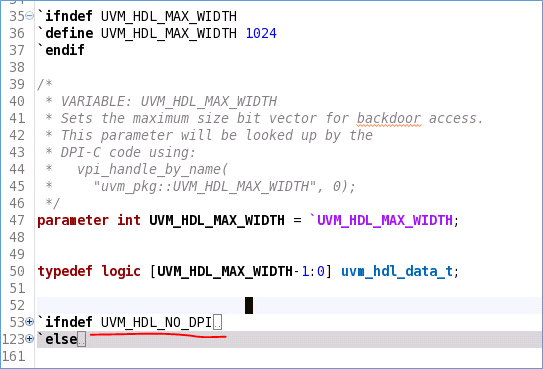

文件中,定义了使用typedef定义了uvm_hdl_data_t类型,其实就是大小为1024bit的数据。

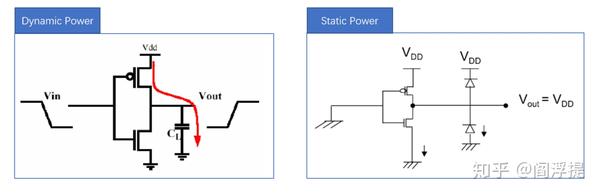

Multi-Vth在当前的IC设计中使用如此广泛,以至于我们说起低功耗的设计手法时经常将其忽略。尤其是工艺进入深微亚米后,Multi-Vth基本上...

这篇博客是一系列博客中的第二部分,探讨如何使用内存模型工具。它提供了一个实验模型的机会,并对它的工作原理有了直观的了解。这些信...

大多数低功耗设计手法在严格意义上说并不是由后端控制的,Clock Gating也不例外。在一颗芯片中,绝大多数的Clock Gating都是前端设计者...

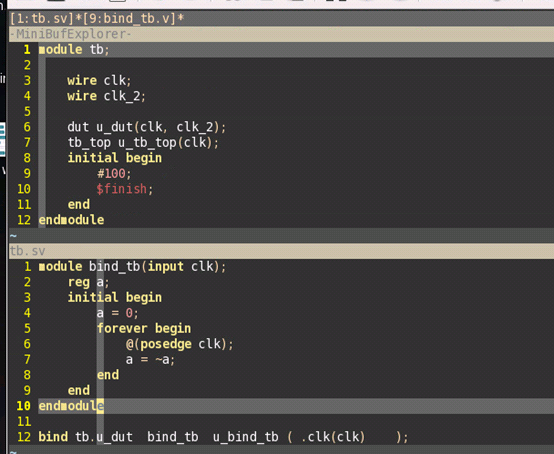

使用irun的增量编译,可以在环境修改情况下,加快编译速度。在实际的使用过程中,在bind操作,遇到了编译的问题。下面将该问题进行分享。

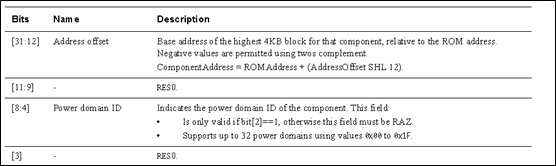

power requestor属于coresight组件。这个组件用来控制系统的power domain,最多可以控制32个。

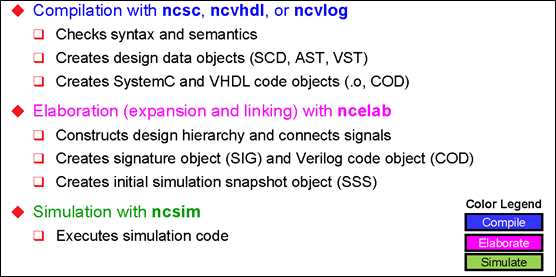

cadence,有两大验证仿真工具。一个是IUS,一个是IES。IUS是cadence以前的仿真工具,功能略弱。代表工具,ncverilog。官方介绍: {代码....

在一个soc中,有多个coresight组件,但是软件怎么去识别这些coresight组件,去获取这些coresight组件的信息了?这个时候,就需要靠cores...

最近大半年IC行业的招聘市场比较动荡,不少新创公司高薪挖人,加上一些原本有成熟产品的企业也开始拉队伍自研芯片,开出了不菲的offer,...

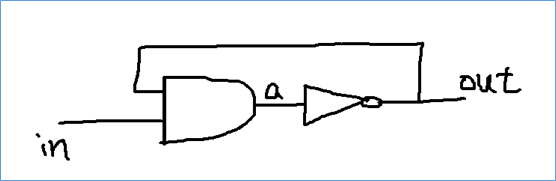

编写RTL,如果不注意,可能会写出zero-delay(零延时)的组合逻辑,也就是组合逻辑的输出,直接反馈到组合逻辑的输入上。如下图中组合逻...

channel interface是用来使不同coresight组件之间传递event使用。使用两个组件来实现:

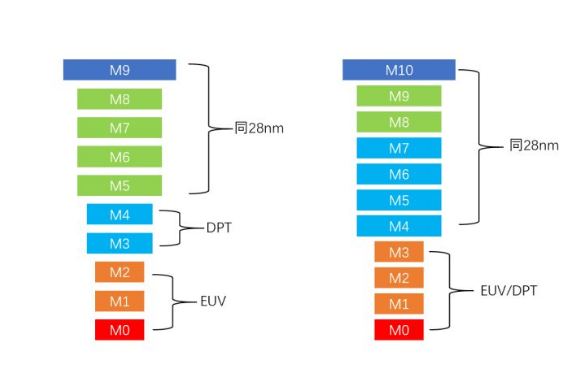

最近开始做一个7nm的项目,发现对于后端来说,有一些东西和之前的工艺有些不同,因此希望借此机会和大家分享一下。