真空中光速为299,792,458米/秒,目前,Intel的i7频率可以达到4GHz,简单换算一下,可以得出结论:光(电流)在一个Cycle内移动的距离约...

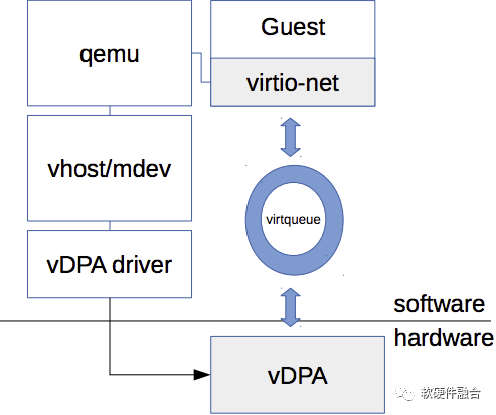

编者按: DPU和CPU通过PCIe高速连接,基于PCIe构建DPU和CPU之间的软硬件接口,如Virtio、NVMe、AWS的ENA/EFA等,以及各厂家自定义的基于...

严格讲我不是CS专业,不清楚CS本科是否需要学习CPU架构。或者说,在这个软件高度集成的时代,软件工程师有必要掌握这些细节吗?我的答案...

在20世纪80年代4位、8位CPU逐渐成为主流,但是当时的CPU发展还处于探索阶段,所以各种“奇葩”的CPU都有出现,今天给大家带来1-bit CPU MC...

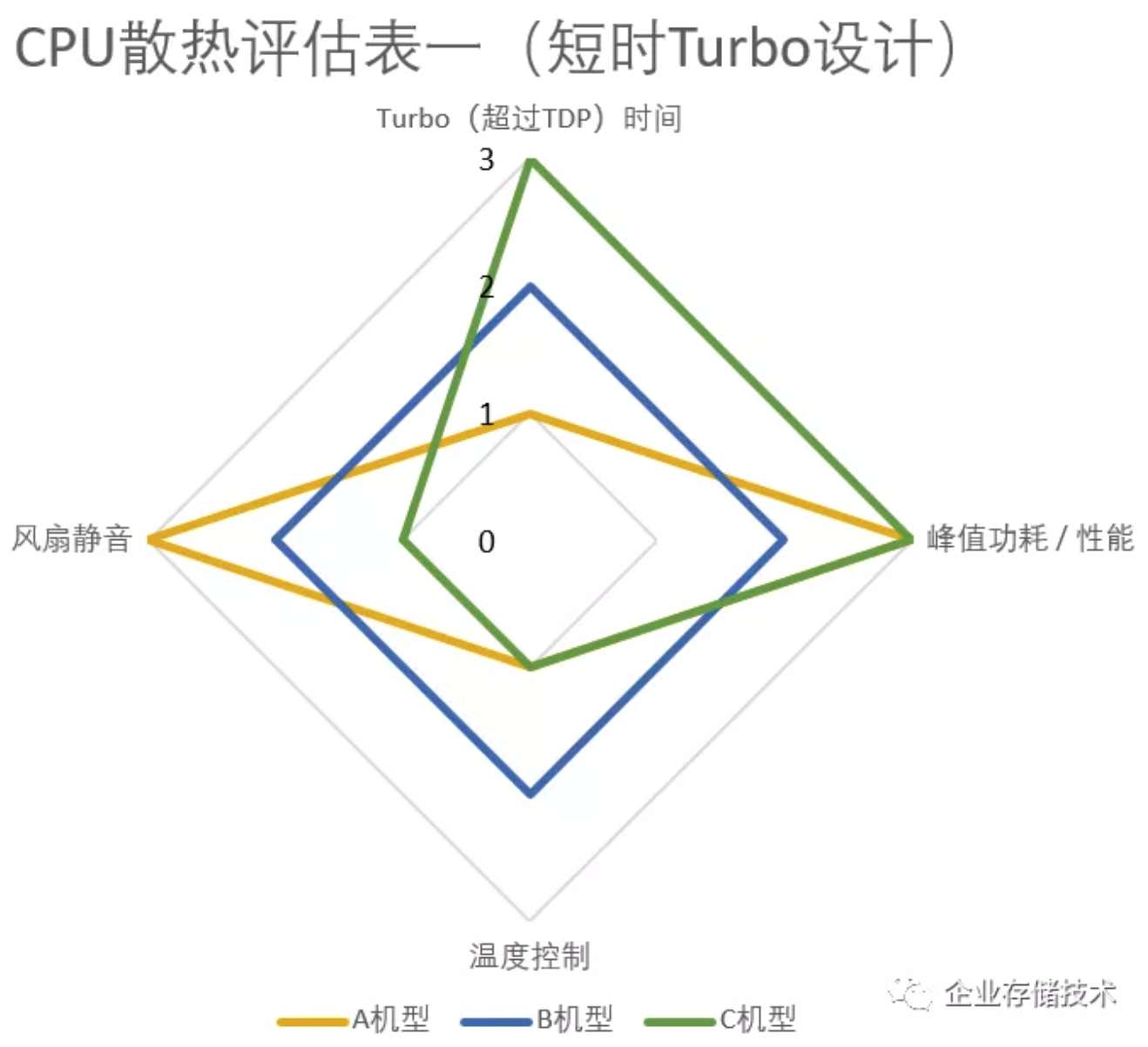

最近在工作中,有时会遇到解释CPU Turbo频率,以及温度和功耗控制的问题。我发现有的同行朋友在这块的认识存在一些误区,倒不是说技术原...

继火力发电、风力发电领域之后,飞腾CPU在水力发电领域也获得落地应用。8月6日,基于飞腾FT-2000/4研发的全国首套700兆瓦水电机组国产计...

本文将重点围绕国产CPU的发展历程与当前产业链各领军企业的布局情况作详尽解读(并包含特大号独家整理的最新进展),具体如下:1、国产C...

百年大计,教育第一。2021年7月6日,教育部联合六大部委发布《关于推进教育新型基础设施建设构建高质量教育支撑体系的指导意见》,提出...

NVIDIA 今日发布了两个在 ARM 平台上运行 GeForce RTX 技术的新 Demo,展示了如何将先进的图形技术扩展到更广泛、更节能的设备中。

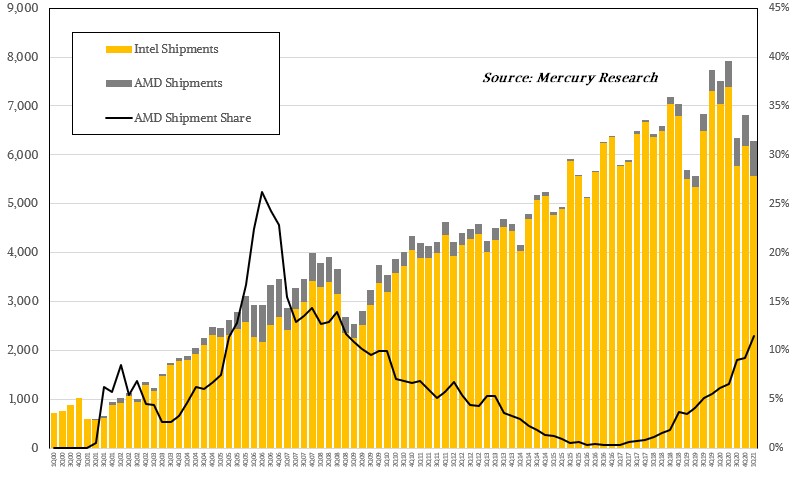

5月初,Mercury Research公布了2021年第一季度的x86 CPU市场份额,AMD在服务器市场获得了自2006年以来最高的单季增长率——2006年第二季度...

随着CPU、GPU等功率密度不断提升,液冷技术在当前有些热门,但这并不意味着风冷就没有创新点了。最近两天看到几台Dell PowerEdge 15G服...

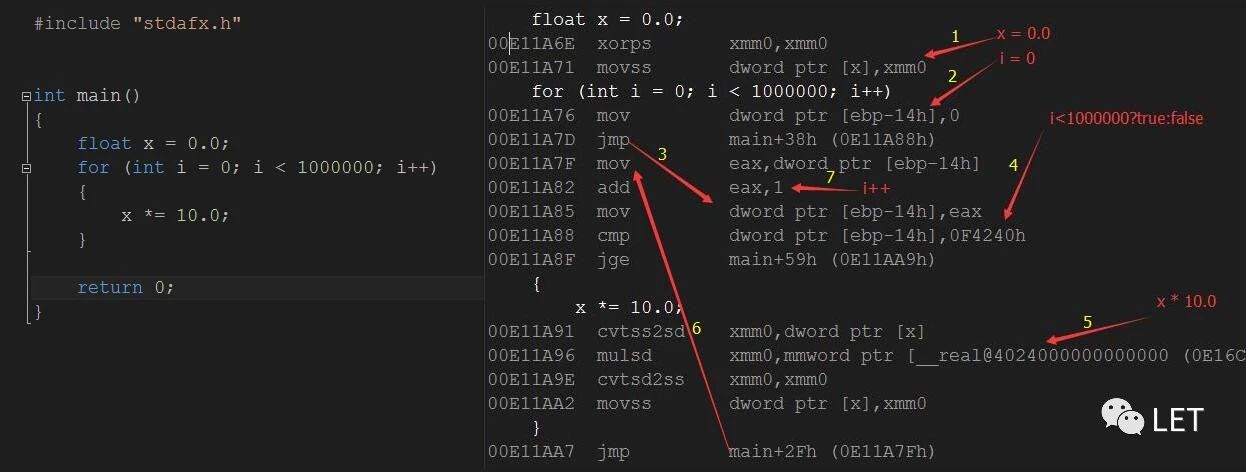

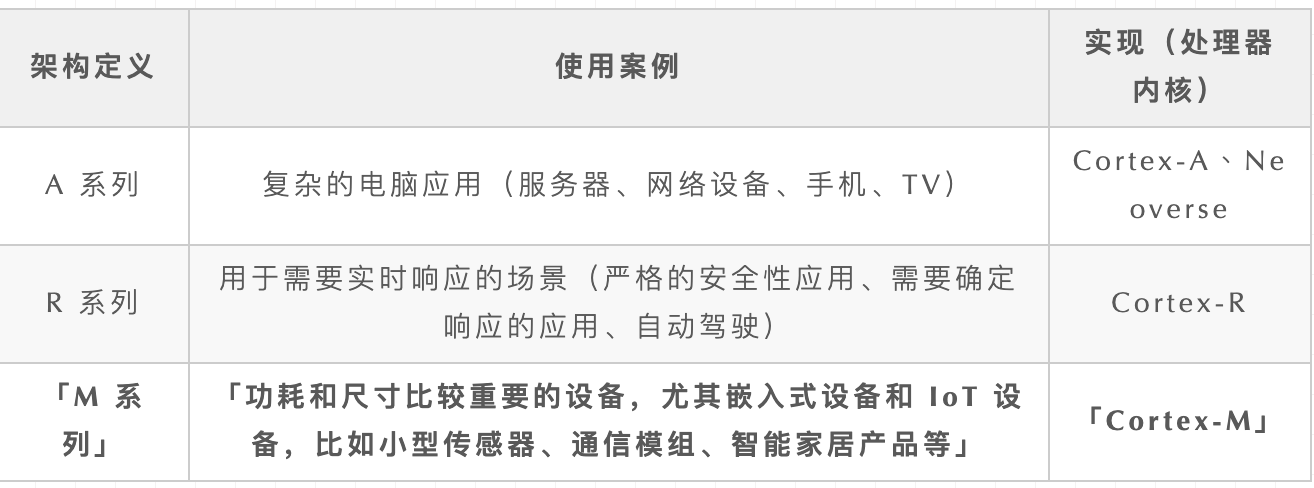

笔者接触嵌入式领域软件开发已近五年,几乎用的都是 ARM Cortex M 内核系列的微控制器。在这五年期间,感谢 C 语言编译器的存在,让我不...

当下国产信息系统建设不断深入,信息系统面临的安全威胁越发严峻,实现系统的安全可信已经成为迫切的现实要求。CPU 作为信息系统的核心...

日前,基于飞腾 CPU 的国内首套自主可控重型燃气轮机控制系统(TCS)在华电浙江龙游电厂成功并网投运,标志着我国重型燃气轮机控制系统...

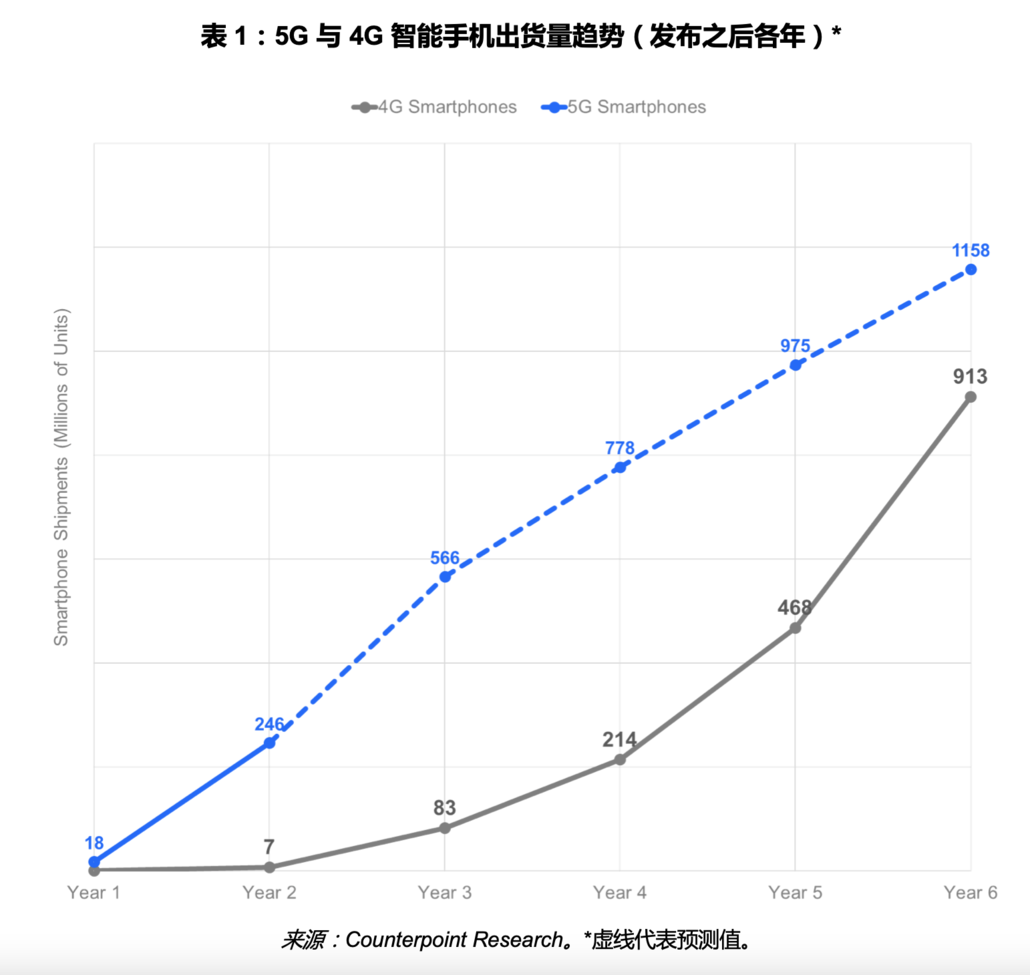

近日,全球成长最快智能手机品牌 realme 与 Counterpoint Research 合作发布了一份题为《5G 全球普及》的白皮书,探讨了全球 5G 智能手...

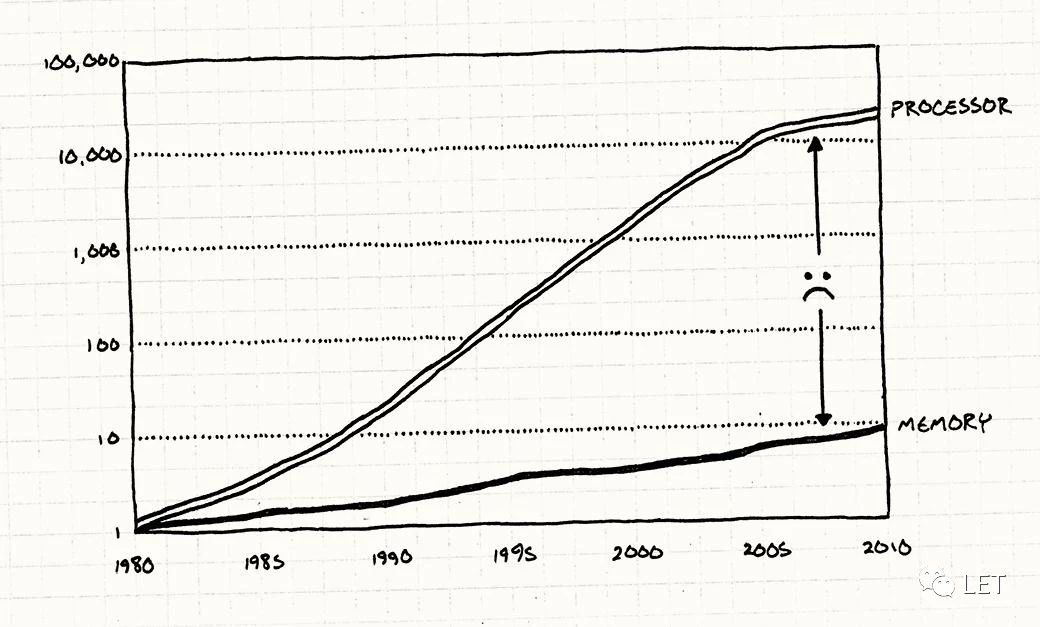

随着工艺的提升,高速缓存的大小虽然不断在增加,但是远远不及主存的容量。众所周知,一旦发生缓存缺失,其代价(penalty)很大,要等待...

这或许是许多人心中的疑问。毕竟在过去的十几年中,服务器领域一直都是数据中心的重点,尤其是在经历了计算升级的大浪淘沙之后,如今通...

根据 Counterpoint 发布的最近数据,2021 年第一季度全球智能手表出货量同比增长 35%。其中,Apple Watch 的市场份额上升了 3%,达 33%。

在前面讲缓存数据放置时讲到,缓存控制器通过地址的高位来做标签(Tag)和索引(Index)判断是否命中。但是我们并没有说这个地址是虚拟...

基于写无效策略的一个弊端在于会造成大量的一致性缺失,每一次读取被无效的块都会遇到缓存缺失,从而导致处理缺失的延迟会很高。